**RKR 01/93**

#### PERIPHERAL DEVICE INTERFACE

#### **DISK LEVEL INTERFACES?**

**HISTORY LESSON No 100001**

#### IN THE BEGINNING

- ONE CONTROLLER THAT HANDLED MANY DISK'S OR SPINDLES PER SYSTEM

- COSTS OF ECC CIRCUITS, BUFFERS, ENDEC'S, WERE AMORTIZED OVER MANY SPINDLES.

- ARRAYS OF DISKS WERE COMMON (FARMS)

- DISKS HAD VERY LITTLE MICROCODE

#### PERIPHERAL DEVICE INTERFACE

#### **DISK LEVEL INTERFACES?**

HISTORY LESSON No 100001-2

#### WHEN WE INHERITED INTELLIGENCE

- SYSTEMS BECAME SMALLER AND ONLY NEEDED ONE OR TWO DISKS

- INTEGRATION TECHNIQUES BECAME VERY COST EFFECTIVE

- IF ONLY ONE DRIVE .... PUT EVERYTHING IN IT...

TAKES COST FROM SYSTEM

- PERFORMANCE WAS QUESTIONABLE .... BUT OVER-RIDDEN BY COST ADVANTAGES

- THE NEED FOR BETTER COMMUNICATIONS BETWEEN SYSTEM AND PERIPHERAL BROUGHT US INTELLIGENT INTERFACES

- DISKS HAVE LARGE MICROCODE PROGRAMS...

DEVELOPMENT COSTS ARE HIGH

#### PERIPHERAL DEVICE INTERFACE

#### **DISK LEVEL INTERFACES?**

HISTORY LESSON No 100001-3

#### NOW WHERE ARE WE

- LARGE CAPACITY SPINDLES.... MANY GBYTES UNDER ONE ARM... MANY SPINDLES TO OBTAIN AVAILABILITY, THROUGH-PUT

- AVAILABILITY OF DATA MORE CRITICAL THAN EVER

- COST IS STILL CRITICAL BUT PERFORMANCE IS REQUIRED

- ACCESSIBILITY TO DATA FOR INCREASED SYSTEM PERFORMANCE

- FAST WIDE SINGLE OPTICAL SYSTEM INTERFACES TO ACCESS PERIPHERALS

- MORE FUNCTIONS.. MORE MICROCODE.. MORE MORE

## **MORE**

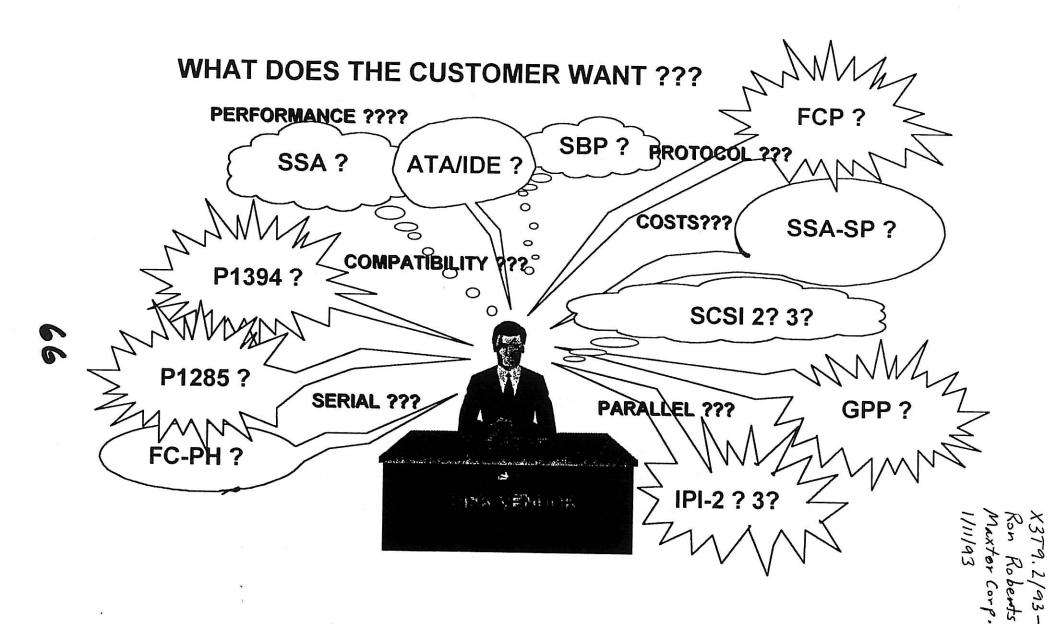

#### PERIPHERAL DEVICE INTERFACE

#### **ANOTHER INTERFACE !!!**

#### **DESIGN GOALS**

- LOW LEVEL ACCESS TO THE MEDIA... IF REQUIRED

- VARIABLE DATA TRANSFER RATES FOR PERFORMANCE VS COST TRADE-OFFS

- ALLOW VENDORS TO TAKE ADVANTAGE OF VOLUME PRODUCTION

- PROVIDE EASY IMPLEMENTATION OF ARRAYS OF DISKS

- PROVIDE SIMPLIFIED COMMAND STRUCTURES AND FLOW

- PROVIDE FOR MAXIMUM THROUGH-PUT

- PROVIDE FOR ERROR FREE TRANSFERS

70

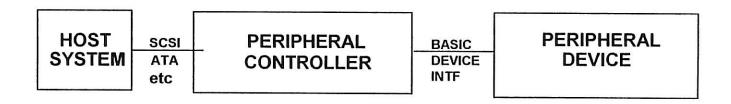

#### PERIPHERAL DEVICE INTERFACE

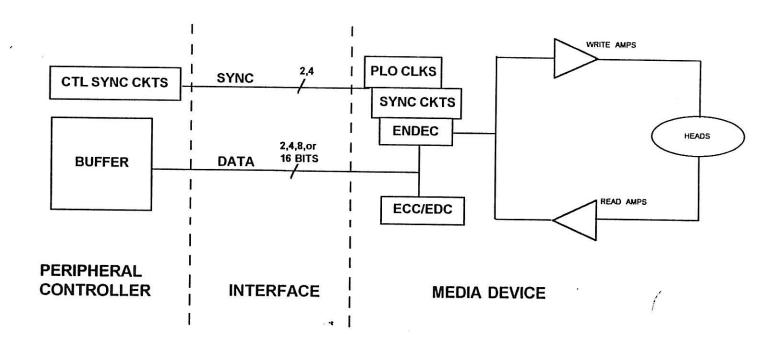

#### ARCHITECTURAL MODEL

SYSTEM ATTACHMENT LEVEL (SCSI, ATA, IPI3, VME, ETC,ETC..)

PERIPHERAL CONTROLLER

BASIC DEVICE LEVEL ATTACHMENT

PERIPHERAL DEVICE

71

#### PERIPHERAL DEVICE INTERFACE

#### ARCHITECTURAL MODEL

#### **ATTRIBUTES OF LEVELS**

| PERIPHERAL CONTROLLER                | PERIPHERAL DEVICE   |

|--------------------------------------|---------------------|

| SYSTEM INTERFACE CONTROLS            | ALL SERVO CONTROLS  |

| CACHE MEMORIES(IF REQUIRED)          | ENCODER DECODER     |

| CONTROLS MULTIPLE DEVICES(NO LIMITS) | READ/WRITE CIRCUITS |

| BUFFER AREAS                         | ECC OF THE FLY      |

| SYSTEM SPECIFIC KNOWLEDGE            | STORAGE MEDIA       |

|                                      | SPINDLE SYNC CKTS   |

|                                      | ALL POWER CONTROLS  |

#### PERIPHERAL DEVICE INTERFACE

#### ADVANTAGES OF INTERCONNECTION SCHEME

- PROVIDES LOW LEVEL ACCESS TO MEDIA (if required)

- SIMPLIFIES PERIPHERAL DEVICE FIRMWARE

- LESS COSTLY PERIPHERAL DEVICES

- EASE OF IMPLEMENTATION FOR ARRAYS OF DISKS (RAID's ??)

- PERIPHERAL GUIDED VS SYSTEM AFTER THOUGHT

- **PERFORMANCE ORIENTED WITH LESS \$ THAN SCSI (PER SYSTEM)**

#### PERIPHERAL DEVICE INTERFACE

#### INFORMATION MOVEMENT PROTOCOL

PERIPHERAL CONTROLLER

PERIPHERAL DEVICE

4 COMMAND WORDS TRANSMITTED

4 COMMAND WORDS RCVD'D

& DECODED

4 STATUS WORDS RCV'D

WAIT FOR INTERRUPT (DO SOMETHING ELSE)

-4 STATUS WORDS TRANSMITTED

PERFORM SPECIFIED COMMAND

4 STATUS WORDS RCV'D

#### PERIPHERAL DEVICE INTERFACE

# WHERE DOES IT FIT ? IN THE HIERARCHY OF THE SUBSYSTEM

TYPICAL PERIPHERAL SUB-SYSTEM

75

### PERIPHERAL DEVICE INTERFACE

#### DATA PATH LAYOUT