## Document X3T9.2/92-199 Revision 2

# SCSI 3 Serial Bus Protocol A Logical I/O Model for SCSI on the 1394 Serial Bus

November 6, 1992

Gerald Marazas Scott Smyers Ed Gardner

Point of Contact:

Gerald A. Marazas IBM Corporation P.O. Box 1328 Boca Raton, Florida 33429 Mail Stop 5432

Phone: (407) 982-4423

Internet: marazas@bcrvmpc2.vnet.ibm.com

#### Secretariat

Computer and Business Equipment Manufacturers Association

Abstract: This document is a proposed working draft of the SCSI 3 Serial Bus Protocol. The purpose of the protocol is to define how SCSI 3 functions are transported over the IEEE 1394 High Speed Serial Bus.

This is an internal working document of X3T9.2, a Task Group of Accredited Standards Committee X3. This is not a completed standard and has not been approved by Task Group X3T9.2. This document is made available for review and comment only.

COPYRIGHT NOTICE: In accordance with the usual ANSI policy on the revision of standards, this draft may be reproduced, for purposes of review and comment only, without further permission, provided this notice is included. All other rights are reserved.

# Contents

\$

\$

| 1.0 Overview 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0 Referenced Standards 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.0 Glossary and Conventions 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| <ul> <li>4.0 Model of Serial Bus Protocol 4</li> <li>4.1 Model of Serial SCSI Initiator 4</li> <li>4.1.1 Setting of the M_Flag 4</li> <li>4.1.2 Focus of a Command Chain 5</li> <li>4.1.3 Composition of a Command Chain 5</li> <li>4.1.4 Retention of a Command Block by the Initiator 5</li> <li>4.1.5 Shoulder Tap Protocol for Command Delivery 6</li> <li>4.2 Model of Serial SCSI Target 6</li> <li>4.2.1 Usage of the Status FIFO 7</li> <li>4.2.2 Usage of the M_Flag 7</li> <li>4.2.3 Management of Target Resources 7</li> </ul> |

| <ul> <li>5.0 Command Transfer Protocol 11</li> <li>5.1 Conceptual Initiator - Target Connection 11</li> <li>5.2 Multiple Initiator Environment 13</li> </ul>                                                                                                                                                                                                                                                                                                                                                                               |

| 6.0 Packet Types 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <ul> <li>7.0 SCSI 3 Serial Bus Protocol Support Elements</li> <li>7.1 Target "Register" Definitions 15</li> <li>7.1.1 Normal FIFO 16</li> <li>7.1.2 Urgent FIFO 16</li> <li>7.2 Initiator "Register" Definitions 16</li> <li>7.2.1 Status FIFO 17</li> </ul>                                                                                                                                                                                                                                                                               |

| <ul> <li>8.0 Command and Status Information</li> <li>8.1 Command Blocks 18</li> <li>8.2 Status Block 23</li> <li>8.3 Initiator Scatter/Gather List 23</li> </ul>                                                                                                                                                                                                                                                                                                                                                                           |

| <ul> <li>9.0 Payload Specification For Command Transfer Packets</li> <li>9.1 Payload of Initiator to Target Packet - "Tap Packet"</li> <li>9.1.1 Request Payload</li> <li>9.1.2 Response Payload</li> <li>9.2 Command Read Request</li> <li>9.2.1 Request Payload</li> <li>9.2.2 Response Payload</li> <li>26</li> <li>9.2.2 Response Payload</li> <li>26</li> </ul>                                                                                                                                                                       |

| <ul> <li>10.0 Data Transfer Protocol 27</li> <li>10.1 Asynchronous Transfer 27</li> <li>10.1.1 Data Read From Device Medium 27</li> <li>10.1.2 Data Written To Device Medium 27</li> </ul>                                                                                                                                                                                                                                                                                                                                                 |

| 11.0 Status Transfer Protocol 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12.0 Examples 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12.1 Target Read Command 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12.2 Target Multiple Read Commands 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13.0 Messages 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 13.1 Payload of Abort Packet 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13.2 Payload of Abort Tag Packet 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 13.3 Payload of Reset Packet 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 13.4 Payload of Clear Queue Packet 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Substitution of the second state of the second state of the second secon |

| 14.0 Contingent Allegiance 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14.1 Aims 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.0 Compatibility to Parallel SCSI 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15.1 Increased Initiator problems 34 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15.1 Increased Initiator problems 34 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <ul><li>15.1 Increased Initiator problems 34 –</li><li>15.2 Asynchronous Event Notification 34</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ul><li>15.1 Increased Initiator problems 34 –</li><li>15.2 Asynchronous Event Notification 34</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15.1 Increased Initiator problems 34 – 15.2 Asynchronous Event Notification 34 15.2.1 Aims 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>15.1 Increased Initiator problems 34 –</li> <li>15.2 Asynchronous Event Notification 34</li> <li>15.2.1 Aims 34</li> <li>Appendix A. Packet Formats 35</li> <li>A.1 Write Packets 35</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ul> <li>15.1 Increased Initiator problems 34 –</li> <li>15.2 Asynchronous Event Notification 34</li> <li>15.2.1 Aims 34</li> <li>Appendix A. Packet Formats 35</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.1 Increased Initiator problems 34 – 15.2 Asynchronous Event Notification 34 15.2.1 Aims 34  Appendix A. Packet Formats 35 A.1 Write Packets 35 A.2 Read Packets 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15.1 Increased Initiator problems 34 – 15.2 Asynchronous Event Notification 34 15.2.1 Aims 34  Appendix A. Packet Formats 35 A.1 Write Packets 35 A.2 Read Packets 36  Appendix B. Isochronous Transfer 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.1 Increased Initiator problems 34 – 15.2 Asynchronous Event Notification 34 15.2.1 Aims 34  Appendix A. Packet Formats 35 A.1 Write Packets 35 A.2 Read Packets 36  Appendix B. Isochronous Transfer 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# **Figures**

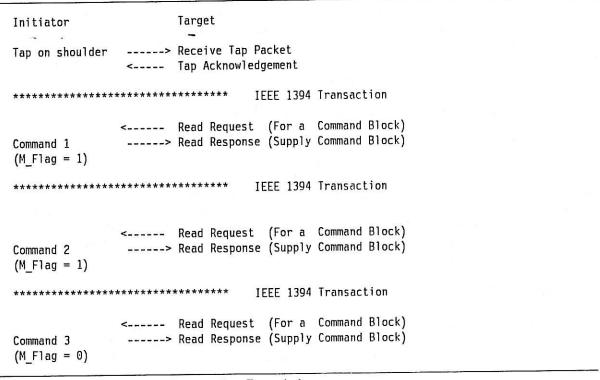

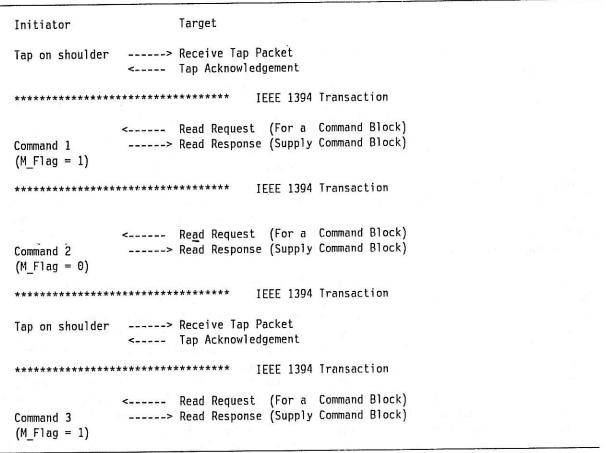

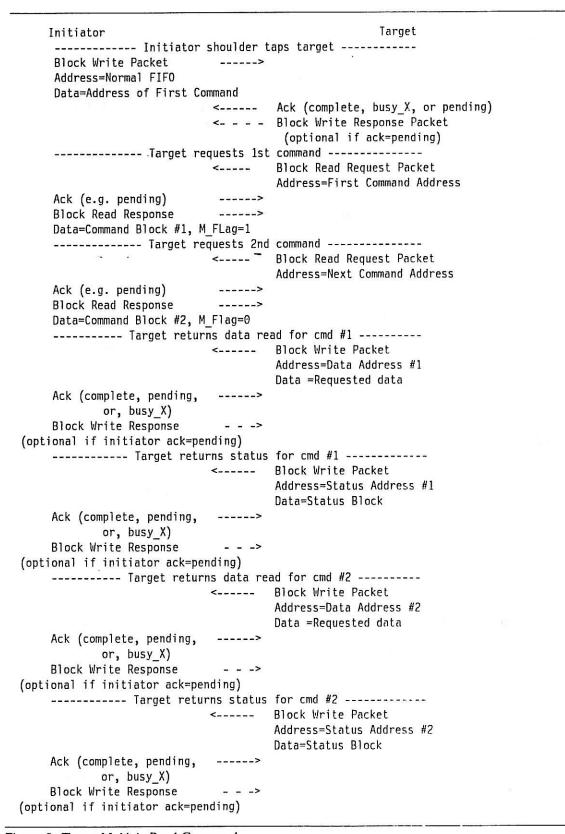

11 Conceptual Initiator-Target Conversation, Example 1 1. 13 2. Conceptual Initiator-Target Conversation, Example 2 3. Command Block 19 Control Flags 4. 5. Status Block 23 Scatter/Gather List Format -- Single 16-Byte Unit 24 6. Payload of Initiator "Tap" packet 7. 8. Target Read Command 30 9. Target Multiple Read Commands Payload of Abort Packet 10. 11. Payload of Abort Tag Packet 32 12. Payload of Reset Packet 13. Payload of Clear Queue Packet 32 14. Quadlet Write Request Packet 15. Block Write Request Packet 35 16. Write Response Packet 17. Read Request Packet 36 18. Read Response Packet 36 19. Block Read Request Packet 36 20. Block Read Response Packet 36 21. Isochronous packet 37 22. Isochronous packet 38

## **Acknowledgements**

The editors wish to express appreciation to the multiple parties who have provided input and/or critique to this document. In particular, the following individuals have made valuable contribution by virtue of their inputs of text and their comments:

Jon Haswell IBM Fujisawa, Japan

Andy McNeill IBM Boca Raton, Florida

Michael Teener Apple Computer Cupertino, California

# Goals and Objectives

This document describes a command and status delivery protocol for controlling the operation of devices attached to an IEEE 1394 Serial Bus physical interface. This protocol is based on a mapping of parallel SCSI commands and messages. Trade offs have been made in function placement so as to provide improvements in performance and subsystem functionality, while allowing Target and Initiator designers to build upon existing parallel SCSI hardware and software.

A major goal motivating this protocol definition was to define a model acceptable to device vendors, looking for an evolution from parallel SCSI, and systems designers looking for opportunities to more fully exploit the capabilities inherent to the IEEE 1394 I/O bus.

The protocol described in this document attempts to solve some of the problems associated with parallel SCSI protocol through provision of additional functional capability such as:

- 1. Ability to queue multiple commands for a Target without concern for arbitrary "queue full" conditions within the Target.

- 2. Target does not need to interrupt processing of a prior command in order to queue a subsequent command.

- 3. Ability to design Target devices that have varying levels of support for command queucing or overlapped command processing without affecting the design of the Initiator. Conversely, the Initiator design can be structured so as to support multiple device and/or command queueing capability.

- 4. Distribute the system DMA context handling (Disconnect, Reconnect, Save Data Pointer, Restore Pointers, etc.) required by parallel SCSI so as to reduce device and adapter overhead for higher subsystem performance. The Target device is given an important role in maintenance of DMA context.

This protocol also attempts to ease the transition to a Scrial SCSI environment by consideration of significant aspects of the Parallel SCSI environment:

- 1. Integrates standard parallel SCSI Command Descriptor Block (CDB) within Serial SCSI Command Block.

- 2. Closely follows standard parallel SCSI command queuing/error recovery procedures and concepts.

- 3. Requires less packet overhead because of command/status list management being performed locally in the Initiator.

In striking a balance between support for existing Parallel SCSI functions, and providing a growth path to exploitation of new features of Serial SCSI environment, a new fixed length command block has been defined. This command block provides support for advanced features of todays SCSI such as automatic sense data reporting and scatter/gather host data buffer handling. Support is provided for interesting new features of the IEEE 1394 High speed Serial Bus such as Isochronous data transfer. The present approach does not require "locked" memory operations for list pointer update/management.

Other aspects of this protocol address the broader elements of operation currently under discussion in the SCSI 3 community.

- 1. Taking into account the command chaining capability of Serial SCSI as well as the SCSI 3 Queueing Model so as to achieve comparable order of command fetching and command execution between Serial SCSI and Parallel SCSI.

- 2. It is desired to maintain some level of commonality for similar functions between SCSI as supported by by the IEEE 1394 transport mechanism and SCSI as supported by Fibre Channel transport.

## 1.0 Overview

The SCSI 3 Serial Bus Protocol has the following features:

- · Fixed length command blocks (See note 1 below)

- · Fixed length status blocks

- · Fair support for multiple Initiators

- · Separate command queues for each Initiator/Target pair

- · Ability to support multiple command queues per Initiator

- Command queue depth determined by Initiator

- · Number of overlapped commands in progress limited by Target

- · Supports parallel SCSI error recovery procedures

- · Supports Isochronous operation

Implementation Note: Target vendors (particularly at the low end) have expressed strong preference for a solution in which every effort is made to reduce the size of the command block. Opportunities should be sought to obtain a smaller command block if this can be done without making unacceptable compromises in functional capability. One accommodation to vendors of low-end Target devices is the organization of the command block into a baseline section which must be fetched under all circumstances and an extended portion for which the option is granted that it may be fetched only when a check condition occurs during execution of the command. It would be anticipated that high-end Target devices would always fetch both the baseline as well as the extended portions of the command block.

# 2.0 Referenced Standards

This Serial Bus Protocol document describes a Logical I/O Model for the physical Transport means provided by the IEEE 1394 High Speed Serial Bus.

For compatibility purposes reference is made to SCSI 2 (X3.131-1992)

# 3.0 Glossary and Conventions

This section is to be provided in a later revision level.

## 4.0 Model of Serial Bus Protocol

This section describes the architectural model for the SCSI Initiator and for the SCSI Target as they interact within the SCSI 3 Serial Bus Protocol.

## 4.1 Model of Serial SCSI Initiator

The Initiator is responsible for building the command blocks, queueing multiple command blocks, allocating status block buffers, and handling the correlation between command blocks and status blocks. It is anticipated that the Initiator may find it beneficial to associate command blocks together into a structure commonly called a command block chain, or more simply a chain. Individual commands within the chain do not need to have any particular connection to one another except that they originate from the same Initiator. One reason for forming commands into a chain is that processing efficiency is enhanced within the Initiator. An additional reason for forming commands into a chain is that there is some relation among the commands as viewed by the Initiator.

Editorial Note: Care should be taken to distinguish between the new facility of commands formed into a chain and the existing facility in SCSI known as the Linked command. With regard to the SCSI 3 Queueing Model, the entire collection of Linked commands are considered as a single I/O Process. The elements within a Linked I/O process must be completed before work may be done on behalf of any other I/O process. In important contrast to this situation for elements of a Linked I/O process, within the command chain, each command is considered a separate and distinct I/O Process. If there are multiple chains, then the Target may interleave its work activity among the chains. Link commands may be used in a chain as can any other SCSI command.

In the SCSI 3 Serial Bus Protocol, command blocks must be queued by the Initiator and the Initiator must be capable of providing the queued command blocks one at a time to the Target whenever the Target is ready to begin processing a new command. This helps to avoid busy conditions where the Target cannot accept any further command blocks. As a supported and encouraged option within the Serial Bus Protocol, Target devices may fetch multiple commands (one at a time) from any Initiator. In this manner (via prefetch), the Target has the optimization option of overlapping certain process steps for a later command while the current command is in execution.

## 4.1.1 Setting of the M\_Flag

The mechanism for forming commands into a chain makes use of the field in the command block which is the address of the next command. Thus, a chain consists of those commands connected to one another by the Initiator through use forward pointer consisting of the next command address field found in each command block. Each command block also contains a flag, called the More\_Flag, or more briefly the M\_FLAG. When the M\_FLAG has value equal to one, it means there is at least one command block in the chain occurring after this present command block. The very last command block in the chain is indicated by having value equal to zero for the M\_FLAG. The Initiator preserves for later use the address of the first command in the chain. It is convenient to refer to the starting address of a command block chain as being the address of the first command block in that chain.

## 4.1.2 Focus of a Command Chain

In conformity to the SCSI 3 queueing model, each chain of command blocks is directed to a specific Logical Unit Number (LUN) of a specific Target. An Initiator is allowed to have multiple command block chains directed to the same Target/LUN combination. An Initiator is also allowed (in fact required) to have a different command block chain for each and every Target/LUN which is to receive commands from that Initiator. Observe that a given Target/LUN combination may also have multiple command block chains directed to it. Each command block chain within an Initiator is distinguished by having a different starting address within that Initiators address space.

# 4.1.3 Composition of a Command Chain

The following four types of I/O process are defined in the SCSI 3 queueing model:

- 1. Simple

- 2. Ordered

- 3. Head of Queue

- 4. Autocontingent Allegiance (ACA)

A chain of command blocks is restricted to contain one and only one type I/O process drawn from the list above. A TYPE\_ID parameter is connected to each chain for the purpose of identifying the nature of commands contained within any given command block chain.

If an Initiator has a sequence of Simple I/O commands which are to be completed before a sequence of one or more Ordered commands, then the Initiator must construct one chain consisting only of the Simple commands and a second chain consisting only of the Ordered commands. The Initiator must first inform the Target of the chain of Simple commands, and second, inform the Target of the chain of Ordered commands. These restriction on contents of a chain and this procedure for informing the Target about chains facilitate processing by the Target which conforms to the completion sequence rules defined in the SCSI 3 Queueing Model.

# 4.1.4 Retention of a Command Block by the Initiator

The Initiator must be aware that the Target may have legitimate need to refetch the same command block at any arbitrary time after the time of original fetch up to the time of return of completion status and/or sense data. One reason for a refetch is that a Target may elect to take advantage of the option in which ending portions of the command block are read only when a check condition occurs. A second instance of refetching a command is the optimization policy in which many command blocks read and then discarded in order to which command is best to execute next so as to achieve best performance. The command selected for execution is then refetched.

Thus, the Initiator must maintain the command block in memory at the same location as originally stated to the Target. The Initiator must assume full consequences for any change in contents of the command block from the time of first fetch of that block until the time of any later fetch. Aborting a command is an example of a situation in which the Initiator may feel it has a proper and good reason for altering some part of a command block after it has been fetched and before return of completion status information.

## 4.1.5 Shoulder Tap Protocol for Command Delivery

As there are potentially multiple initiators in a system, there has to be a method for an Initiator to indicate to a Target that it has some work for that Target. A conceptual "tap on the shoulder" is performed via a SCSI Command Initiation Packet sent to a set of Command FIFOs maintained by the Target. Two members are defined for this set of Command FIFOs. The first member is the Normal FIFO and this is intended for use by command chains. The second member is the Urgent FIFO and this is intended for use by SCSI messages sent to the Target by the Initiator for various control purposes. One set of these two FIFOs shall be provided per Target. This single set is to be shared by all Logical Units connected to the given Target.

Many implementation choices are available as to hardware and/or software means to support the Normal FIFO and the Urgent FIFO data structures. A comparable structure, the Status FIFO, is defined for use within the Initiator in order to receive status information from the Target regarding command completion. Observe, at the conceptual level, the Status FIFO and the Normal FIFO and the Urgent FIFO have many notions in common. A key element common to both the Status FIFO in the Initiator and the set of two FIFOs in the Target is that the same size packet (12 Bytes of payload) is sent to all of them. This is not to say that any requirement exists to provide the same hardware implementation for the Normal FIFO, the Urgent FIFO, and the Status FIFO.

There are always limits as to the number of "Shoulder Taps" which can be accommodated at any one time by a Target. The Initiator must be prepared to accept a response from a Target which states the present Tap cannot be accepted. Various software means may be employed by the Initiator to deal with this situation that a Target is temporarily not able to accept a Tap. Various elements of the Command Delivery architecture of the Serial Bus Protocol operate so as to make it an unusual and infrequent circumstance that a given Tap cannot be accepted.

After the Target has received this "Tap", it will read command blocks, one at a time, using a Read Transaction as defined by the Transaction Layer architecture of the IEEE 1394 standard. The Request portion of the Read Transaction makes use of IEEE 1394 style address of the command block. For the first command, the needed command block address is supplied via the SCSI Command Initiation Packet. For second and following commands within a chain, the address for the next command is contained as a field within the present command block.

## 4.2 Model of Serial SCSI Target

The Target is responsible for fetching command blocks, one at a time from the various Initiators having indicated to it there is work to be performed on their behalf. Upon completion of any given command, the Target returns completion status information back to the appropriate Initiator. The addressing scheme of IEEE 1394 is sufficiently flexible that specification can be made for the Target to return Status information to a different Initiator than originated the command block.

Since a given Initiator may have multiple commands fetched by a Target and not yet completed, the Target must provide correlation information between command blocks and status blocks. The address of the associated command block shall be placed in the status block in order to provide this needed correlation.

Conceptually, there is a one to one relation between Sense Data blocks and Command blocks. Also, there is also a one to one conceptual relation between a Status block and its associated Command block. Sense Data blocks are most often written by the Target to general purpose memory within the Initiator address space. Status blocks may be written by the Target to special purpose hardware provided in support of the Status FIFO. While a Sense Data block may not be written for each and every command completing with "good status", there is the notion of allocating a Sense Data block area for each and every command.

- \$ Editorial Note: Based upon discussion within the SCSI Committee, it was determined to be necessary to maintain full generality in the specification of starting address for the Sense Data buffer within the

- \$ maintain full generality in the specification of starting address for the Sense Data buffer within \$ Initiator. As a result, the Sense Data buffer start location is specified by means of a full 64-bit

- \$ address. The notion of a Sense Data Buffer Offset has been removed from this document.

# 4.2.1 Usage of the Status FIFO

For purposes of this Serial Bus Protocol, status information is sent by the Target to a Status FIFO within Initiator address space. Many implementation choices are available as to hardware and/or software means to support the Status FIFO data structure. Observe, at the conceptual level, the Status FIFO and the Command FIFO have many notions in common. A key element common to both the Status FIFO in the Initiator and the Command FIFO in the Target is that the same size packet (12 Bytes of payload) is sent to both. This is not to say that any requirement exists to provide the same hardware implementation for the Command FIFO and the Status FIFO. However, if specialized hardware support is provided for each FIFO it can involve the same hardware design. One useful result of the same hardware treatment for each FIFO is that it becomes more convenient for an Initiator with its Status FIFO to use the same equipment as a Command FIFO and thereby be able (at the hardware level) to also function as a Target.

# 4.2.2 Usage of the M\_Flag