X3T10/94- r 1.1 January 26, 1995 12:37 am

# Proposal for ATA-3 Features

ATA-3 & ATAPI

Devon Worrell January 26, 1995

#### 1.0 Introduction

### 1.1 Purpose

The purpose of this document is to describe a proposal from Western Digital. This proposal will add functionality to the ATA-3 Specifications.

The issue is that more people in the world are now aware that more is to be gained by enhancing ATA than by promoting SCSI into the volume PC space. The obvious opportunity is to overlap the ATA channel, i.e. send one command per device. The motivation for overlapped ATA is multi-tasking OS. The next obvious opportunity is to add queuing, i.e. more than one command per device. This would allow for the DMA channels be multi-threaded.

We must realize that the existing single threaded dual channel DMA, single threaded dual channel ATA solution hasn't shipped and we need to get market focus behind it....not focus all the interest on something that isn't available...ie. SWAT...Sell What is Available Today. The multi-threaded thing is at best a 2H95 product, more likely a 1H96 product.

### 1.2 Scope

This document will cover the key architectural points and other design issues. It is intended that this document be the basis for industry discussion.

#### 1.3 Audience

This document is intended for use by Western Digital Engineers and Managers and attendees of ATA and SFF.

#### 1.4 Technical Terms

There are a number of technical terms being used today to describe the capabilities this document proposes be added to the ATA interface. This of course is natural (Given that Marketing is involved), but could cause confusion when reading this proposal.

Multi-thread, Multi-threaded, Multi-threading

This must be the most misused term used today. It is used to describe everything from operating systems to lines at the bank. For the purposes of this document this term will be used to describe a very general capability of the ATA interface only. When used to describe the ATA Interface then it will mean that the interface can be used to transmit new commands to device(s) on the cable before the completion of any previous (pre-existing) command(s). This term will NOT be used to describe any capability of the Host or Devices attached to the ATA Cable.

Single Thread, Threaded or Threading

This will be used to describe the opposite of Multi-thread and will be used to describe a general capability of the ATA Interface only.

Overlapped, Overlapping

This will be used to describe a capability of Device(s) attached to the ATA Cable.

Arbitration

When used within the context of this proposal, this will refer to the sharing of common signals or other resources (Registers)used

ATA-3 Proposal

in conjunction with the ATA interface, Host computers or Devices using the ATA interface.

Simply put, allowing more than one command at a time to be ac-

cepted by the ATA Device.

Tagging No not showing the world that you exist. This is synonymous with

Command Queuing and is used interchangeably.

Controller The electronics on a peripheral, that provides the ATA functional-

ity

IDE Integrated Drive Electronics. The industry knows the AT Attach-

ment (ATA) interface by this name. ATA, ATA-2 and ATA-3 are used by the Standards bodies as a pseudonym for the ubiquitous

IDE Interface.

Semaphore Used in the context of this proposal, a semaphore is any mecha-

nism that is used to lock access to a common resource.

Task File, Task File Registers

This refers to the Registers that are used to control an ATA device.

For the purposes of this proposal only those registers and signals that can be altered by either the Host or the Device are considered part of the Task File Registers. e.g. BSY, DRDY, DREQ etc. are

NOT considered part of the Task File.

Control Block Same as Task File Registers.

Post That part of the Power-up or initialization sequence that is used to

setup the hardware characteristics. Normally this operation is per-

formed by the System BIOS (for x86 based systems.)

Simple Queued Commands is the capability in the Device to accept multiple commands. Each of these commands can then be re-

ordered by the device. The device has complete freedom to reorder

the queued commands.

Command Queuing

#### 2.0 Goals

It is the intent of this proposal to provide some basic improvements to ATA. The most basic improvement will be to allow commands to be sent to each of the two devices on one ATA Cable, independently. That is allowing commands to be processed in both devices at the same time. A further improvement will be to allow multiple commands to be sent to each of the devices on the ATA Cable. Although this may seem simple, the compatibility issues are extremely complicated.

#### 2.1 Generic Goals

Keep it as simple as possible.

Allow Commands to be sent to each Device on the ATA cable independently.

Allow mixing of Legacy Devices and Newer capability Devices and still use the new capabilities.

Use DMA and independent commands as basis for greatest performance improvement.

Reduce the number of Interrupts to further improve performance.

Report Capabilities and Default to Legacy Mode.

Enable Capabilities that are backward compatible in Post, using Set Features.

Enable Capabilities that are not backward compatible on a command by command basis.

Single solution for ATA and ATAPI peripherals.

Use only the existing task file register space

Maintain compatibility with current silicon.

Support both PIO and DMA modes.

Support existing PCI Bus Master DMA

Support transfers of more than 512 bytes on any given DRQ Interrupt.

Allow error reporting after transfer on reads.

Allow for a minimum queue depth of 64.

Allow the drive to release the Task File Registers before command completion.

Support only simple queued commands.

Minimize Host polling requirements.

### 2.2 Other Possible Areas for Improvement

There are some other areas that should be investigated for ATA-3:

One Interrupt for both Primary and Secondary Channels.

Parity on Data Transfers.

Reduced Command Set.

3.3v Interface.

Note that this proposal goes no further than to point out the need for the above features.

### 3.0 Marketing considerations

Some would say that all these changes are not needed, after all there is the SCSI interface. Some would also say that these changes are producing an ATA-3 interface that is no different in complexity from SCSI.

We all should realize the mistakes were made with SCSI. You must also realize that ATA runs to a different model. We would not use the comparison Simple versus Complex, instead we would use: More Control and Cheap versus Less Control and not so Cheap. Clearly ATA has always been and always will be much closer to an implementable standard due to it being a register based interface, whereas SCSI is a protocol based interface.

### 3.1 History

If you take a step back, you will realize that any interface is comprised of only four elements:

Physical:

Connectors, Jumpers, Form Factor

Electrical:

Signals, Voltages, Timings

Protocol:

Sequence, Bits, Registers

Commands:

Operations

If you apply this model against the 10 years since the original PC/AT hard disk controller shipped and then transitioned to ATA, you will see that progress had occurred where the PC market needed it to.

### 3.1.1 Physical

ATA has 3 physical interfaces:

- 3.5": 40 pin I/O connector, 4 pin power

- 2.5": 44 pin I/O that has 40 pins of I/O and 4 of power

- 1.8": 68 pin PCMCIA

#### 3.1.2 Electrical

ATA has had a relatively constant electrical interface with the following areas of growth:

- PDIAG-/DASP to address compatibility during transition from controller/ST-506 drives to ATA drives.

- DMARO and DMACK to support DMA transfers.

- Faster PIO Data Register Timing.

Mode 0: 600 ns per word - 3.33 Mbyte/sec.

Mode 1: 383 ns per word - 5.22 Mbyte/sec.

Mode 2: 240 ns per word - 8.33 Mbyte/sec.

Mode 3: 180 ns per word - 11.1 Mbyte/sec.

Mode 4: 120 ns per word - 16.66 Mbyte/sec.

· Faster Multiword DMA Data Register Timing.

Mode 0: 480 ns per word: 4.16 Mbyte/sec.

Mode 1: 150 ns per word: 13.33 Mbyte/sec.

Mode 2: 120 ns per word: 16.66 Mbyte/sec.

CSEL to ease installation and eliminate jumpers

#### 3.1.3 Protocol

Until ATAPI, ATA has only added more advanced data transfer protocols and had relied upon the Command Register write, BSY bit, DRQ bit, and IRQ protocol for almost everything:

- Multi-sector PIO Read/Write.

- DMA Read/Write.

- Packet Interface. (ATAPI)

#### 3.1.4 Command Set

Since the AT controller first shipped in 1984, command functionality has been added in the areas of:

- IDENTIFY to report capabilities.

- SET FEATURES to enable advanced capabilities.

- Multi-Sector PIO Read/Write.

- DMA Read/Write.

- Power management.

- Download microcode.

- Removability.

- Packet Interface. (ATAPI)

- CD-ROM command sets.

- Tape command sets.

#### 3.2 Issues with SCSI

The major issues with SCSI within the PC market were:

- No effort was made to standardize the hardware registers used to integrate it into the PC. What the PC OEMs want are standard register sets, standard command sets, and embedded operating system support. This forced either:

- Vendor supplied drivers, or

- Layered device driver model with vendor supplied hardware driver (aka mini-port)

- A command set that was too complex and subject to too much interpretation.

- A protocol that was too complex for single-user machines.

- · A cost point that was/is too high.

It should come as no surprise that the industry is trying to take the ATA cost benefits and extend the capabilities. The beauty of ATA is that it defines a register set, a protocol, a command set, an electrical interface, and a physical interface all within one document. PCI Bus Master DMA is obvious, as is moving from the domain of a single threaded channel to a multi-threaded channel to a queuing device.

### 3.3 Model for enhancing ATA

The obvious model is:

- Power up to Legacy/Compatibility mode.

- Report advanced capabilities via Identify Drive.

- Have the OS driver enable the advanced capabilities via Set Features command or use arguments to individual enhanced capability commands.

- Have the OS driver communicate with the ATA device via the advanced capabilities protocol/commands.

### 3.3.1 Timing Control

We all must admit that none of us like the BIOS controlled local bus ATA hardware, but a standard register set would have been impossible due to these devices running at different clock frequencies and the requirement that they be programmed to support fixed Mode 0/1/2/3/4 PIO ATA timings. Fortunately, the PCI DMA model is 100% register standard, thus this will be easier for all.

#### 3.4 ATAPI Disk

As long as ATA retains a single register set, it makes embedded OS integration much easier. With the advent of ATAPI compliant ATA CD-ROM, ATAPI compliant ATA Tape, and ATA compliant ATA disk, it seems natural for the following to occur:

- Definition of ATAPI compliant ATA disk

- Move ATA support into the layered device driver model, with ATA/ATAPI handled via a mini-port. This allows the OS

to support Disk, Tape, and CD-ROM via a single TSD for SCSI or ATA.

### 3.5 Focus for this Proposal

Western Digital's impression is that PCI has killed VL. Intel worked to get SFF to accept a PCI Bus Master DMA ATA register level specification. The goal is a common register set in order to facilitate embedded operating system (i.e. MS) support. Why? If \$200 CPU uses 10% of bandwidth for ATA PIO data transfer, then this cost is \$20. Multimedia performance is shown to be directly related to amount of CPU bandwidth that can be allocated to it. DMA frees the CPU to do multimedia better.

PCI chipsets today are high pin-count, thus the die sizes are pad limited. This gives them lots of logic to work with as long as the function doesn't add pins. Lets just say that Intel is setting the PCI chipset feature bar and that their 486 and Pentium PCI chipsets have embedded EIDE in the CPU to PCI bridge. The design multiplexes PCI and ATA onto the same pins, thus it costs no pins, and uses up the excess die size...it is free! Unfortunately, SCSI can't be done the same way (i.e more gates, more pins) and I don't see it ever getting integrated into the chipset for this reason and the reason of embedded software support (i.e. Chicken/Egg situation... chipset vendor would want embedded OS support. Which means they would have to license architecture/design from existing SCSI LSI supplier. The Intel Pentium chipset includes the PCI Bus Master DMA ATA capability.

Additionally, the world is trying to add ATA capabilities to issue one I/O per ATA device, not one I/O per ATA channel. The key issues have to do with philosophy (some now, some later versus all later) and where to arbitrate (host hardware/software versus peripheral side) for control of the ATA task file, the ATA IRQ and the ATA DMARQ/DMACK. This topic has started within a working group of ATA (ATA-3). Basically there is a WD proposal that takes a phased approach and has host arbitration and a Quantum/Conner approach which takes a Big Bang approach and has peripheral arbitration.

Some basic points to remember:

- ATA is getting more capable and staying cheap.

- SCSI has become cheaper and easier, but it isn't going to get anywhere near as cheap as ATA since it isn't in the

chipsets.

- ATAPI CD-ROM is now 2X and 4X. There are requests for ATAPI HDCD, ATAPI CD-R, and ATAPI changer specs.

- · ATAPI Tape is now starting to happen.

- The future direction for high speed ATA data transfer is DMA. PIO transfers will become a thing of the past. ATA will only be increasing the data transfer rates when using DMA in the future.

- A push is starting for Overlapped Commands and Queued Commands.

- PCI Bus Master ATA is starting to happen (one command/channel). This same capability can be leveraged by simple Driver modifications to support interleaving of data transfers from each device on the cable.

#### 4.0 Overview

Rather than delve into the complexities of this proposal, a general overview of the Reasons, Concepts and Specific Proposals is discussed in this section.

### 4.1 Key Points and General Approach

Phase in the Changes. Although the changes to the interface should be phased in, the actual definition of them shall occur before any implementations are attempted.

Start in 1995.

More advanced capabilities in 1996.

Provide solutions for the Customers of ANSI and SFF.

Host Silicon providers (e.g. Intel PCI and Bus Master DMA).

BIOS (e.g. Phoenix).

Drivers (e.g. Microsoft, IBM, Apple).

System Vendors.

- Focus on Overlapped operation.

- Allow but de-emphasize more advanced Server and Array capabilities.

- Obtain OS and Hardware solutions in a timely manner.

Support in Win 95 Release 2.

Support in the PC'95 and/or PC'96 Hardware Design Guide.

### 4.2 Assumptions / Constraints used in the generation of this proposal

- Don't alter the key value that ATA currently has (Cost, Performance, True Register Set Standard).

- Phase in the improvements.

- Allow first implementations without any hardware changes.

- Always be backward compatible.

- ATAPI & ATA Features should be implemented identically where possible.

- Improve Performance only where complexity and cost are not increased.

- Overlapped operations will be mainstream, Queuing will not be within the 1995-96 timeframe.

- Reducing number of host interrupts will be beneficial.

- System suppliers, Motherboard manufacturers, BIOS and OS suppliers will decide what is acceptable and what is not.

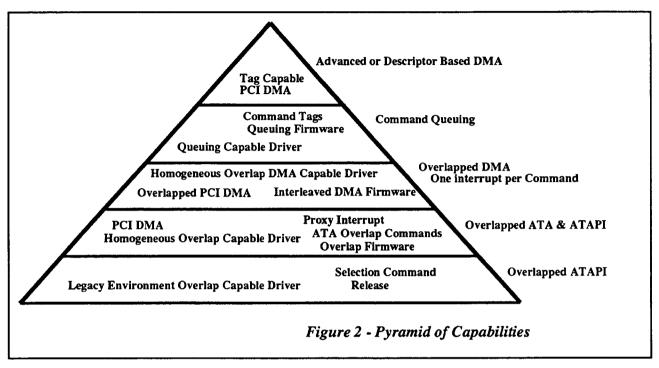

#### 4.3 Phased approach

The proposed features should be phased in over one to two years. There are five distinct capabilities. Each of these can be used when all of the previous capabilities are implemented.

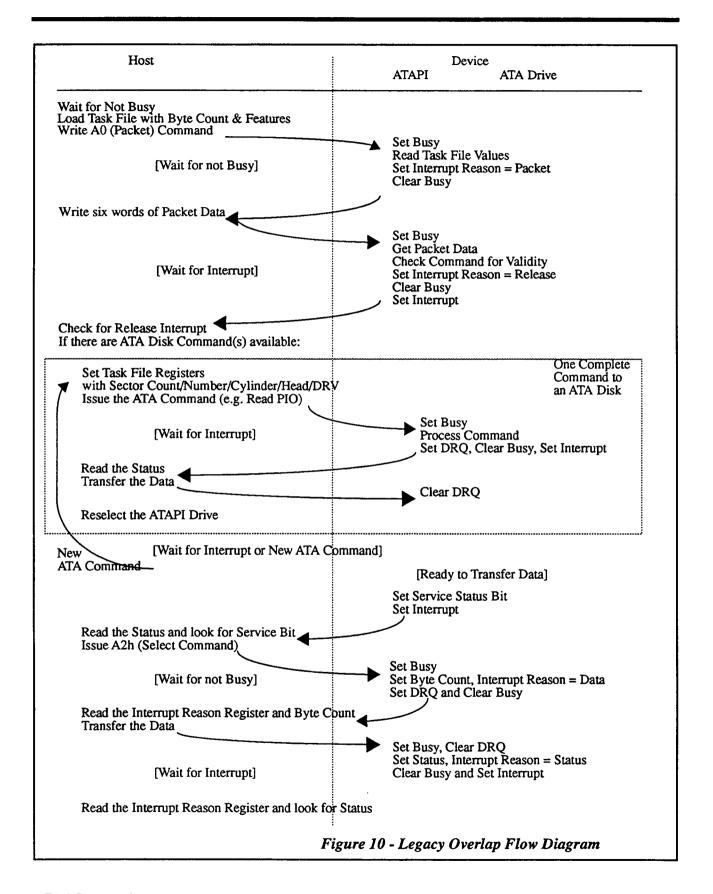

Overlap in a mixed legacy and overlap capable environment (Legacy Overlap).

Allow CD-ROM and Tape Drives to release the Task File Registers and commands to be sent to legacy device (e.g. the faster ATA Disk Drives).

Overlap in a homogeneous overlapping environment (Homogeneous Overlap). Note that the only distinction between

the mixed mode and homogeneous environment is that the Driver must control the overlap for the Legacy Devices, the

Overlap capability will be implemented only one way. There will be the possibility for the Overlap capable Device to

be either Microprocessor driven or Accelerated.

Add Overlapped command capability to all the devices.

Add Proxy Interrupt support.

Use existing PIO and DMA.

- New Overlapped PCI DMA Capability (Reduced Host Interrupts).

- Allow each Drive on the ATA cable to use the DMA Controller without any Host (Driver) intervention.

- Command Queuing and Tagging.

- Multiple commands for each Drive on the ATA cable.

- Advanced DMA for Servers and Arrays.

- Allow Tag information to be processed by the DMA Controller.

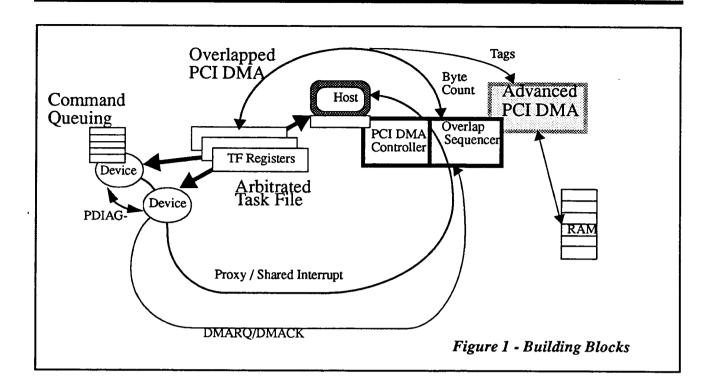

### 4.4 Basic Building Blocks

- · Arbitration of the Task File Registers.

- Release of Task File Registers. A new wrinkle in the protocol will allow the peripherals to clear

the BSY signal before the completion of the command, thus allowing the registers to be used for

sending command(s) to another device.

- Selection Command (A2h). This allows the registers to be given back to the Device when needed.

- Arbitration of Interrupt Request (INTRQ) line.

- · Proxy Interrupt.

- · Service Status bit for detecting who interrupted.

- Arbitration of DMA Control (DMARQ, DMACK) signals.

- Overlapped DMA uses INTRQ to signal ready to transfer of data just like the PIO protocol.

- Overlap PCI DMA Bridge Logic reads & writes Task File Registers directly.

- Interlock function in PCI DMA Bridge Logic controls access to ATA Registers.

- Overlap Capable PCI DMA Drive.

- DMA Ready Status.

- Command Queuing

- Communication of Tags (ATA Feature Register / ATAPI Tag Register.)

- Advanced or Descriptor Based PCI DMA.

- Pointer to memory block used to select DMA control information for each Tagged command.

### 4.5 Capabilities

ATA-3 Proposal

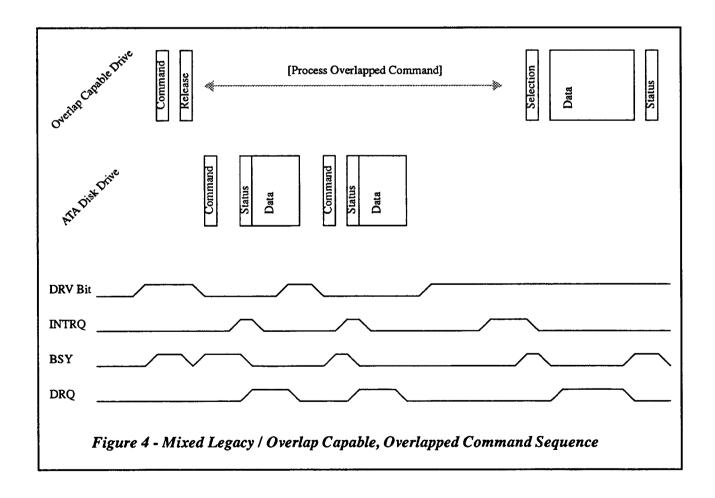

### 4.5.1 Mixed Legacy Environment Overlap

- Allows a CD-ROM Drive to be attached to Primary Cable with no Performance Penalty.

- Uses existing Host & Drive (ATAPI) Hardware (No hardware changes needed.)

- ATAPI Drive Releases the Task File Ownership after acceptance of an ATAPI command.

- Overlap Mode is enabled on each command via the ATAPI Features Register.

- Overlapped Commands are issued to an ATA (Legacy) Drive while an ATAPI Command is still processing.

- Interrupts are generated from the selected device only. Thus the Driver must always select the Overlap capable device when there is no active command to a Legacy Device.

- Device uses Interrupt & SERVICE Status to gain Host's attention.

- SERVICE Status set when any service is needed by the Device.

- Driver uses the A2h (Select) Command to give control of the Task File Registers back to the Device after an Interrupt and Sensing the SERVICE status bit.

- The Interrupt Reason RELEASE Status bit is used to indicate a Release Interrupt.

- · Use existing PCI DMA.

- When DMA used, the Drive Interrupts when DMA is complete, only when there is still more data to be transferred (That command still has more data to transfer).

- When DMA used, Host (Driver) uses Byte Count from the Selection Command (A2h) results, to program the DMA Controller.

ATA-3 Proposal

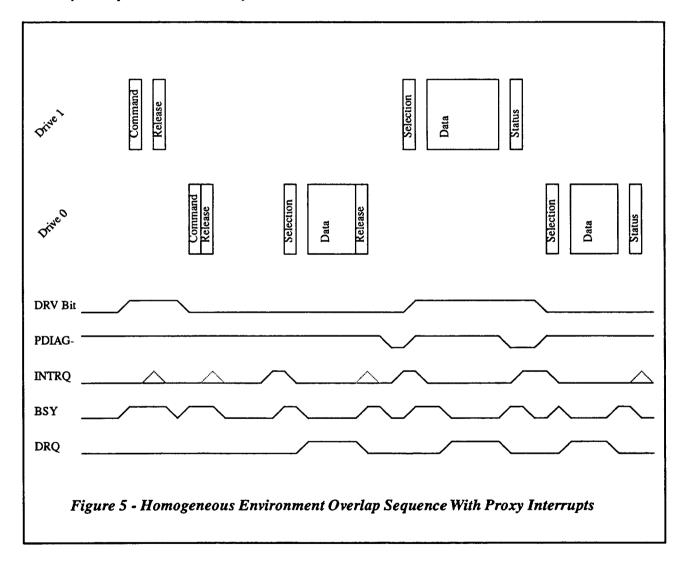

### 4.5.2 Homogeneous Overlap

- Two new ATA commands for Read and Write Overlapped or Queued.

- DMA or PIO specified in the ATA Feature Register.

- Device Releases Task File after acceptance of an Overlapped command.

- Task File arbitration performed by the Host (Driver).

- Proxy Interrupts used to signal Service to Host.

- Device prevents interrupts while BSY or DRQ is set.

- Both Devices on the Cable must support the Proxy Interrupt for it to be used.

- · Limited Overlap can still be used without Proxy Interrupts.

- Proxy Interrupt function is enabled by the Driver via the SET FEATURES Command.

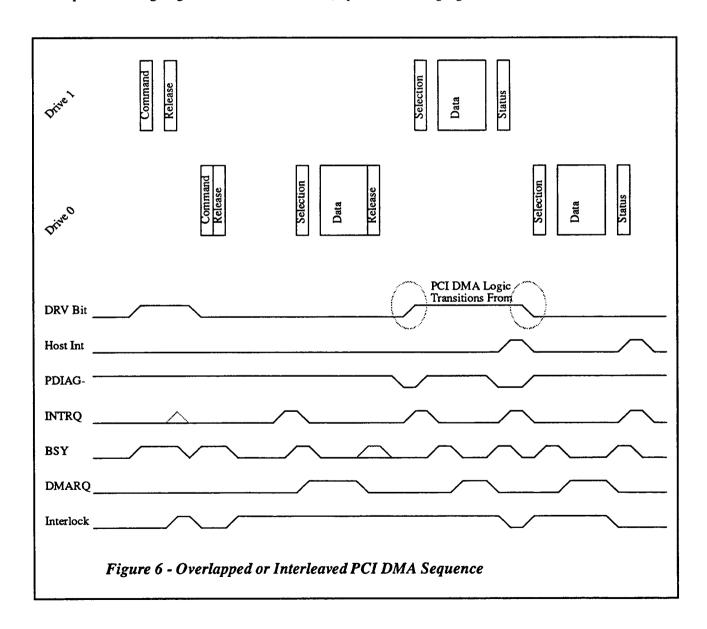

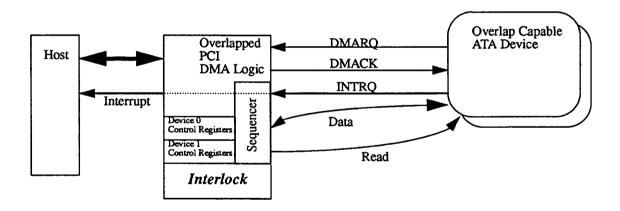

### 4.5.3 PCI DMA Overlap Capability

- Intercepts the Interrupt from the ATA/ATAPI Device.

- New Status bit in the ATA Status Register to indicate DMA ready.

- Sequencer selects each Drive, senses DMA Ready & Service status bits.

- Arbitrates and Selects a Drive by issuing A2 command.

- Uses an Interlock to prevent Host (Driver) and Sequencer collisions.

- Blocks Interrupts while processing INTRQ or DMA transfers.

- Interrupts Host for unknown interrupt reasons.

- Host (Driver) Performs same function on systems that do not have the Hardware support for the PCI DMA Overlap.

- No change in the existing Drive DMA or DMARQ/DMACK logic.

- Bridge logic must include control registers for each of the two devices.

- Sequencer in bridge logic reads the Task File Status, Byte Count and Tag registers.

### 4.5.4 Command Queuing

- · Tags are used to identify each command

- ATAPI uses the Tag register to communicate the Tag To and From the Device

- ATA Drives use the ATA Feature Register to send the Tag on a command, then use the ATAPI Tag register when asking

for service.

- For Both ATAPI and ATA the Tag is placed in the ATAPI Tag register after the A2h Command is issued.

- Simple Queue Tags only are implemented.

- Errors abort all commands in the Queue.

- The Overlap Capable PCI Bus Master DMA logic should read the Tag Register after the SELECT Command has been issued and if the Tag is not the same as the previous, then Interrupt the Host for processing. This should be the basic functionality, even if command queuing is not supported by the PCI DMA Logic.

### 4.5.5 Advanced or Descriptor Based DMA

- Layered on Overlapped PCI DMA & Homogeneous Overlap capability.

- Advanced DMA Controller reads Tag from Task File.

- Uses a memory block with one DMA Control entry for each Tag and Device.

410

### 5.0 Paths

Although what has been discussed thus far are the goals, they will not be implemented all at once. The goals will be met in groups. These groups represent a phased implementation approach, with less complicated but most beneficial features implemented first. Other more complicated features or those features that require host hardware modification will be phased in over a longer time frame.

Although some features will be phased in, the actual definitions for all the enhanced functions will be standardized at the same time.

A real issue is silicon development cycles, with drive vendors wanting to get this worked out soon as there are new chips on the operating table and we need closure.

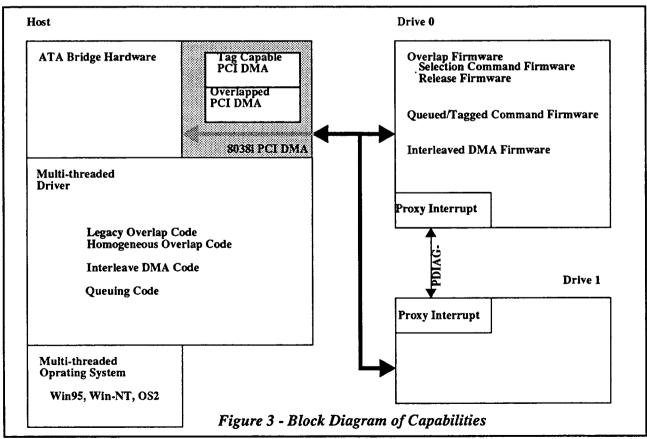

### 5.1 Phase 1: Mixed Legacy Overlap Environment

These are the first improvements that will be implemented. They do not require any hardware changes to the Host or the Overlap Device. This capability will be the foundation for all the other overlap and Queuing capabilities. This phase will allow the OEMs to place one ATA Hard Drive and one ATAPI CDROM on a single ATA Cable, thus reducing the overall cost of the system by at least \$0.50 or more.

One Fast Device and one slower (ATAPI) Device on one ATA Cable.

Doesn't require host LSI changes.

The Host (Driver) arbitrates the DMA hardware usage by the ATA & ATAPI Drives.

Requires OS Driver changes.

Requires minor ATAPI Device Firmware changes.

Only the ATAPI Device needs to be capable of the Overlap function.

# 5.2 Phase 2: Homogeneous Overlap Environment & Reduced Host Interrupts for DMA

This is where most of the performance improvements will be created. This phase supports both ATA Disk drives and ATAPI CDROM/Tape. The capabilities added here will form the foundation for Command Queuing and more advanced DMA capabilities. During this phase there will be some skewing in the use of Host Silicon and Devices that can implement the overlap capabilities. Although the full improvement in performance will not be obtained when this occurs, some improvement is still expected.

Mixing of Legacy and Overlap Capable Devices possible.

Mixing of Non-enhanced Hosts and Enhanced Drives keeps most of the performance gains.

Doesn't require host LSI changes when using existing PCI DMA or PIO.

Reduced Host Interrupts requires new PCI DMA Bridge logic.

The Host arbitrates the DMA hardware usage by the ATA and ATAPI Devices.

Requires the use of Proxy Interrupts in the Devices.

Requires OS Driver changes (Should have already been done in the first phase.)

Requires minor ATA Drive Firmware changes (ATAPI Drive changes occurred in phase one.)

#### 5.3 Phase 3: Command Queuing

In this last phase, Queuing of commands in the Faster ATA Disks is implemented. In addition, optional PCI DMA bridge logic could be implemented that will allow the Queued commands to be processed out of order without interrupting the Host Driver when the Tag changes.

All Drives must be Shared Interrupt capable, no mixing allowed.

Optional DMA channel handles Tag and Drive changes automatically (No Driver intervention).

Requires Host LSI changes if Automated DMA is used.

Requires OS driver changes. Requires Drive Firmware changes.

### 5.4 OS Improvements

Although not part of any of the above "Phases" the Operating System and its drivers are an integral part of any performance improvements that can be achieved. Once the definition for the Overlap capabilities is complete the next releases should implement ALL the new capabilities. There are a number of areas that Western Digital believes are important for the Operating Systems to consider:

- · Get rid of the monolithic ATA disk/CD-ROM driver and move fully to the NT like layered I/O model.

- · Support disk, CD-ROM, and tape TSDs.

- · Rename SCSI Manager and call it I/O Manager.

- · Run ATA and ATAPI hardware via mini-ports.

- Allow the ASPI interface to communicate with the ATA and ATAPI mini-ports so that CDHD, CR-R, and CD changer can be supported by 3rd party applications.

- Support PCI Bus Master DMA.

- Support for Overlapped ATA channel.

- Support for Command Queuing.

### 6.0 Key Issues

Before launching into technical discussion of various solutions, it is necessary to provide a foundation of understanding for the reader. This can be thought of as a list of problems, but even more than that, a tutorial.

#### 6.1 Tutorial and Problem Definition

The ATA interface of today has evolved from the simple Winchester controllers, where there was only one set of registers and up to two ST506 or ESDI drives. In this environment there was only one controller for the peripherals and as such the interface was created as "Single Threaded."

Here we find the first of the problem areas for enhancing the interface to provide some level of "Multi-threading" capabilities. ATA controllers use a protocol to talk with the host, that provides a simple semaphore for locking access to the ATA Interface Control Registers (Task File). This is made up of the Busy (BSY) signal and the Data Request (DRQ) signals. These signals are used to control "Ownership" of some of the Task File Registers. When either BSY or DRQ is set only the peripheral (that is selected) is allowed to Read and/or Write to the controlled registers.

### 6.1.1 Task File ownership

Logic conventions are: A = signal asserted, N = signal negated, x = does not matter which it is.

Dark Gray are registers where ownership is controlled by BSY & DRO.

Light Gray are Registers that are not defined for use by ATA.

|       | Ad    | dresses |     |     | Functions                            |                       |  |  |

|-------|-------|---------|-----|-----|--------------------------------------|-----------------------|--|--|

| CS1FX | CS3FX | DA2     | DA1 | DA0 | Read (DIOR-) Write (DIOW-)           |                       |  |  |

| Α     | N     | 0       | 0   | 0   | D                                    | ata                   |  |  |

| Α     | N     | 0       | 0   | 1   | Errot Reguster                       | Features              |  |  |

| Α     | N     | 0       | 1   | 0   | ATAPI Interrupt Re                   | ason / Sector Count   |  |  |

| Α     | N     | 0       | 1   | 1   | Sector                               | Number                |  |  |

| Α     | N     | 1       | 0   | 0   | ATAPI Hyte Count                     | LSB / Cylinder Low    |  |  |

| Α     | N     | 1       | 0   | 1   | ATAPI Byte Count MSB / Cylinder High |                       |  |  |

| Α     | N     | 1       | 1   | 0   | Drive                                | Select                |  |  |

| Α     | N     | 1       | 1   | 1   | Status                               | Command               |  |  |

| N     | Α     | 0       | 0   | -0  | Floppy A Status                      | Unused                |  |  |

| N     | Α     | 0       | 0   | 1   | Floppy B Status                      | Unused                |  |  |

| N     | A     | 0       | 1   | 0   | Unused                               | Floppy Digital Output |  |  |

| N     | A     | 0       | 1   | 1   | Floppy ID / Tape Control             | RESERVED              |  |  |

| N     | Α     | 1       | 0   | 0   | Floppy Controller Status             | RESERVED              |  |  |

| N     | A     | 1       | 0   | 1   | Floppy Da                            | nta Register          |  |  |

| N     | A     | 1       | 1   | 0   | Alternate Status                     | Device Control        |  |  |

| N     | A     | 1       | 1   | 1   | Change / Drive Address               | Unused                |  |  |

Table 1 - Registers Controlled by BSY & DRQ

As you can see it is impossible to issue a new command for a number of reasons:

Can't write new command parameters into the Task File while BSY or DRQ is set. Either BSY or DRQ is always set from the time the command is issued until it is completed.

Changing the DRV bit will cause commands to be aborted in some existing ATA Hard Drives.

### 6.1.2 Sharing of ATA Hardware Signals

Provided that the problems of sending overlapped commands is solved, a new set of issues is exposed. These center around the sharing of signals from the ATA Device to the Host. These signals are used to Generate an Interrupt (INTRQ) and Control DMA operations (DMARQ, DMACK).

### 6.1.2.1 Sharing INTRQ

For example with one or more commands being processed in more than one device at the same time, when the drive needs to signal to the host that data or status is available, it uses INTRQ. This signal in ATA devices today is driven high when an interrupt is desired. In addition it is only driven by the device that is selected via the DRV bit. Thus there is no way, currently, to allow each device to independently generate an interrupt.

There are several basic approaches to solve this problem. The INTRQ Signal could be inverted and each peripheral can then drive it low to signal an interrupt, or the devices can decide between themselves which will be allowed to drive the signal. A hybrid of these approaches is to continue to use the existing INTRQ hardware, but allow the selected device to generate an interrupt for the non-selected device. This proposal will use this hybrid as it is believed that the arbitration by the devices themselves is far too complicated for any benefit that is derived. This would also force significant hardware changes in the devices. Note that the other proposals would make use of DASP and PDIAG- for device to device arbitration, and this would then prohibit the use of these signals for future enhancements (e.g. Parity.)

The request for the other device to generate an interrupt will be referred to as a "Proxy Interrupt" in this proposal. To allow the selected device to generate an interrupt for the non-selected device (Proxy), there must be some communication from the non-selected device to the selected device. This proposal will make use of the PDIAG- signal. This signal is not used after the Reset and Diagnostics have been completed and is already used to communicate between the devices. The PDIAG- is an inverted signal, and thus also is perfect for bidirectional communication. If during transitions the signal is driven by both the devices then there will be no damage or loss of protocol. The PDIAG- signal is currently driven by firmware in the devices and is thus available for a new protocol. It is assumed that only in the first generations of devices will this function be performed by firmware. Firmware delays will cause reduced performance compared with a hardware implementation for passing the PDIAG- through to the INTRQ signal.

Another advantage of the proxy interrupt is that the device that is currently selected has intimate knowledge of the current Task File state. It can thus only generate an interrupt for the non-selected device when the registers are idle. Thus if a data transfer or interrupt request or command is still being processed, the selected device will ignore any proxy interrupt request.

#### 6.1.2.2 Sharing DMARQ & DMACK

When it comes to the DMA control signals the problem again can be solved in one of two ways. Unlike the INTRQ signal the DMARQ can not just be driven by each of the devices at the same time. Only one device at a time must use the signal to communicate with the DMA logic on the mother board. In addition the DMA logic must also be kept in sync with the specific location in a specific command from a specific device. The easiest way to do this of course is to use the Host computer to setup the DMA logic and select the device that will be using it.

A more complicated technique would be to program the Host DMA Logic with information on all the outstanding commands, then have the devices themselves arbitrate for the use of the DMA control signals, then provide a communication path from the Device to the Host DMA Logic to tell it which device, command and location within the command is currently using the control signals. Western Digital has a real problem with this level of complexity. Adding all this logic to the host DMA will add significant cost and as such will never be "Main Stream." In addition this would not allow a phased approach to implementation, which Western Digital believes is important.

Thus the solution Western Digital proposes is to not change the existing DMA logic in the Devices, and allow either the Host Driver or the PCI DMA Overlap Logic to change the DRV bit.

This proposal is for the DMA operations to use a protocol similar to the current PIO protocol. In the current ATA DMA environment, the device assumes that it has complete control of the Host's DMA logic. Of course in an overlapped environment this is not the case. Thus when overlapped operation is enabled the device will not start DMA operations until the Select Command has been received. When the device wishes to transfer data via DMA, it requests the use of the DMA logic by asserting INTRQ (or PDIAG- when not selected) and waiting for the Select Command (A2h). Once the Select Command is received, the device can start the DMA by asserting DMARQ and following the normal ATA DMA protocol. The device must also place the number of bytes that will be transferred in the Byte Count Registers before BSY is cleared when processing the Select Command.

Once all the data that the device has available to transfer has been exhausted the device can either release the Task File registers by clearing BSY or not release the registers by keeping BSY set. The only allowable reason for keeping BSY set is to allow the drive to place the Completion Status into the Task File Registers and then generating an Interrupt. This removes the extra interrupt to regain the us of the Task File Registers.

#### 6.1.3 Other DMA issues

An overall issue of DMA, is that of using the interface for any other operations while the DMA is in progress. DMA makes actual reads and writes to the Data Register of the device performing the DMA. Thus it would be impossible to issue new commands to the device that is performing active DMA. In this proposal the DMA as well as the arbitration is performed by the Overlapped PCI DMA Bridge Logic. Today when DMA is used the command is issued to the device, and no further interrupts are generated until the DMA is complete.

In this proposal the DMA operation will be changed to be much closer to that of the PIO protocol used today. This will add some extra interrupts if the Host does not support the Overlapped PCI DMA Bridge Logic, but will still allow DMA and overlap to be used. This it is believed will still provide significant performance improvements.

#### 6.1.4 Other Problem areas with ATA

Although the Overlapped capability is one of the major areas that need to be addressed, there are other weaknesses as well.

Status is not provided after the data is transferred.

The data transfers are always 512 bytes or some fixed multiple.

ATA-3 Proposal

### 6.2 Driver Issues

This section should contain any currently understood sequences that the drivers will be responsible for.

• When there will be more than one ATA Driver in the system some form of interlock (semaphore) will need to be employed. Currently there is no mechanism to lock access to the Task File Registers between Drivers.

# 7.0 Proposal Details

This proposal makes the attempt to combine discussions of the solutions into just a few categories. In each of these categories all the pertinent information related to the Host Driver, Host Silicon, Drive Firmware and Drive Silicon will be covered. Rather than just cover the device side implementation as is usual for X3T10, all the interrelated functionality needs to be discussed.

This proposal is broken up into four separate capabilities:

- Overlapped Operation.

- Proxy Interrupts.

- · Command Queuing.

- Advanced or Descriptor Based DMA.

## 8.0 Overlapped Operation

This section will discuss the overall capability of "Overlap." This is the foundation for all the other capabilities. There are two very slightly different variations of the Overlap Capability for the Devices, one for ATA and another for ATAPI. In the ATAPI world there are plenty of registers available in the Task File for the Link Layer information. In the ATA world all the bits are dedicated to passing parametric information and as such none (too few) are available to extend the functionality. This proposal requires the Overlap Capability to be enabled on a command by command basis. Although this is strictly not needed for just the simple overlapping of commands, when the Tags are introduced later, this becomes more important. Rather than try to change the method of overlap between simple overlapped and queued commands, this proposal makes them identical with the exception of the use of the Tags when sending the command to the Device.

### 8.1 Task File Changes for Overlap

### 8.1.1 Overlap for ATA commands

The overlap is enabled by using two new ATA Commands, READ Tagged and WRITE Tagged commands only. All other commands can not be overlapped. There is no real reason for commands that do not access the media to be overlapped. These commands operate quickly and thus do not need overlapping. If overlapping was to be supported for ATA Commands, then there would need to be a Command by Command enable, so that there would be no backward compatibility issues when dropping back to an "Older Style" driver in sever error conditions. As there is no place in the Task File for an Enable bit, this approach of the two new commands was taken.

In addition the definition for the ATA Feature Register changes when the Overlap Commands are used.

Figure 7 - Changes to the ATA Feature Register (ATA Tag) for Overlapped Operation

| D7 | D6 | D5  | D4    | D3 | D2 | D1       | D0  |         |

|----|----|-----|-------|----|----|----------|-----|---------|

|    |    | Tag | Value |    |    | Reserved | DMA | Write O |

#### 8.1.2 Overlap for ATAPI Commands

As has already been discussed, the overlap capability is enabled on a command by command basis. There exists in ATA-PI a register dedicated to this function, the Features Register. Thus each command is changed into an overlapped style command via the Overlap Enable bit in the ATAPI Features Register. As this register is used for every ATAPI command, they can all can be overlapped.

Figure 8 - Changes to the ATAPI Feature Register for Overlapped Operation

| D7 | D6 | D5   | D4    | D3 | D2 | D1                              | D0         |

|----|----|------|-------|----|----|---------------------------------|------------|

|    |    | Reso | erved |    |    | Overlapped<br>Command<br>Enable | DMA Enable |

# 8.1.3 Status register for Overlapped Operation

Figure 9 - Changes to Status and Alternate Status Registers for Overlapped Operation

| Ī  | D7   | D6           | D5           | D4                         | D3             | D2              | D1             | D0                |                                               |

|----|------|--------------|--------------|----------------------------|----------------|-----------------|----------------|-------------------|-----------------------------------------------|

|    | BSY  | DRDY         | DMA<br>Ready | SERVICE                    | DRQ            | CORR            | IDX            | CHECK<br>or ERROR | Read                                          |

| Bi | it 7 | BSY          |              | Busy is set                | whenever the   | e drive has acc | cess to the Co | ommand Block      | k.                                            |

| Bi | it 6 | DRDY         |              | be cleared                 | at power on.   | Devices that    | implement t    | agged comma       | This bit shall nds shall clear and into their |

| Bi | it 5 | DMA Ready    |              | used to cor                | nmunicate to   |                 | Capable PC     |                   | ansfer. This is<br>that this ser-             |

|    |      |              |              | Note that t<br>is not enab |                | ed for Drive l  | Fault (DF) N   | vhen the Ove      | rlap operation                                |

| Bi | it 4 | SERVICE      |              | will be set                | •              | errupt is requ  |                |                   | rrupt. This bit<br>il the SELEC-              |

|    |      |              |              | Note that t<br>not enable  |                | d for the DSC   | C function w   | ith the Overla    | p operation is                                |

| Bi | it 3 | DRQ          |              | data betwe                 | en the host a  | nd the drive.   | The informa    |                   | vord or byte of TAPI Interrupt PRQ is set.    |

| Bi | it 2 | CORR         |              | Indicates if               | a Correctabl   | e Error occurr  | red.           |                   |                                               |

| В  | it 1 | IDX          |              | Index statu                | s. This bit is | Vendor Specif   | ic.            |                   |                                               |

| Bi | it O | CHECK or ERI | ROR          | Indicates th               | at an error o  | ccurred during  | g execution o  | f the previous    | command.                                      |

# 8.1.4 Task File Register usage for ATAPI Devices implementing Overlap

| Addr<br>esses | D7  | D6    | D5           | D4               | D3           | D2          | DI                                      | D0    | Register               |

|---------------|-----|-------|--------------|------------------|--------------|-------------|-----------------------------------------|-------|------------------------|

| 1F0           |     |       |              |                  |              |             | 000000000000000000000000000000000000000 | •     | Data                   |

| 1F1           |     | Sense | e Key        |                  | MCR          | ABRT        | EOM                                     | ILI   | Error Register         |

|               |     |       |              |                  |              | <del></del> | Overlap                                 | DMA   | ATAPI Feature Register |

| 1F2           |     |       |              |                  |              | Release     | IO                                      | C₀D   | Interrupt Reason Reg   |

| 1F3           |     |       |              | Ta               | g            |             |                                         |       | Tag Register           |

| 1F4           |     | Byte  | Count that v | vill be used for | or PIO or fo | TDMA oper   | ations                                  |       | Byte Count Low         |

| 1F5           |     |       |              |                  |              |             |                                         |       | Byte Count High        |

| 1 <b>F</b> 6  |     |       |              | DRV              |              | He          | ad                                      |       | Drive Select           |

| 1F7           | BSY | DRDY  | DMA          | Service          | DRQ          | CORR        | IDX                                     | ERR   | Status                 |

|               |     |       |              | 0xA0 o           | r 0xA2       |             |                                         |       | Command                |

| 3F6           | BSY | DRDY  | DMA          | Service          | DRQ          | CORR        | IDX                                     | Check | Alternate Status       |

|               |     |       |              |                  |              | SRST        | nIEN                                    |       | Device Control         |

| 3F7           |     | L     |              | DEV              |              | Head S      | elected                                 |       | Change / Drive Address |

Table 2 - ATAPI Overlapped Commands, Register Usage

420

#### 8.2 Release

One of the capabilities that is the foundation for Overlapped operation is Release. There are three different forms of release used in this proposal, after the receipt of a Command, after transferring some data and after the receipt of the SE-LECT Command.

This proposal will allow the device to implement these release operations either in the Firmware or in Hardware. Each of these release points has its own complexities. For example before the Task File Registers can be released after the receipt of a command, the Command and parameter information must be saved. Once the release is performed the contents of the Task File Registers can no longer be used by the Device. Although this save would seem simple, adding a complete set of shadow registers is expensive and will not allow the device to perform command queueing. For command queuing there must be separate registers/memory locations for each of the commands that can be queued. Thus if the device supports 16 commands, then 16 back to back commands could be sent to the device by the host faster then the device could process them. The device could have only one set of shadow registers and only automatically release the Task File Registers when moving the standard set into the shadow set, but this would incur delays for release when the second command was loaded if the first had not yet been processed by the device. This would thus cause inconsistent delays until the Task File Registers were released.

In this proposal it is assumed that device will consistently unload the information in the Task File Registers. Although holding the BSY longer in some cases would most likely be acceptable from a system performance standpoint, forcing the driver to poll for varying lengths of time is not. This proposal forces the device to report the maximum length of time that the device will EVER require to unload and then Release the Task File Registers. Further to reduce the length of time that the Driver would have to poll for the Release, this proposal adds an Interrupt on Release Capability.

The Interrupt on Release capability is enabled by the Host Driver using a SET FEATURES Command. To assist the Driver in determining if the Interrupt should be enabled the IDENTIFY DRIVE Command returns the length in microseconds that the device will use to Release for both a Overlapped Command and the SELECT Command. The Driver can then make its own decision to enable the interrupt. Thus if the Device reports 1000 microseconds, the Driver could decide that it wants to poll and not enable the interrupt (Unlikely). This should remove the debate on how long should the driver have to poll.

The Release after the transfer of data must be performed by hardware for DMA operations and as such there is no Interrupt generated after the release when transferring data.

The Release after the SELECT Command can only occur after the parameters for the Interrupt are loaded into the Task File Register. Thus for a hardware implementation of this Release, there must exist a separate set of information (Shadow Registers) for these parameters e.g. Byte Count, Interrupt Reason, Status. Note that even for Command Queuing there needs to be only one set of Shadow Registers. The acceleration of the SELECTION Command will be very important to the overall system performance when using overlap. It is highly recommended that the time required to perform the Release after the SELECTION Command is less than 5µs.

### 8.3 Using the Select Command (A2h)

The Arbitration of the Task File Registers is performed by logic outside of the Devices attached to the ATA Cable. The basic premise of this proposal is that the Device releases the use of the Task File Registers when it is processing the command and no longer needs the registers. This of course makes it difficult to place the arguments for the Interrupt into the registers as the device no longer owns them. The Select command essentially hands the registers back to the device so that the correct parameters can be placed into them. These parameters include the Byte Count, Interrupt Reason and Command Tag values.

When an overlapped command requests service the Host Driver or PCI DMA Logic is responsible for determining which device should be serviced, and then issuing the Select. This causes the device to place information on the reason for the service into the Task File registers. Note that for both ATA and ATAPI devices the results of the Select Command are the same.

| Addr<br>esses | Register                 | Contents                                                                        |

|---------------|--------------------------|---------------------------------------------------------------------------------|

| 1F0           | Data                     |                                                                                 |

| 1F1           | Error Register           | If the Status indicates an Error then this is Valid                             |

| 1F1           | ATA Tag for Command      | TAG for ATA Command. Only used when sending the command to the Device.          |

| 1F2           | Interrupt Reason         | Contains IO and CoD                                                             |

| 1F3           | Tag for Command          | Contains the Tag for the command requiring Service                              |

| 1F4           | ATAPI Byte Count LSB     | Number of bytes that need to be transferred, both for                           |

| 1F5           | ATAPI Byte Count MSB     | PIO or for DMA                                                                  |

| 1F6           | Drive Select             | Same before and after "Select"                                                  |

| 1F7           | Status                   | DRQ along with IO, Cod and Release determine the reason for the Service Request |

| 3F0           | Floppy A Status          | Unused                                                                          |

| 3F1           | Floppy B Status          |                                                                                 |

| 3F2           | Unused                   | 1                                                                               |

| 3F3           | Floppy ID / Tape Control |                                                                                 |

| 3F4           | Floppy Controller Status | 1                                                                               |

| 3F5           | Floppy Data Register     | 1                                                                               |

| 3F6           | Alternate Status         | Same as Status register                                                         |

| 3F7           | Change / Drive Address   | Same before and after "Select"                                                  |

Table 3 - Registers after the Selection Command

### 8.4 Error Handling with Overlapped Commands

An issue can arise with because overlapped commands are enabled on a Command by Command basis. If an overlapped command is in progress and a non-overlapped command is then received, the Device must abort without any status any outstanding overlapped or queued command(s).

ATA-3 Proposal

### 9.0 Proxy Interrupts

The sharing of the Hardware ATA signal for requesting an interrupt (INTRQ) to the host is enabled by a SET FEA-TURES command. Note that this feature must be enabled for both devices on the cable. If either of the devices does not support Proxy, or if the set features command to enable the capability is aborted, the capability must be disabled in both devices.

When Proxy interrupts are enabled the SERVICE bit in the Status and Alternate Status registers will indicate that an interrupt was generated. This status bit will remain set until the condition that caused the interrupt is cleared. This could be Sending a Selection Command (A2h) or starting a data transfer for an ATA style command. Because this is a capability that is enabled once, it must be kept backward compatible with existing ATA commands and Drivers.

### 9.1 Rules regarding use of Proxy Interrupts

The PDIAG- signal is used to request a "Proxy" interrupt. The PDIAG- signal is defined in the ATA Standard as tristate. When the Proxy capability is enabled, each device will Tristate the PDIAG- signal. This signal has a pullup that will then drive the signal to +5 volts. This high level is the Deasserted or Idle level. Whenever the Device is NOT requesting a Proxy Interrupt, the PDIAG- shall be tristated. When a Proxy Interrupt is to be requested the PDIAG- signal will be enabled and driven to a low level. This is the "Asserted" state.

In this proposal the INTRQ signal continues to obey the ATA Standard definition. INTRQ will only be driven by the selected drive. The INTRQ signal will be driven to a High logic state when an Interrupt is being requested. The INTRQ signal, once driven to a high logic level will be again driven to a low logic level when the ATA STATUS REGISTER is read by the host.

1. When a selected device is not actively using the Task File e.g.

Device not interrupting; and

BSY is clear; and

DRQ is clear; and

Proxy Interrupts are enabled using set features command

Then the selected device shall:

Assert INTRQ if PDIAG- is at a logic low (Proxy Interrupt is being requested)

- 2. When a selected device releases the Task File (Bsy & DRQ Cleared) the device shall discontinue requesting an interrupt, before BSY & DRQ are cleared, by tristating the devices PDIAG- driver and pulling PDIAG- high through the existing 10k pull up resistors on each device.

- 3. When a non-selected device, with overlap enabled, wishes to interrupt the host, the device shall set the SERVICE and optionally the DMA READY status bits, Enable PDIAG- and drive PDIAG- active low.

- 4. When a selected device receives a SELECT command, it shall clear any pending SERVICE request and discontinue requesting an interrupt (Tristate PDIAG-, allowing it to be pulled up to +5 volts)

- The ATA EXECUTE DRIVE DIAGNOSTICS command shall cause Proxy Interrupts to be disabled. The host shall re-enable Proxy Interrupts following each diagnostic command using the enable Proxy Interrupts set features command.

- 6. When a Device that is driving PDIAG- low is selected, the Device shall tristate PDIAG- and Drive INTRQ high.

### 9.2 Why Proxy

Is this arbitration proposal a basic PROXY protocol? Yes, in the proposal the selected drive is still the only device which can issue an interrupt to the host. The non selected device drives PDIAG- to a logic low to request that the selected device interrupt the host for it.

What happens if the selected device is busy with a command or transferring data? When the selected device is busy it can block the interrupt request from the non-selected device. This is a crucial interlock which allows the selected device to prevent conflicts over the task file and DMA resources.

How long can the selected device block an interrupt request without causing the host to miss the requested interrupt? Like all level based ATA interrupts there is no time limit. The non-selected device will continue to drive PDIAG- to a logic low, to request an interrupt, until it is selected or reset by the host.

If I implement this arbitration protocol in F/W then there will probably be an overlap between the time my device is selected and the time I stop driving PDIAG-. How will we guarantee that we do not blow up drivers when both devices are driving PDIAG-. This proposal relies on using PDIAG- drivers which tristate with a pull-up to go to a logic high (NO INTRQ Request) and drive the signal to a logic low (Interrupt Request). This is a pseudo Open collector configuration and as such no driver conflicts exist.

Why don't we just use PDIAG- as a second interrupt to the host controller logic? The current proposal works without changes to the ATA host electrical interface which has been shipping for over five years. Many Mother board VLSI manufacturers have also stated that they are pin limited on embedded IDE implementations. Drive manufacturers have also noticed that features which can be implemented with hardware changes only in the drive find their way to the mass market much sooner than those which require changes to the host interface logic.

How does the arbitration proposal fit in with the ATA-3 discussion on WEAK Overlap, STRONG Overlap and Queuing? This arbitration proposal is designed to eliminate the difference between WEAK and STRONG overlapped command protocols. Western Digital believes that this proposal addresses the concerns on both WEAK and STRONG Overlapped commands. e.g. it provides for a F/W only implementation of strong Overlapped commands eliminating the need for a separate weak overlapped command protocol. This should simplify the task of device and driver development.

# 10.0 Enabling Enhanced Capabilities

The Set Features command is used to set some interface timing and protocol modes. These modes are set at Post by many BIOSes. The contents of the ATA Features Register indicates the function to be performed.

Table 4 - Contents of the Feature Register for Set Features Command

| Bit<br>Byte | 7                                | 6 | 5 | 4 | 3             | 2 | 1 | 0 |

|-------------|----------------------------------|---|---|---|---------------|---|---|---|

| 0           | Set (1)/<br>Clear (0)<br>Feature |   |   | 1 | Feature Numbe | π |   |   |

| Feature Register<br>Contents | Set Feature Commands                                                     | Support                                       |

|------------------------------|--------------------------------------------------------------------------|-----------------------------------------------|

| 5Dh                          | Enable Interrupt for Release after the receipt of an Overlapped Command  | Mandatory if the Device requires              |

| 5Eh                          | Enable Interrupt after the processing of Select (A2) Command             | more than 50µs to process a Release operation |

| 5Fh                          | Enable Proxy Interrupt Capability                                        | Mandatory for an<br>Overlap Capable<br>Device |

| DDh                          | Disable Interrupt for Release after the receipt of an Overlapped Command | Mandatory if the Device requires              |

| DEh                          | Disable Interrupt after the processing of Select (A2) Command            | more than 50µs to process a Release operation |

| DFh                          | Disable Proxy Interrupt Capability                                       | Mandatory for an<br>Overlap Capable<br>Device |

Table 5 - Feature Number Description for Set Feature Command

# 11.0 Identifying Device's Capabilities

Table 6 - Identify Drive Data - Capabilities Word (49)

| Bit<br>Byte | 7/15                                   | 6/14                            | 5/13                 | 4/12                                       | 3/11               | 2/10                          | 1/9                | 0/8                |

|-------------|----------------------------------------|---------------------------------|----------------------|--------------------------------------------|--------------------|-------------------------------|--------------------|--------------------|

| 0           |                                        |                                 | -                    | Vendor                                     | Unique             |                               |                    |                    |

| 1           | Inter-<br>leaved<br>DMA Sup-<br>ported | Command<br>Queuing<br>Supported | Overlap<br>Supported | Reserved<br>for Pseudo<br>DMA Sup-<br>port | IORDY<br>Supported | IORDY<br>can be dis-<br>abled | LBA Sup-<br>ported | DMA Sup-<br>ported |

| Bit 8  | DMA Supported               | This bit indicates that the Device supports the DMA mode of data transfer.                                                                                                                                                        |

|--------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 9  | LBA Supported               | Indicates that the Device supports the LBA form of addressing. The ATAPI Devices must set this bit to one.                                                                                                                        |

| Bit 10 | IORDY can be disabled       | Is used to indicate a device's ability to enable or disable the use of IORDY. If this bit is set to one, then the device does not support the changing of IORDY.                                                                  |

| Bit 11 | IORDY Supported             | This is used to help determine whether a device supports IORDY. If this bit is set to one, then the device supports IORDY operation. If this bit is zero then the device may support IORDY (this insures backward compatibility.) |

| Bit 13 | Overlap Operation Supported | This device supports the features in this proposal. Both the Release and Select protocol and the Proxy Interrupt capability must be supported to report that the Device supports Overlap Operation.                               |

|        |                             | When the Overlap Operation is supported, words 71 and 72 must also contain valid information.                                                                                                                                     |

| Bit 14 | Command Queuing             | This device supports Command Queuing and Command Tagging.                                                                                                                                                                         |

| Bit 15 | Interleaved DMA             | This device supports the Interleaving of DMA data as specified in this proposal.                                                                                                                                                  |

There is no need to Enable or Disable Command Queuing/Tagging. This capability is enabled by the use of the Queuing Command opcodes. Note that these commands can be used, even if Overlapped operations are not enabled. If READ or WRITE TAGGED is used then the Overlapped operation is automatically enabled. In this case the Overlap being enabled causes the SERVICE and DMA Ready status bit to be used.

### 11.1 Reporting of Overlap Timing Constraints

When Overlapped Operation is supported there are other informational words in the Identify Drive Data:

Length (Maximum) in  $\mu$  seconds for the Release after Command Function.

Length (Maximum) in  $\mu$  seconds for the Release after Select.

Thus the Driver can determine if it wants to Poll for the operation or to enable the interrupt so that it does not need to poll. Note that if the time reported for either Release Operation is greater than 50µs then interrupts must also be supported.

Table 7 - Identify Drive, Fields supported

| Word    | Description                                                          |

|---------|----------------------------------------------------------------------|

| 0       | General Configuration.                                               |

| 1       | Cylinders                                                            |

| 3       | Heads                                                                |

| 4       | Number of unformatted bytes per track                                |

| 5       | Number of unformatted bytes per sector                               |

| 6       | Number of sectors per track                                          |

| 10-19   | Serial Number                                                        |

| 20      | Buffer Type                                                          |

| 21      | Buffer Size                                                          |

| 22      | ECC bytes available                                                  |

| 23-26   | Firmware revision                                                    |

| 27-46   | Model Number                                                         |

| 47      | Multiple Sector Command, Sector Count                                |

| 48      | Double Word I/O                                                      |

| 49      | Capabilities                                                         |

| 51      | PIO Cycle Timing                                                     |

| 52      | DMA Cycle Timing                                                     |

| 53 - 56 | Current Cylinder/Heads/Sectors and Enable                            |

| 57-58   | Current Capacity                                                     |

| 60-61   | User Addressable Sectors                                             |

| 62      | Singleword DMA mode                                                  |

| 63      | Multiword DMA mode                                                   |

| 64      | Enhanced PIO mode                                                    |

| 65      | Blind PIO minimum cycle time                                         |

| 66      | Manufacturer's Recommended Multiword DMA Cycle Time                  |

| 67      | Minimum PIO Transfer Cycle Time without Flow Control                 |

| 68      | Minimum PIO Transfer Cycle Time with IORDY Flow Control              |

| 69-70   | Reserved for Advanced PIO support                                    |

| 71      | Length (Maximum) in µ seconds for the Release after Command Function |

| 72      | Length (Maximum) in $\mu$ seconds for the Release after Select       |

| 73-127  | Reserved                                                             |

| 128-159 | Vendor Specific                                                      |

| 160-255 | Reserved                                                             |

### 12.0 Overlapped PCI DMA

The overlapped PCI DMA Logic emulates in a simple form what the Host Driver would do when an interrupt is detected. Thus the ATA or ATAPI Device is unaware of any difference between a driver and the PCI DMA Logic.

To allow the PCI DMA Logic to more easily detect that DMA transfer is required, a new status bit has been added, called DMA Ready. This bit in conjunction with the Service bit and INTRQ signals to the PCI DMA Logic that it should start a DMA Operation for this device. Note that the DMA Logic must have previously been programmed for the transfer.

Use of the DMA Ready status and Service bits is enabled when overlapped Command are issued with the DMA enable bit set in the ATA or ATAPI Feature Registers.

Whenever the PCI DMA Logic senses a condition where it can not handle the interrupt (e.g. No DMA was setup for this device, or the DMA Ready and Service bits were not set) the Interrupt is passed through to the Driver. The Driver is then responsible for providing the same level of functionality as in the PCI DMA Logic. Note also that if the Host doesn't support the Overlapped DMA Capability, then the driver will provide that functionality.

To prevent the Host from accessing the ATA bus while any possible contention could occur, the PCI DMA Logic contains an Interlock mechanism. This is nothing more than a simple semaphore. When the Host commands the PCI DMA Logic to start overlapped operations, the Semaphore is seized by the DMA Logic. When the Driver wishes to gain access to the ATA Bus, it requests that the Semaphore is released and then waits until it is.

This might be a case for an addition of an Interrupt so that the driver won't have to poll.

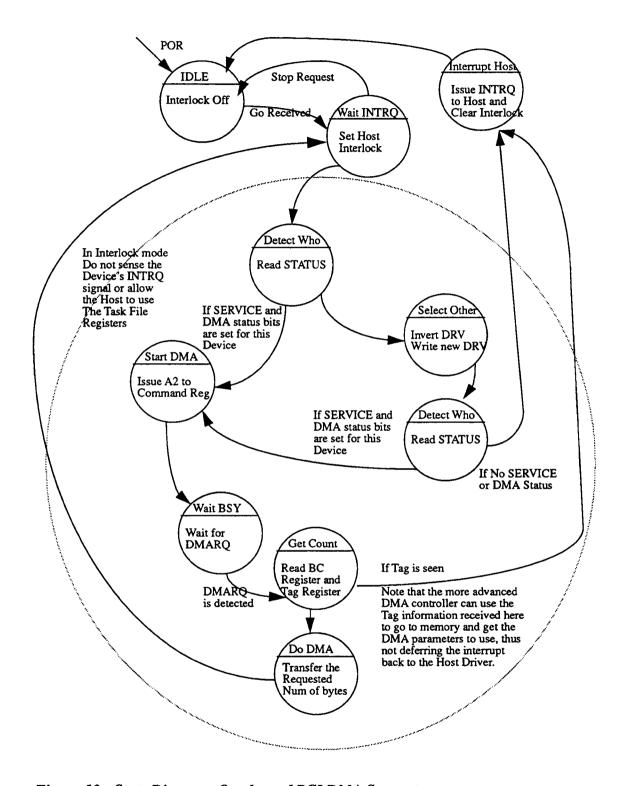

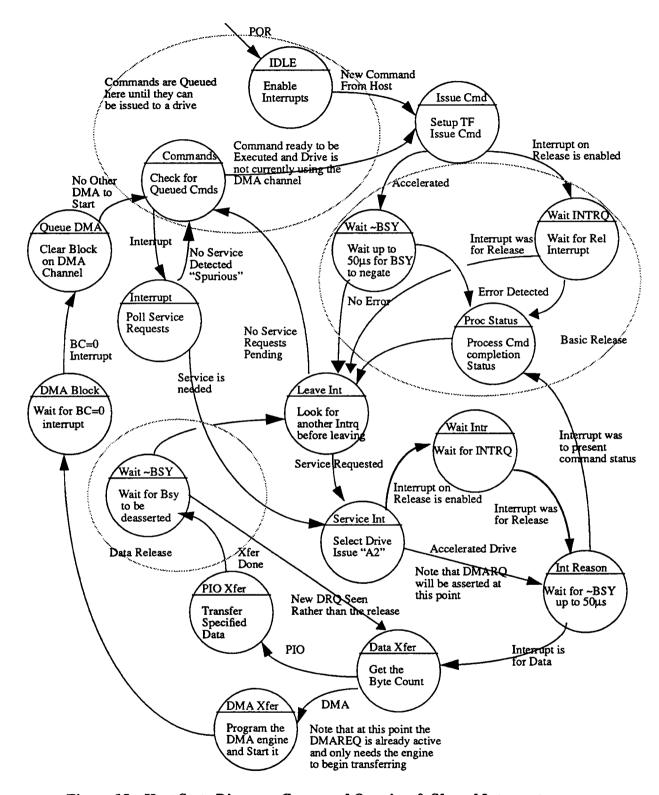

Figure 11 - Overlapped PCI DMA Block Diagram

#### 12.1 Error Handling with Overlapped DMA

Error handling is no different than is used today.

#### 13.0 IDE ATA Bus Master DMA

This section proposes a register level programming interface for a bus master ATA compatible (IDE) disk controller that directly moves data between IDE devices and main memory. By performing the IDE data transfer as a bus master, the Bus Master Device off-loads the CPU (no programmed IO for data transfer) and improves system performance in multitasking environments.

Controllers that implement this programming interface will benefit from bundled software shipped with major OS's limiting the amount of software development required to provide a complete product.

The master mode programming interface is an extension of the standard IDE programming model. This means that devices can always be dealt with using the standard IDE programming model, with the master mode functionality used when the appropriate driver and devices are present. Master operation is designed to work with any IDE device that support DMA transfers on the IDE bus. Devices that only work in PIO mode can be used through the standard IDE programming model.

The programming interface defines a simple scatter/gather mechanism allowing large transfer blocks to be scattered to or gathered from memory. This cuts down on the number of interrupts to and interactions with the CPU.

The interface defined here supports two IDE channels (primary and secondary). Individual controllers that support more than two channels will need to appear to software as multiple controllers if the standard drivers are to be used.

Master IDE controllers should default to Mode 0 Multiword DMA timings to ensure operation with DMA capable IDE devices without the need for controller-specific code to initialize controller-specific timing parameters.

### 13.1 Physical Region Descriptor Table

Before the controller starts a master transfer it is given a pointer to a Physical Region Descriptor Table. This table contains some number of Physical Region Descriptors (PRD) which describe areas of memory that are involved in the data transfer. The descriptor table must be aligned on a 4 byte boundary and the table cannot cross a 64K boundary in memory.

### 13.2 Physical Region Descriptor

The physical memory region to be transferred is described by a Physical Region Descriptor (PRD). The data transfer will proceed until all regions described by the PRDs in the table have been transferred.

Each Physical Region Descriptor entry is 8 bytes in length. The first 4 bytes specify the byte address of a physical memory region. The next two bytes specify the count of the region in bytes (64K byte limit per region). A value of zero in these two bytes indicates 64K. Bit 7 of the last byte indicates the end of the table; bus master operation terminates when the last descriptor has been retired.

Table 8 - Physical Region Descriptor Table Entry

| 31                                         |  |  | 0 |  |  |

|--------------------------------------------|--|--|---|--|--|

| Memory Region Physical Base Address [31:1] |  |  |   |  |  |

| EOT Reserved Byte Count [15:1]             |  |  |   |  |  |

NOTE: The memory region specified by the descriptor is further restricted such that the region cannot straddle a 64K

boundary. This means the byte count can be limited to 64K, and the incrementer for the current address register need only extend from bit [1] to bit [15]. Also, the total sum of the descriptor byte counts must be equal to, or greater than the size of the disk transfer request. If greater than, then the driver must terminate the Bus Master transaction (by resetting bit zero of the command register to zero) when the drive issues an interrupt to signal transfer completion.

#### 13.3 Bus Master IDE Register Descriptions

The bus master IDE function uses 16 bytes of IO space. All bus master IDE IO space registers can be accessed as byte, word, or Dword quantities. The description of the 16 bytes of IO registers follows in Table 2-1:

Table 9 - PCI DMA IO Register Map

| Offset from Base Address | Decreter                                   |     |  |  |  |  |  |

|--------------------------|--------------------------------------------|-----|--|--|--|--|--|

| 00h                      | Bus Master IDE Command register Primary    | R/W |  |  |  |  |  |

| 01h                      | Device Specific                            |     |  |  |  |  |  |

| 02h                      | Bus Master IDE Status register Primary     | RWC |  |  |  |  |  |

| 03h                      | Device Specific                            |     |  |  |  |  |  |

| 04h-07h                  | Bus Master IDE PRD Table Address Primary   | R/W |  |  |  |  |  |

| 08h                      | Bus Master IDE Command register Secondary  | R/W |  |  |  |  |  |

| 09h                      | Device Specific                            |     |  |  |  |  |  |

| 0Ah                      | Bus Master IDE Status register Secondary   | RWC |  |  |  |  |  |

| 0Bh                      | Device Specific                            |     |  |  |  |  |  |

| 0Ch-0Fh                  | Bus Master IDE PRD Table Address Secondary | R/W |  |  |  |  |  |

Figure 12 - PCI DMA IO Registers, BIt Definitions

| Address              | D7        | D6                        | D5                        | D4                                            | D3                                    | D2                        | D1                | D0                                                   |

|----------------------|-----------|---------------------------|---------------------------|-----------------------------------------------|---------------------------------------|---------------------------|-------------------|------------------------------------------------------|

| Base +0<br>Command   | Saft Stop |                           | Reserved                  |                                               | Read/<br>Write                        | Inter-<br>leave<br>Enable | Overlap<br>Enable | Start/Stop                                           |

| Base +1              |           |                           |                           | Reserved or D                                 | evice Specifi                         | С                         |                   |                                                      |

| Base +2<br>Status    | Simplex   | Drive 1<br>DMA<br>Capable | Drive 0<br>DMA<br>Capable | Channel is Over- lap and Inter- leave Capable | Select<br>(A2h)<br>has been<br>issued | Interrupt                 | Error             | Active<br>and also<br>the Inter-<br>lock Sta-<br>tus |