Preface

CCU Architecture: D0.52

X3T9.2/92-131r1: 13Aug92:

# CCU Architecture

#### A Common Command Unit Architecture based on P1212.1 Shareable List DMA

X3T9.2/92-131r1 / D0.52 13Aug92

#### Abstract

This document specifies the I/O process that provides communication between a I/O driver and an I/O service. The scope of the specification includes the formats of command and status lists, the list-update operations, device registers, and ROM entries. This document assumes that nodes are connected using the P1394 Serial Bus and that devices fully comply with the IEEE Std 1212-1991 CSR Architecture. This document is based on the concepts developed within the P1212.1 DMA Framework working-group draft.

CCU Architecture: D0.52

Preface

X3T9.2/92-131r1: 13Aug92:

NOTE: Copies of this document may be purchased from: Global Engineering Documents, 2805 McGaw, Irvine, CA 92714 (800) 854-7179 or (714) 261-1455. Please refer to document X3T9.2/92-131

draft proposed American National Standard for information systems -

Common Command Unit Architecture CCU

13Aug92

Secretariat

Computer and Business Equipment Manufacturers Association

This is a draft proposed American National Standard of Accredited Standards Committee X3. As such, this is not a completed standard. The X3T9 Technical Committee may modify this document as a result of comments received during X3 approval as a standard.

COPYRIGHT NOTICE: This draft standard may be reproduced, for the purpose of review and comment only, without further permission, provided this notice is included. All other rights are reserved.

Ed Note: The appropriate legal stuff has to be put here.

Comments on this Draft should be addressed to the current Editor: either of the Editors:

Scott Smyers Apple Computer, Inc. 20705 Valley Green Drive, MS: 60-AR Cupertino, CA 95014 voice: 408/974-7057

fax: 408/446-9154

email: smyers.s@applelink.apple.com

Comments may also be addressed to the previous (and still somewhat active) editors:

Daniel C. O'Connor Apple Computer, Inc. 20705 Valley Green Drive, MS: 60-AR Cupertino, CA 95014

voice: 408/974-6753 fax: 408/446-9154

email: doconnor@apple.com

Dave James Apple Computer, Inc. 20450 Stevens Creek Blvd., MS: 60-AR Cupertino, CA 95014 voice: 408/974-1321 fax: 408/974-9793

email: dvj@apple.com

# Contents

|                                                           | 11         |

|-----------------------------------------------------------|------------|

| Contents                                                  |            |

| Listings                                                  | ۷<br>      |

| Figures                                                   | vi         |

| Tables                                                    | VII        |

| Foreword by the Chairman of the Working Group             | viii       |

| Working Group Members                                     | 1X         |

| 1 Introduction                                            | L          |

| 1 1 I/O Process Overview                                  | L          |

| 1.1.1 I/O Process Components                              | 1          |

| 1 1 2 Stops in the I/O Process                            | Z          |

| 1 1 3 Shared-Queue Transfers                              | ວ          |

| 1 1 4 Initiator and Target Resources                      | 4          |

| 1 1 5 Design Canabilities                                 | 4          |

| 1.2 Glossam and Notation                                  | ວ          |

| 1 2 1 Conformance Levels                                  | ə          |

| 1 2 2 Glassary of Terms                                   | 0          |

| 1 2 Bit Bute and Quadlet Ordering                         | o          |

| 1 4 Numorical Values                                      |            |

| 1 5 Address Dainters                                      | y          |

| 1 5 1 4/8 byte Aligned Pointers                           |            |

| 1 5 9 16 byte Aligned Pointers                            |            |

| 1.6 Momory Access Operations                              | LU         |

| 1 6 1 List and Management Operations                      | 1U         |

| 2 Tist Undata Protocols                                   |            |

| 2.1 Command and Status List Structures                    |            |

| 9.1.1 Tiet Structures                                     |            |

| 2.1.2 Empty (Zero-Entry) List Structures                  |            |

| 2.2 List Append Operation                                 | Lū         |

| 2 2 1 Appending One Entry                                 |            |

| 2 2 2 Appending Multiple Entries                          | TO         |

| 2.2 List Extract Operation                                | 1 <i>1</i> |

| 9 9 1 Extractor Wakeins                                   |            |

| 2.3.2 List Extractions                                    | 17         |

| 2.4 Append and Extract Specification                      |            |

| 2.4.1 Append and Basic Extract                            | 19         |

| 2.5 Wakeup Registers                                      | 22         |

| 2.5.1 Target Wakeup Register Model                        | 22         |

| 2.5.2 Initiator Wakeup Register Model (Broadcast Capable) | 22         |

| 2.5.2 Initiator Wakeup Register Model (Directed Only)     | 23         |

| 3. Command-List Structure                                 |            |

| 3.1 Command Entries                                       | 24         |

| 3.2 Command Groups                                        | 24         |

| 3.3 Data Transfer Addresses                               | 26         |

| 3.3.1 Direct and Indirect Address Blocks                  | 26         |

| 3.3.1 Direct and indirect Address Diocks                  | 28         |

| 3.3.2 Data-Block Transfer Examples                        | 2.9        |

| 3.3.2.2 Indirect-Initiator/Direct-Target Transfers        | 2.9        |

| 3.3.2.2 Indirect-Initiator/Direct-Target Transfers        | 3(         |

| 3.3.2.3 Indirect-Initiator/Indirect-Target Transfers      | 91         |

| 3.4 Constant Transfers                                    | Q-         |

| 3.4.1 Initiator Constant used with Read Command           | و          |

| 3.4.2 Initiator Constant used with Copy Command           |            |

| 3.4.3 Target Constant used as Device-Dependent Command                                   | 31 |

|------------------------------------------------------------------------------------------|----|

| 3.5 Data-Transfer Constraints                                                            | 32 |

| 3.5.1 Unaligned or Cross-Block Transfers                                                 |    |

| 3.5.2 Aligned Sub-Block Transfers                                                        |    |

| 4. Data Formats                                                                          | 34 |

| 4.1 Command Entry                                                                        | 34 |

| 4.1.1 listControl Field                                                                  | 36 |

| 4.1.1.1 listControl Format                                                               | 36 |

| 4.1.1.2 listControl.cmd Values                                                           | 37 |

| 4.2 Status Entry                                                                         | 38 |

| 4.2.1 Status Entry Format                                                                |    |

| 4.2.2 stdStatus Values                                                                   |    |

| 4.3 Scatter Array                                                                        |    |

| 4.3.1 Target's Scatter-Array Elements                                                    |    |

| 4.3.2 Initiator's Scatter-Array Elements                                                 |    |

| 5. Registers and ROM Entries                                                             |    |

| 5.1 DMA Register Addressing                                                              |    |

| 5.1.1 Unit Address Spaces                                                                |    |

| 5.1.2 Control Register Structure                                                         |    |

| 5.2 Control Registers                                                                    |    |

| 5.3 Ownership Registers                                                                  |    |

| 5.4 DMA List Groups                                                                      |    |

| 5.4.1 List Groups                                                                        |    |

| 5.4.2 Unit Architectures                                                                 |    |

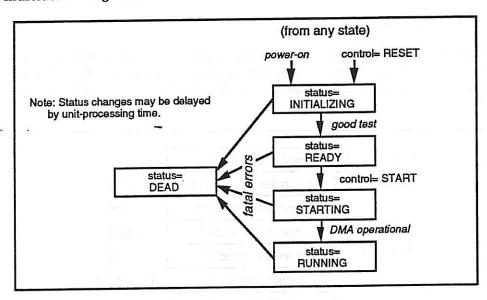

| 5.5 Internal State                                                                       |    |

| 5.6 Unit Initialization and Control                                                      |    |

| 6. Special Operations                                                                    |    |

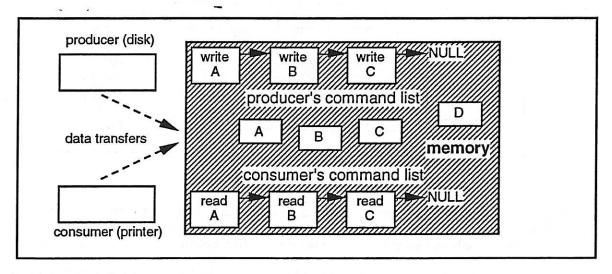

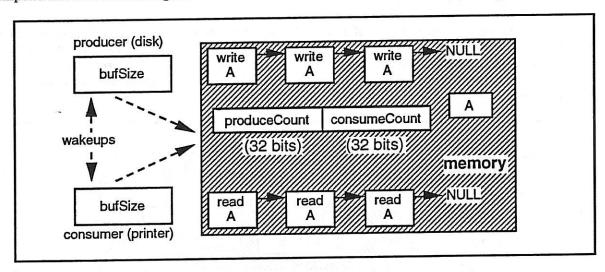

| 6.1 Dependent Data Transfers                                                             |    |

| 6.1.1 Serialized Data Transfers                                                          |    |

|                                                                                          |    |

| 6.1.2 Flow-Controlled Transfers                                                          |    |

| 6.1.3 Command-List Looping                                                               |    |

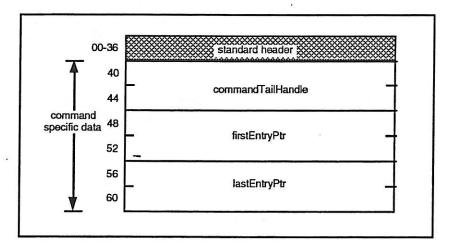

| 6.1.4 Command-List Attachments                                                           |    |

| 6.2 Supervisory Kill Command                                                             |    |

| 7. Standardized DMA Commands                                                             |    |

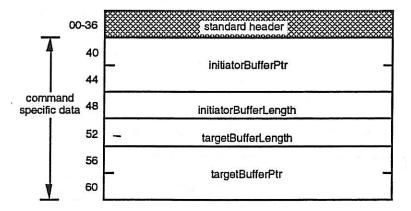

| 7.1 Read and Write Command Entries                                                       |    |

| 7.2 Copy Command Entries                                                                 |    |

| 7.3 Kill Command                                                                         |    |

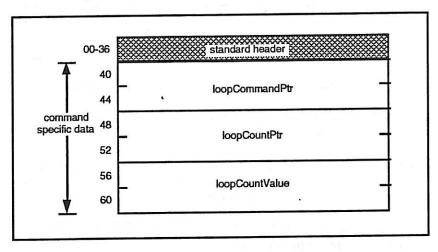

| 7.4 Loop Command                                                                         |    |

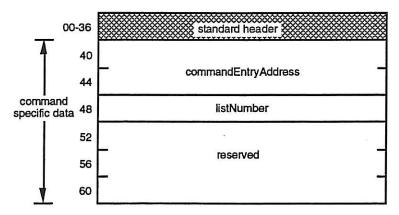

| 7.5 Attach Command                                                                       |    |

| 8. Design Alternatives                                                                   |    |

| 8.1 Direct-Mapped DMA Resources                                                          |    |

| 9. Appendix                                                                              | 60 |

| 9.1 C-Code Specification                                                                 | 60 |

| 9.1.1 Code Extraction                                                                    | 60 |

| 9.1.2 Simulation Environment                                                             | 61 |

| 9.2 Native SerialBus Adapters                                                            |    |

| 9.2.1 Address-Space Mappings                                                             |    |

| 9.2.2 Buffered Write Transactions                                                        |    |

| 9.2.3 Incoming Page Tables                                                               |    |

| 9.3 Foreign SerialBus Host Bus Adapter (HBA)                                             |    |

| 9.3.1 Processor-Initiated Accesses of SerialBus CSRs                                     | 66 |

| 9.3.2 Processor-Initiated Appending To Command Lists                                     |    |

| 9.3.3 SerialBus Transfers to HostBus-Resident System Memory                              |    |

| 9.3.4 SerialBus Appending to Host-Resident Status Lists                                  |    |

| — — — — — — — — — — — — — VV ==VVV = VVV=V440 WVWWW W4U W 111111111111111111111111111111 |    |

# CCU Architecture: D0.52 Preface X3T9.2/92-131r1: 13Aug92: 9.3.5 SerialBus Wakeup of HostBus Processors 68 9.4 List Append/Extract Overview 69 9.4.1 Appending Command-Group Entries 69 9.4.2 Appending Command-Group Entries 71

#### Preface

# Listings

| Listing 1-1: Memory-Access Routines             | 11 |

|-------------------------------------------------|----|

| Listing 2-1: Append and Extract List Operations |    |

| Listing 9-1: make_cache shell-file              |    |

| Listing 9-2: sedCmd1 sed-command files          |    |

| Listing 9-3: sedCmdc sed-file                   | 61 |

CCU Architecture: D0.52

# **Figures**

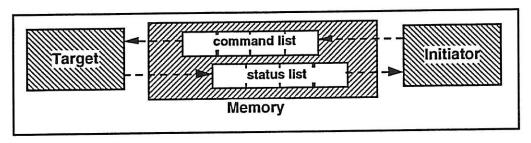

| Figure 1-1: I/O Process System Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

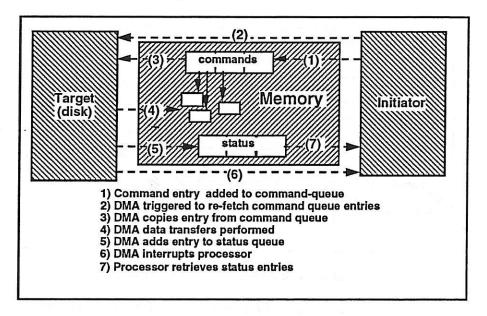

| Figure 1-2: Steps in the I/O Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4               |

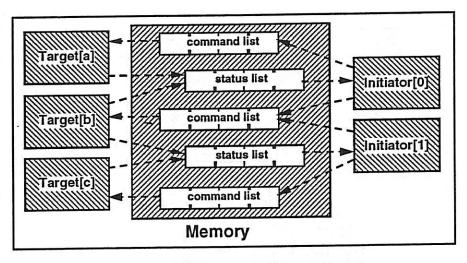

| Figure 1-3: Shared Queue Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . o             |

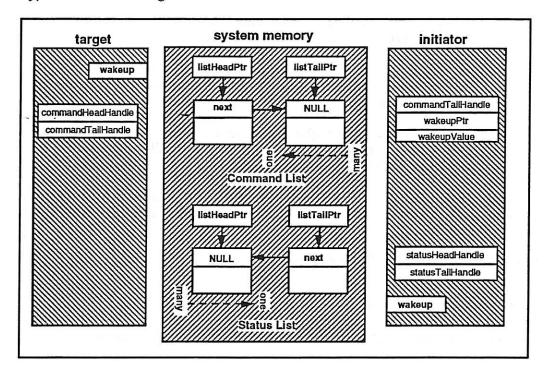

| Figure 1-4: Initiator and Target Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 4             |

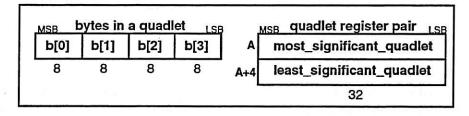

| Figure 1-5: Byte and Quadlet Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 0             |

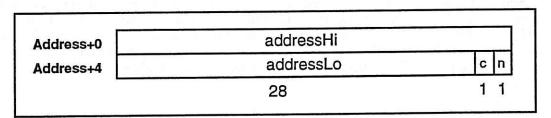

| Figure 1-6: 4/8-Byte Aligned Pointer Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . <del>છ</del>  |

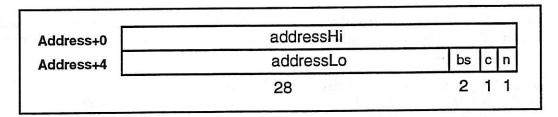

| Figure 1-7: 16-Byte Aligned Pointer Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9               |

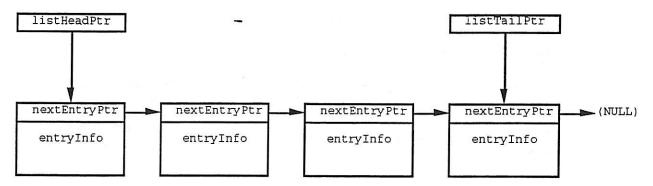

| Figure 2-1: List Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | .14             |

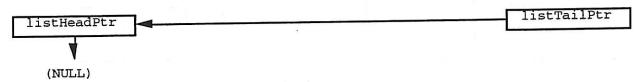

| Figure 2-2: Empty List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .10             |

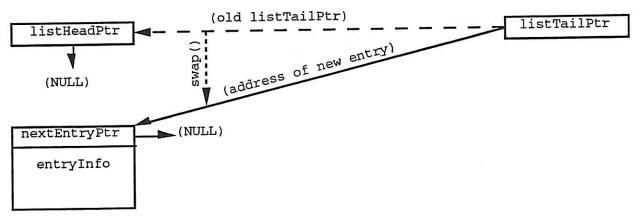

| Figure 2-3: Adding First Entry to List, Phase 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10              |

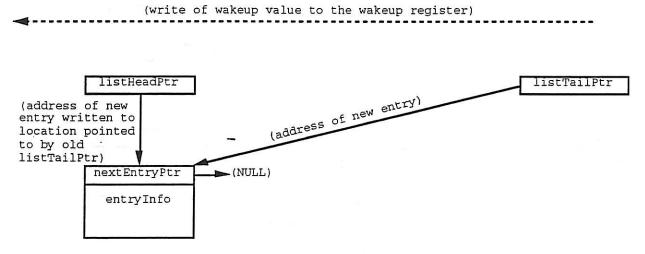

| Figure 2-4: Appending First Entry to List, Phase 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | .TO             |

| Figure 2-5: Adding a Mini-List to List. Phase 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 10            |

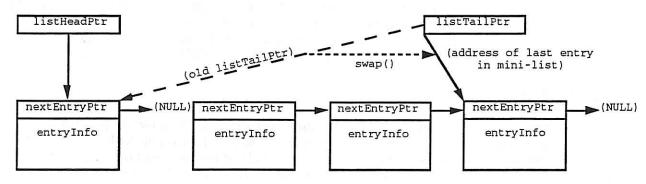

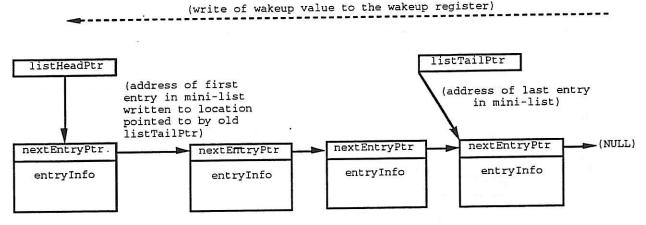

| Figure 2.6: Appending a Mini-List to List, Phase 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 17            |

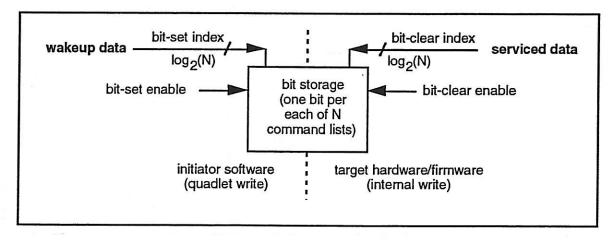

| Figure 2-7: Bit-Indexed Wakeup Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .ZZ             |

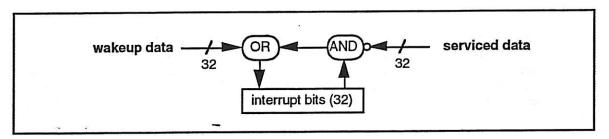

| Figure 2.8. Bit-Manned Wakeup Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .23             |

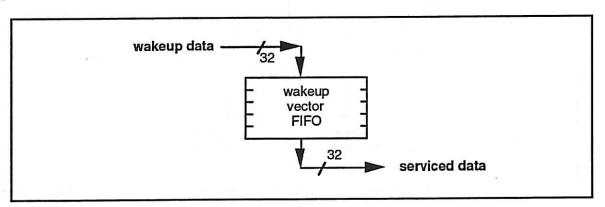

| Figure 2.0. Vector-Fife Wakeup Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Z3              |

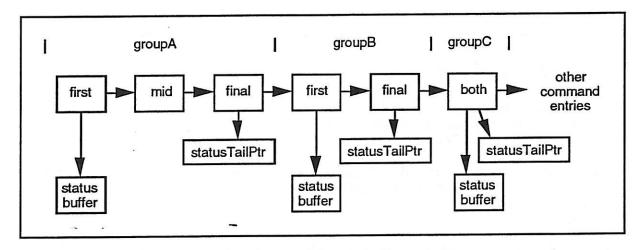

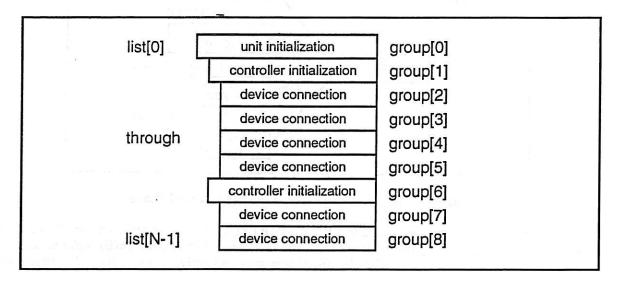

| Figure 3-1: Command-Group Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .Zo             |

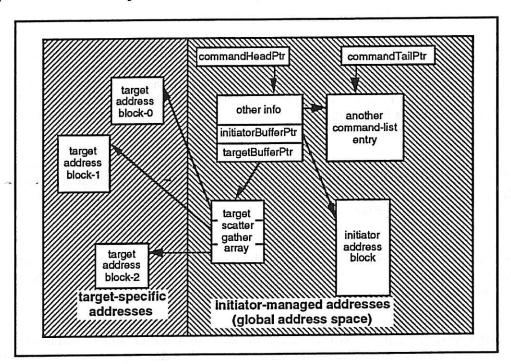

| Figure 3.2: Address-Block Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .21             |

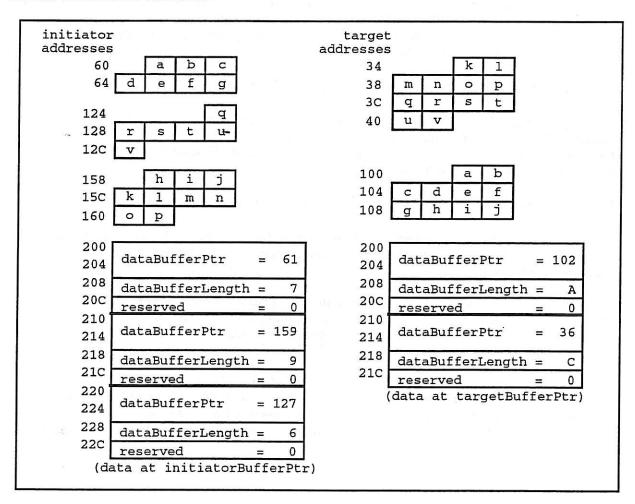

| Figure 3-3: Data Addressing, Direct-Initiator/Direct-Target Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .28             |

| Figure 3 4. Data Addressing Indirect-Initiator/Direct-Target Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 29            |

| Figure 3.5: Data Addressing Indirect-Initiator/Indirect-Target Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | .30             |

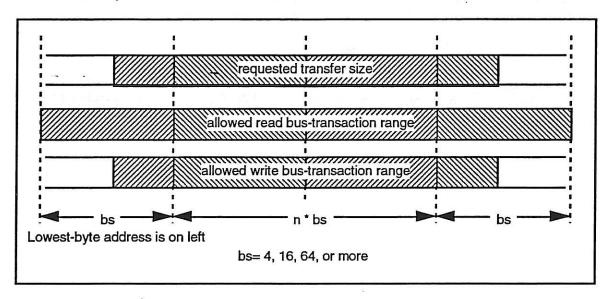

| Figure 3.6: Cross-Block Data Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .32             |

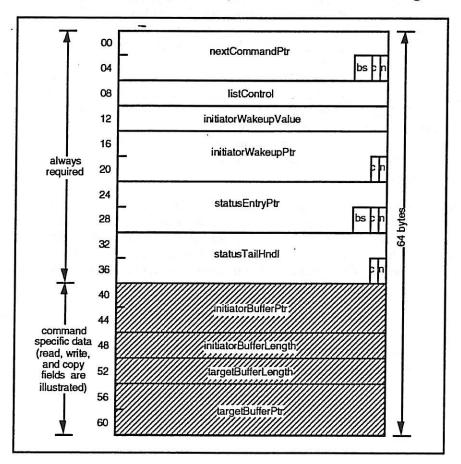

| Figure 4-1: Command Entry Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .34             |

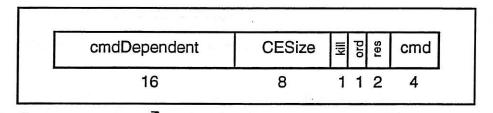

| Figure 4.2: listControl Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 30            |

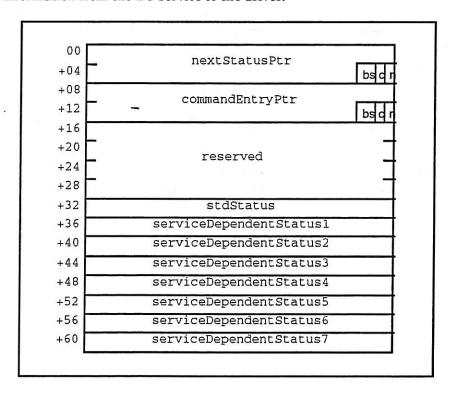

| Figure 4.2. Status Entry Fields                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .38             |

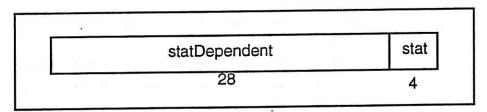

| Figure 4.4: stdStatus Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .39             |

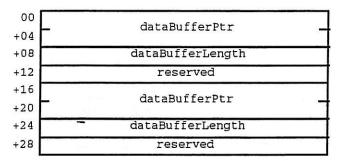

| Figure 4 5: Initiator's Scatter-Array Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .41             |

| Figure 4.6: Initiator's Scatter-Array Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .42             |

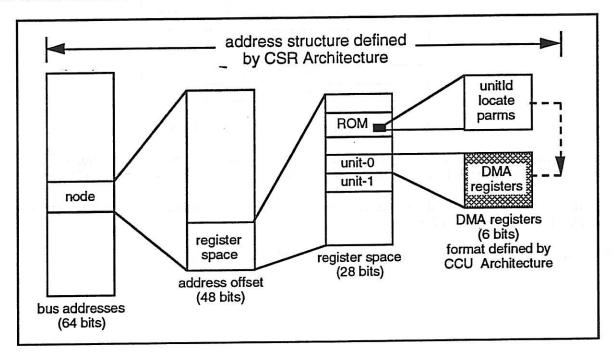

| Figure 5-1: CCII Unit Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .43             |

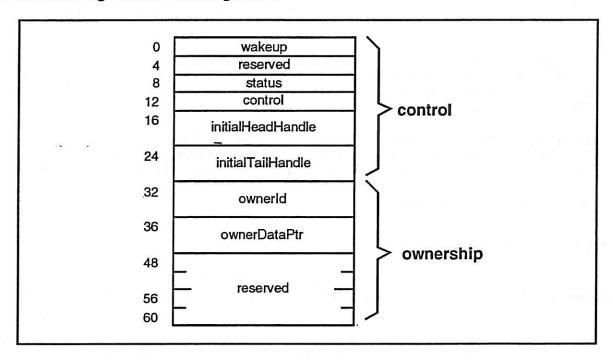

| Figure 5-2: Unit Register Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .44             |

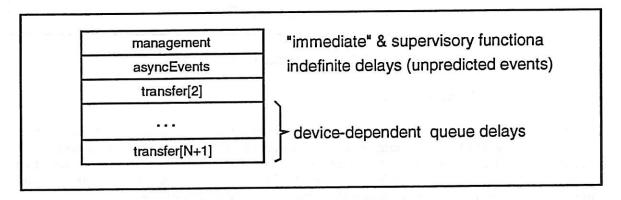

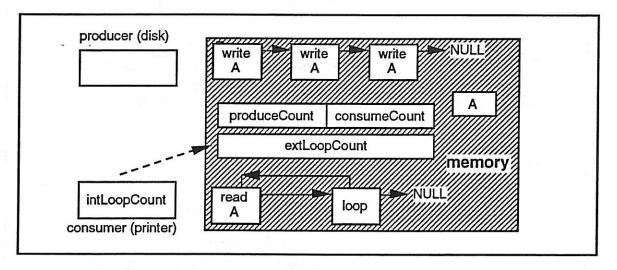

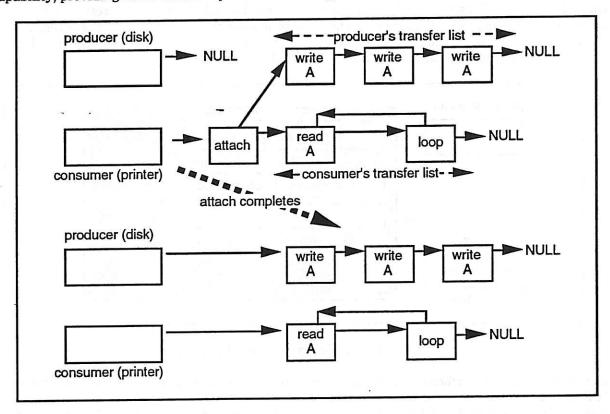

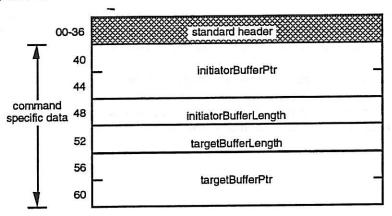

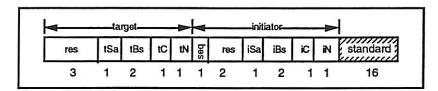

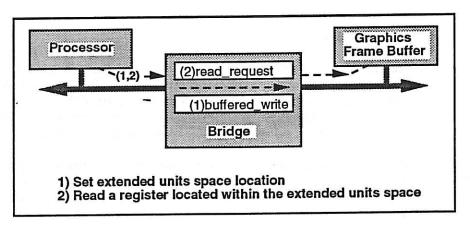

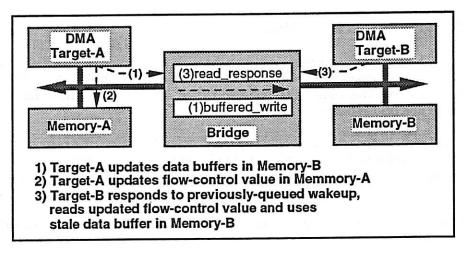

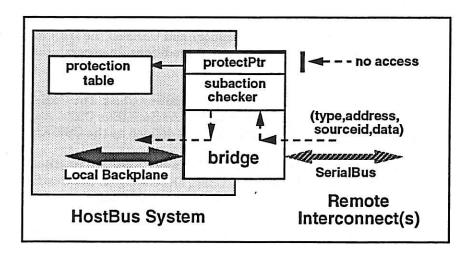

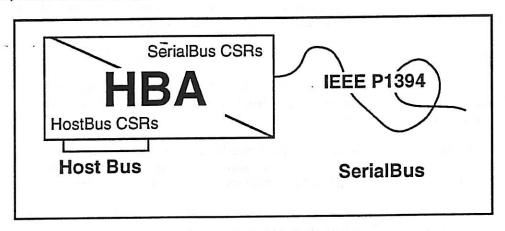

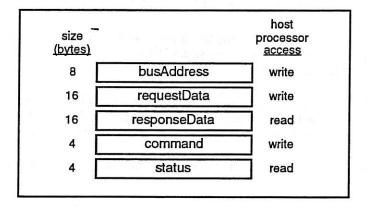

| Figure 5-3: List Group Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .40             |