# T10/99-261 r01

4420 ArrowsWest Drive Colorado Springs, CO 80907

#### 0910/0913/1999

- To: T10 Technical Committee

- From: William Petty, LSI Logic Corp.

Subj: SPI-4 Timing budget utilizing receiver signal deskew method

#### Change Control

| <u>Rev.</u> | <u>Date</u> | Description of Change                                                           |

|-------------|-------------|---------------------------------------------------------------------------------|

| 0           | 9/9/99      | Initial Document                                                                |

| 1           | 10/11/1999  | Changed 0.00 entries in spreadsheet to N.A. Removed requirement of using ATN as |

|             |             | a qualifier for deskew calibration indication. Aligned REQ/ACK timing with data |

|             |             | timing. Revised waveforms to match new transmit timing.                         |

### 1. PROPOSAL SUMMARY

In order to reach 160 mega-transfers per second while maintaining current cable lengths with viable input timing margins, a method of removing a major portion of deterministic system errors is needed. This proposal describes a method of receiver deskew that can remove most of the signal skew caused by static sources such as silicon clock balancing errors, package, board routing, and cable propagation variations. The amount removed is limited only by the resolution and calibration of the deskew hardware itself.

#### 1.1 Primary Goals

- Removal of deterministic skew errors.

- Minimize performance degradation due to calibration overhead.

#### 1.2 Assumptions

- The major sources of skew vary little over time, temperature, and voltage.

- Primary calibration need only be run during bus scan or when requested.

- Secondary calibration cycles can be hidden within the normal phase change delays.

- The use of single or multi-cycle calibration edges are allowed.

| T10/99-261r0261r1: SPI-4 Timing budget utilizing receiver | 09 <u>10</u> /09 <u>13</u> /99 | Rev. <u>1</u> 0 |

|-----------------------------------------------------------|--------------------------------|-----------------|

| deskew                                                    |                                |                 |

# 2. Supporting Data

|                 |                                                                                        | SPI-4 timing budget |                |        |

|-----------------|----------------------------------------------------------------------------------------|---------------------|----------------|--------|

|                 |                                                                                        |                     |                |        |

|                 |                                                                                        | Fast-160            | Fast-80        | Fast40 |

| Period (ns)     |                                                                                        |                     |                |        |

|                 | Basic Period                                                                           | 12.500              | 25.000         | 25.000 |

|                 | DT Period                                                                              | 6.250               | 12.500         | N.A.   |

|                 | Period Tolerance                                                                       | 0.700               | 0.700          | 0.700  |

| Static error    | sources                                                                                |                     |                |        |

|                 | Silicon TX Driver Routing Skew                                                         | 1.000               | 1.500          | 1.500  |

|                 | Package Skew (Initiator)                                                               | 0.065               | 0.065          | 0.065  |

|                 | PCB Layout Skew (Initiator)                                                            | 0.200               | 0.200          | 0.200  |

|                 | Cable Skew                                                                             | 2.500               | 2.500          | 2.500  |

|                 | PCB Layout Skew (Target)                                                               | 0.200               | 0.200          | 0.200  |

|                 | Package Skew (Target)                                                                  | 0.065               | 0.065          | 0.065  |

|                 | Silicon RX Routing Skew                                                                | 1.000               | 1.500          | 1.500  |

|                 | HL Vs LH Matching                                                                      | 0.500               | 0.500          | 0.500  |

| Dynamic er      | ror sources                                                                            |                     |                |        |

|                 | Low Vt Vs Substrate Noise                                                              | 0.200               | 0.100          | 0.100  |

|                 | Clock Jitter                                                                           | 0.250               | 0.500          | 0.500  |

|                 | Cross Talk Induced Jitter                                                              | 0.500               | 0.500          | 0.500  |

|                 | Cable Distortion ISI                                                                   | 2.000               | 2.000          | 2.000  |

|                 | Input Slew Rate Dependent Skew                                                         | 0.200               | 0.200          | 0.200  |

|                 | Receiver Amplitude Dependent Skew                                                      | 0.200               | 0.200          | 0.200  |

|                 | Self Cal Accuracy (+-100ps)                                                            | 0.200               | N.A.           | N.A.   |

| Data Valid      | Window                                                                                 | 1.850               | 2.120          | 14.270 |

| Data Setup/Hold |                                                                                        | 0.925               | 1.060          | 7.135  |

|                 |                                                                                        |                     |                |        |

|                 | <b>NOTE</b> Cable timings based on good q<br>* These values are removed by <b>Skew</b> |                     | shielded cable |        |

|                 | * Calculated Value                                                                     |                     |                |        |

|                 |                                                                                        |                     |                |        |

| <mark>)9<u>13</u>/99   Rev. <u>1</u></mark> | Ð |

|---------------------------------------------|---|

|                                             |   |

|                                             |   |

## 2.1 Deskew Requirements

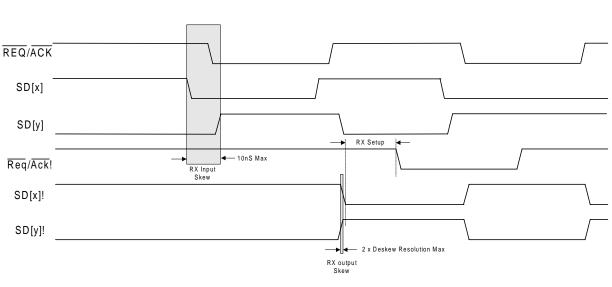

The timing diagram in Fig. 2 shows the input Vs output timing waveforms for a typical deskew circuit.

Not only can the deterministic skews be minimized, it is also easy for the internal REQ/ACK! strobe to be positioned to its optimum placement.

By using the current SPI-3 timing budget values plus an allotment for silicon based contributions a minimum of 5nS of absolute skew correction is needed. But, due to the hardware not knowing which signals will be best or worst for any given cable plant, the deskew delay generators must be capable of covering  $\pm$ 5ns for a total of 10ns of timing adjustment over temperature and process. The minimum resolution step in this 10nS delay generator is not yet defined but should be  $\leq$  100pS due to the small final setup and hold budget.

During calibration, the REQ/ACK delay generator is set to its midpoint – one setup delay and all data/parity signals are adjusted to occur line on line with the output REQ!/ACK!. After calibration is complete, the REQ/ACK delay generator is readjusted to achieve the desired setup/hold of the internal latches. These calibration values for each pin should also be available for storage and retrieval on a per connection basis.

| T10/99- <del>261r0261r1</del> : SPI-4 Timing budget utilizing receiver | <mark>09<u>10</u>/09<u>13</u>/99</mark> | Rev. <u>1</u> 0 |

|------------------------------------------------------------------------|-----------------------------------------|-----------------|

| deskew                                                                 |                                         |                 |

|                                                                        |                                         |                 |

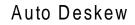

The training patterns presented to the receiver should accommodate both a single edge deskew mechanism similar to HIPPI 6400 as well as Multi-cycle techniques. It must also allow for all ISI interference to die out prior to the actual calibration edge(s). <u>Calibration is entered via counting of edges. Once the first 10 DT edges are detected, the following 20 DT edges are used for the calibration function.</u> See Fig 2 waveform below.

The multi-cycle method also has the additional capability of switching from bit write mode during the primary multi-cycle calibration to increment/decrement mode during secondary calibration cycles. These secondary cycles consist on a single calibration edge only and are used to track any subtle changes in the sources of skew. These secondary cycles should be run on a selection/re-selection basis while primary calibrations would only be run at bus scan time or when requested due to CRC errors.