September 14, 1999 Extended SCSI Addressing

T10/99-250R0

To: Members of T10 Date: September 14, 1999

From: Charles Monia/Larry Lamers

Prepared by: Charles Monia

**Subject:** Proposal for Increasing the Addressability of Parallel SCSI

**Document Number: T10/99-250R0**

Reply: ljlamers@ieee.org, cmonia@corp.adaptec.com

### 1. Overview

Recent improvements in the SCSI electrical layer combined with low cost bus extenders, increases in the synchronous data rate and a more efficient protocol have increased the load carrying capacity of the bus far beyond the combined workload presented by the maximum number of connectable devices now allowed. The ability to connect more devices therefore represents an opportunity to improve systems performance at low cost by more fully utilizing latent bus capacity.

With that in mind, this paper discusses protocol extensions that increase the addressability of the parallel SCSI bus. These protocol modifications allow extended and legacy devices to interoperate with some restrictions. The intermixed operational mode is discussed in section 7.

This proposal describes new methods for arbitration, quick arbitration and device selection. Using these methods, a 16-bit parallel SCSI bus can accommodate a maximum of 64 extended and eight legacy devices. These extensions are made practical by the Ultra160m definition, which establishes a design center based on Low Voltage Differential signaling (LVD) and a 16-bit data path. They allow the superior performance and signaling capabilities of this bus type to be fully exploited.

### 2. Reference Documents

SCSI Parallel Interface -3 (SPI-3), Revision 7, dated 3-June-1999 (T10 project 1302D), referred to in this document as SPI-3.

# 3. Extended SCSI Addressing

An extended SCSI address consists of two components – a group I/D (GID) and group member I/D (MID). The format and associated priority of each address element is shown in Table 1 and Table 2. As described in section 4, each component forms the basis for a two-cycle arbitration scheme in which each address element is asserted on the data bus during a given cycle and tested by contending devices to determine the ultimate winner.

An extended device has a GID in the range of 0 through 7 and a MID in the range 8 through 15. The GID/MID combination must be unique. Since eight groups are allocated and each group may have up to eight members, up to 64 extended devices may be attached to the bus.

A legacy device address consists of a group address in the range of 0 through 15. Legacy devices do not have a MID component. As discussed in section 7, legacy and extended devices may not share a GID. Consequently, a legacy device with a GID in the range 0 through 7 will be the sole user of a GID that could have been shared by up to eight extended devices.

Table 1 -- Group I/D Arbitration Priority

| Group<br>I/D | DB<br>15 | Legacy devices only |   |   |   |   | DB<br>8 | DB<br>7 | Legacy or extended devices |   |   |   |   | DB<br>0 | Priority |   |    |

|--------------|----------|---------------------|---|---|---|---|---------|---------|----------------------------|---|---|---|---|---------|----------|---|----|

| 7            | -        | -                   | - | - | - | - | -       | -       | 1                          | - | - | - | - | -       | -        | - | 1  |

| 6            | -        | -                   | - | - | - | - | -       | -       | -                          | 1 | - | - | - | -       | -        | - | 2  |

| 5            | -        | -                   | - | - | - | - | -       | -       | -                          | - | 1 | - | - | -       | -        | - | 3  |

| 4            | -        | -                   | - | - | - | - | -       | -       | -                          | - | - | 1 | - | -       | -        | - | 4  |

| 3            | -        | -                   | - | - | - | - | -       | -       | -                          | - | - | - | 1 | -       | -        | - | 5  |

| 2            | -        | -                   | - | - | - | - | -       | -       | -                          | - | - | - | - | 1       | -        | - | 6  |

| 1            | -        | -                   | - | - | - | - | -       | -       | -                          | - | - | - | - | -       | 1        | - | 7  |

| 0            | -        | -                   | - | - | - | - | -       | -       | -                          | - | - | - | - | -       | -        | 1 | 8  |

| 15           | 1        | -                   | - | - | - | - | -       | -       | -                          | - | - | - | - | -       | -        | - | 9  |

| 14           | -        | 1                   | - | - | - | - | -       | -       | -                          | - | - | - | - | -       | -        | - | 10 |

| 13           |          | -                   | 1 | - | - | - | -       | -       | -                          | - | - | - | - | -       | -        | - | 11 |

| 12           |          | -                   | - | 1 | - | - | -       | -       | -                          | - | - | - | - | -       | -        | - | 12 |

| 11           |          | -                   | - | - | 1 | - | -       | -       | -                          | - | - | - | - | -       | -        | - | 13 |

| 10           | -        | -                   | - | - | - | 1 | -       | -       | -                          | - | - | - | - | -       | -        | - | 14 |

| 9            | -        | -                   | - | - | - | - | 1       | -       | _                          | - | - | - | - | -       | -        | - | 15 |

| 8            |          | -                   | - | - | - | - | -       | 1       | -                          | - | - | - | - | -       | -        | - | 16 |

Table 2 - Member I/D Arbitration Priority

| Member<br>I/D | DB<br>15 | Extended devices only |   |   |   |   |   | DB<br>8 | DB<br>7 | Unused |   |   |   |   | DB<br>0 | Priority |   |

|---------------|----------|-----------------------|---|---|---|---|---|---------|---------|--------|---|---|---|---|---------|----------|---|

| 15            | 1        | -                     | - | - | - | - | - | -       | -       | -      | - | - | - | - | -       | -        | 1 |

| 14            | -        | 1                     | - | - | - | - | - | -       | -       | -      | - | - | - | - | -       | -        | 2 |

| 13            |          | -                     | 1 | - | - | - | - | -       | -       | -      | - | - | - | - | -       | -        | 3 |

| 12            |          | -                     | - | 1 | - | - | - | -       | -       | -      | - | - | - | - | -       | -        | 4 |

| 11            |          | -                     | - | - | 1 | - | - | -       | -       | -      | - | - | - | - | -       | -        | 5 |

| 10            | -        | -                     | - | - | - | 1 | - | -       | -       | -      | - | - | - | - | -       | -        | 6 |

| 9             | -        | -                     | - | - | - | - | 1 | -       | -       | -      | - | - | - | - | -       | -        | 7 |

| 8             |          | -                     | - | - | - | - | - | 1       | -       | -      | - | - | - | - | -       | -        | 8 |

## 4. Extended Addressing Protocol

The methods described below define a two-round elimination scheme for arbitration and quick arbitration. During the first round, each contesting device asserts its GID and tests to see if it is still in contention. Extended devices sharing the highest priority GID on the first round, assert their MIDs and enter a second round of competition. The winner is the device with the highest priority MID.

Legacy devices only compete on the first round. If a legacy device wins, it begins selection as described in section 7; otherwise it drops out of contention.

The following sections describe the processes in detail.

## 4.1 Overview of Extended Arbitration

After detecting a bus free condition (SEL and BSY false), devices wishing to arbitrate begin by asserting their group IDs. During the initial cycle all arbitrating devices sample the data bus to determine whether or not they have lost.

Devices still in contention assert SEL and BSY and continue to assert their SCSI IDs. All losing devices, including all lower priority legacy devices, are required to drop out of contention.

If a legacy device wins arbitration, it performs selection as described in section 7. If one or more extended devices win, they begin the second arbitration cycle by asserting their MIDs. At this point, devices still in contention sample the bus once again. This time, the device with the highest priority group member ID wins and asserts C/D. As in the first arbitration cycle, the remaining devices must determine that they have lost and stop driving all signals.

## 4.2 Extended Arbitration -- Details

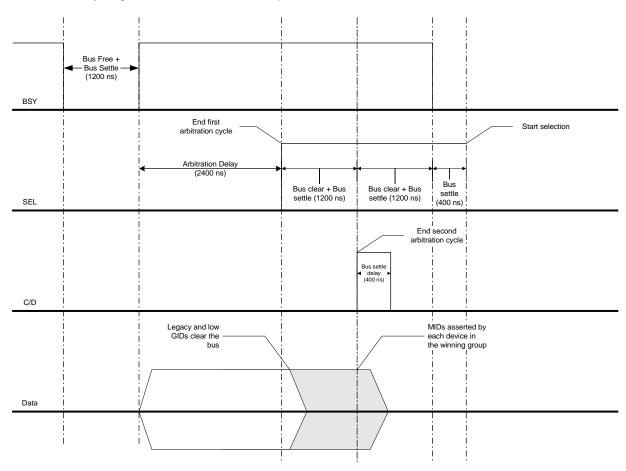

A device arbitrates for the bus as described below. The timing sequence is shown in Figure 1.

- a) The SCSI device shall first wait for the BUS FREE phase to occur. The BUS FREE phase is detected whenever both the BSY and SEL signals are simultaneously and continuously false for a minimum of a bus settle delay.

- b) The SCSI device shall wait a minimum of a bus free delay after detection of the BUS FREE phase (i.e. after the BSY and SEL signals are both false for a bus settle delay) before driving any signal.

- c) Following the bus free delay in step (b), the SCSI device may arbitrate for the SCSI bus by asserting the BSY signal and its own group I/D. However the SCSI device shall not arbitrate (i.e. assert the BSY signal and its GID) if more than a bus set delay has passed since the BUS FREE phase was last observed.

- d) After waiting at least an arbitration delay (measured from its assertion of the BSY signal) the SCSI device shall examine the DATA BUS. The device has lost arbitration if a higher priority group I/D is present on the bus.

- e) An SCSI device that has not lost arbitration during the first cycle, shall assert the SEL signal and shall continue to assert BSY and its SCSI I/D.

- An SCSI device that has lost shall release the BSY signal and its SCSI ID within a bus clear delay after the SEL signal becomes true. The device may return to step (a).

- f) After waiting at least a bus clear plus a bus settle delay from the assertion of SEL, the device shall examine the data bus. If no higher priority group member ID is present on the DATA BUS, then the SCSI device has won the arbitration and it shall assert the C/D signal.

- Any SCSI device other than the winner has lost the arbitration and shall release the BSY signal, the SEL signal and its SCSI ID within a bus clear delay after the C/D signal becomes true. An SCSI device that loses arbitration may return to step (a).

- g) After waiting at least a bus settle delay from the assertion of C/D, the device that has won arbitration shall release C/D. After waiting at least a bus clear delay from its release of C/D, the device may begin the extended selection phase.

Figure 1 -- Arbitration Timing

## 4.3 Extended QaS

The QaS arbitration protocol reduces overhead by allowing a target to transfer control of the bus to a new device without going through the bus free phase.

A target signals the beginning of quick arbitration to all QaS-enabled devices by means of the handshake defined in SPI-3 (see SPI-3, clause 10.2.2.1). After starting QaS, the target continues to assert BSY until QaS completes as described below.

During the initial arbitration cycle, contending devices assert their group and group member I/Ds. After a delay, all arbitrating devices examine the bus. Those having a lower priority group I/D drop out of contention by deasserting all signals. The remaining devices assert SEL and continue to drive their extended SCSI I/Ds.

The assertion of SEL triggers the start of the second arbitration cycle and signals all devices having a lower group I/D to drop out of contention. After an appropriate delay to allow losing devices to clear the bus, devices still in contention sample the data bus again. The winning device asserts C/D to indicate the completion of the second arbitration cycle. Lower priority devices must drop out of contention within a given time of C/D becoming true. The winning device then negates C/D and releases all other signals.

On detecting the assertion of C/D, the target waits long enough to allow transients to settle and losing devices to clear the bus. It then terminates QaS arbitration by deasserting BSY. Following deassertion of BSY, the winning device performs extended selection as described in section 5.

## 4.3.1 Details of Extended QaS

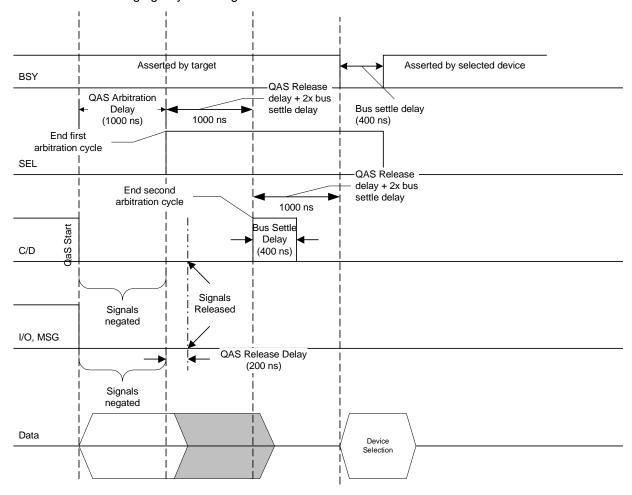

The following detailed description is derived from the QaS protocol specified in clause 10.2.2.1 of the SPI-3 document. Procedures are given specifying the behavior of the target releasing the bus and a device wishing to gain control of the bus. QaS timing is shown in Figure 2.

## 4.3.1.1 Extended QaS -- Target releasing the bus

The following steps are performed when a QaS-enabled target terminates a connection with a QaS-enabled initiator. This procedure signals the start of QaS arbitration and passes control of the bus from the target to the winning device.

- a) The target shall change to a MESSAGE IN phase and issue a single QA REQUEST (55h) message. The target shall assert REQ for a minimum of 16 ns. The current initiator shall assert the ACK signal for a minimum of 16 ns in responding. The target shall hold the message byte for a minimum of 33 ns after detection of the ACK signal being asserted.

- b) After the initiator negates the ACK signal for the QAS REQUEST message and if the initiator does not create an attention condition then the initiator shall release all SCSI signals within two system deskew delays after detecting MSG, C/D, and I/O signals false.

- c) After detection of the last ACK signal being false and if there is no attention condition, the target shall release all SCSI signals except the BSY, MSG, C/D and I/O signals and the target shall negate the MSG, C/D, and I/O signals within two system deskew delays.

- d) If the target detects the SEL signal being true, the target shall release the MSG, C/D and I/O signals within one QAS release delay.

- e) After waiting at least a QAS arbitration delay from releasing the SCSI signals in step (c), if there are no SCSI ID bits true, the target shall transition to the BUS FREE phase.

- f) After waiting at least a QAS arbitration delay from releasing of the SCSI signals in step (c), if there are any SCSI ID bits asserted the target shall wait at least a second QAS arbitration delay. If the SEL signal is not asserted by the end of the second QA arbitration delay, the target shall transition to the BUS FREE phase.

- g) The target shall wait for the C/D signal to be asserted.

- h) After waiting at least a QAS release delay plus two times the bus settle delay from detecting the assertion of the C/D signal in step (g), the target shall release the BSY signal.

# 4.3.1.2 Extended QaS -- Device arbitrating for the bus

The following procedure applies to a QaS-enabled device that wishes to arbitrate for the bus.

- a) The SCSI device may arbitrate for the SCSI bus by asserting its own SCSI ID within a QAS assertion delay from detection of the MSG, C/D, and I/O signals being negated (see section 4.3.1.1, step (c).

- b) After waiting at least a QAS arbitration delay (measured from the detection of the MSG, C/D, and I/O signals being negated) the SCSI device shall examine the DATA BUS.

- A) If no higher priority group I/D is true on the DATA BUS, then the SCSI device is still in contention and it shall assert the SEL signal.

- B) If a higher priority group I/D is present on the DATA BUS (see section 3 for the SCSI ID arbitration priorities), then the SCSI device has lost the arbitration. All devices that have lost the arbitration shall release their SCSI IDs after two deskew delays and within one QA release delay after detection of the SEL signal being asserted. An SCSI device that loses arbitration may return to step (a).

- c) The SCSI devices still in contention shall wait at least a QAS arbitration delay. A device still in contention shall examine the DATA BUS. If a higher priority group member I/D is present on the bus, then the SCSI device has lost arbitration. If no higher priority group member I./D is present on the bus, then the device has won arbitration.

- d) The device that has won arbitration shall assert the C/D signal. After a bus settle delay following the assertion of C/D, the device shall negate the C/D signal. The device shall release (stop driving) C/D within one QAS release delay of its being negated.

- e) The device that has lost arbitration shall release all signals after two deskew delays and within one QAS release delay after detecting the assertion of C/D.

- f) The SCSI device that has won arbitration shall wait at least a QAS arbitration delay after asserting C/D before changing any other signals.

Figure 2 -- Extended QAS Timing

### 5. Extended Selection

To participate in selection, all extended devices are required to listen during each arbitration or quick arbitration cycle to determine the SCSI ID of the winning device. The inclusive OR of this value and the device's SCSI I/D are saved in a selection mask register internal to the device. A device determines that it has been selected by referencing this information during the selection phase.

Note: The ability to snoop the bus during arbitration is required for devices that implement the fair arbitration policy described in section 6.

# 5.1 Monitoring bus activity during arbitration

The listening device monitors the bus as follows:

- a) The device shall first wait for the BUS FREE phase to occur. The BUS FREE phase is detected whenever both the BSY and SEL signals are simultaneously and continuously false for a minimum of a bus settle delay.

- b) After detecting the BUS FREE condition, the listening device shall continuously monitor the BSY signal. If BSY is asserted, the listening device shall begin sampling the data bus. Sampling shall stop after C/D is asserted. The device shall save the bus I/D of the winning device.

- c) The device shall set its selection mask to the inclusive OR of its SCSI ID and the SCSI ID of the winning device.

## 5.2 Monitoring Bus Activity during quick arbitration

Listening devices observe the bus as follows:

- a) The listening device detects the start of Quick Arbitration as described in section 4.3.1.1

- b) After waiting for a QAS arbitration delay, the device begins sampling the data bus continuously.

- c) When C/D is asserted, the device shall stop sampling and save the bus I/D of the winning device.

- d) The device shall set its selection mask to the inclusive OR of its SCSI ID and the SCSI ID of the winning device.

### 5.3 Extended Selection Phase

During the selection phase, the selecting device asserts a bit mask corresponding to its SCSI ID inclusively ORed with the SCSI ID of the device to be selected.

A device shall determine that it is selected when

- a) The SEL signal is true and the BSY and I/O signals are false for at least a bus settle delay and

- b) The data bus is equal to the selection mask register. Parity must be valid.

The selected target shall then assert the BSY signal within a selection abort time of its most recent detection of being selected; this is required for correct operation of the selection time-out procedure.

A device that supports extended addressing shall not respond to selection if:

- a) Parity is invalid or

- b) More than four or less than three data bits are set.

#### 5.4 Extended Reselection

The reselection protocol is similar to the above, except that the I/O signal is true.

## 6. Extended Addressing Fairness

### 6.1 Model for Extended Devices

In this extended version of fairness, each device supporting fair arbitration implements group and group member fairness registers. When an SCSI device does not need to arbitrate for the SCSI bus, it monitors the arbitration attempts of the other SCSI devices and updates its fairness registers as follows.

- a) During the first arbitration cycle, each listening device records in its group fairness register all asserted group I/Ds whose priority is equal to or less than the listening device.

- b) If the winning group I/D in step (a) is at or below the priority of the device, it updates its group member fairness register with the MID of each lower priority device in the winning group (relative to the listening device) that has lost arbitration during the second cycle. (If a legacy device wins arbitration during the first cycle, the contents of the group member fairness register are set to 0.)

Whenever a requirement for arbitration arises, the device first checks to see if both of its fairness registers are clear. If so, this SCSI device may now participate in arbitration. If the fairness registers are not clear, the SCSI device postpones arbitration until all lower priority group and group member I/Ds have been cleared from the fairness registers as described below.

A device that is waiting to arbitrate shall update its fairness registers as follows:

- a) Group IDs are cleared from the group fairness register as all contending devices in those groups either win or withdraw from arbitration.

- b) Lower priority group member I/Ds are cleared from the group member I/D register as lower priority devices in that group win arbitration.

To prevent low priority devices from holding off a high priority device indefinitely, new member and group I/Ds are added to the fairness registers only when the SCSI device wins or is not waiting to arbitrate. Other lower priority SCSI devices that decided to arbitrate after the waiting device will therefore not indefinitely inhibit that device from attempting to arbitrate.

# 6.2 Fairness for Legacy Devices

The method described above is compatible with the fairness scheme implemented by legacy devices. Such devices will update their fairness registers during the first arbitration cycle and automatically defer to devices in lower priority groups. Conversely, extended devices will detect and defer to arbitration attempts by lower priority legacy devices.

Since legacy devices do not recognize the second arbitration cycle, however, such devices should not have a group I/D that exceeds the priority of an extended device.

# 6.3 Fairness Behavior for Extended Addressing

The fairness policy for extended addressing deviates from fairness as implemented in legacy SCSI. Under the circumstances described below, a lower priority device can preempt a higher priority device for a single arbitration cycle.

This preemption occurs whenever devices from several lower priority groups are in contention for the bus. Under these circumstances, higher priority devices cannot discover which group members to defer to until one of the lower priority groups wins and enters the second arbitration cycle. Consequently, a device in a lower priority group that decides to arbitrate after other devices in its peer group, may preempt devices in higher priority groups for one round of arbitration.

The effect on arbitration latency is similar to a service queue in which members closer to the head of the queue may allow a limited number of new arrivals to cut into line. In this case, the new arrivals are not detected until they reach the head of the queue. Once detected, of course, no further preemption is allowed.

#### 6.4 Fairness for Normal Arbitration

[A detailed description is TBS]

# 6.5 Fairness for quick arbitration method

[A detailed description is TBS]

## 7. Mixing legacy and extended addressing modes

The following sections describe how legacy and extended address devices can interoperate on the same bus. The only restriction is that a device in legacy mode cannot use Quick Arbitrate and Select.

This proposal assumes that a SCSI-compliant legacy device will:

- Automatically drop out of contention during arbitration when it sees SEL+BSY set at the end of the first arbitration cycle.

- b) Not respond to an extended selection phase in which more than two data bits are set.

As discussed previously, up to eight legacy devices and 64 extended address devices can be supported. Each initiator must have two addresses: a legacy address used for selection and reselection consisting of a single, bit significant value in the range of 0 - 15, and an extended address used for arbitration and extended selection.

Device I/Ds are assigned so that at least three data bits are asserted during an extended selection or reselection and two when selection or reselection is performed with a legacy device. An initiator probes for legacy devices by performing a series of selections using a single target I/D bit.

In this case, the following behaviors are required:

- a) With either addressing method, extended address targets shall not respond to selection if the number of data bits asserted is less than three or parity is incorrect.

- As required by the SCSI specification, legacy targets shall not respond to selection if more than two data bits are asserted or parity is incorrect. (The degree to which existing devices comply with this requirement is unknown.)

An initiator would select a legacy device by asserting the initiator's group I/D along with the member I/D of the target device. A legacy device would perform reselection in the same manner. During reselection, the assertion of only two data bits enables the initiator to detect and respond to a legacy device while at the same time inhibiting a response from an extended device.

An initiator would select an extended target by asserting its group and member I/Ds along with those of the target device. Since at least three data bits must be asserted, a compliant legacy device will not respond.

#### 8. Issues

- Devices that use the SCA-2 connector today pick up their SCSI ID from the encoded value on the connector. Investigation is needed into how such a device would automatically detect and operate in extended mode while retaining the ability to be connected to a legacy bus.

- 2) Bus loading and configuration rules need to be specified for systems that support extended addressing.

- 3) Expanders will probably be needed for bus loading considerations so they would have to support the new arbitration and selection methods.

- Since multiple devices will be asserting SEL, this signal may require filtering to remove release glitches.

# 9. Bus control timings

The bus control timings used in this document are listed in Table 2. These values are extracted from SPI-3, table 29.

Table 2 -- SCSI bus control timing values

| Timing description    | Timing values |

|-----------------------|---------------|

| Arbitration delay     | 2.4 μs        |

| Bus Clear Delay       | 800 ns        |

| Bus Free Delay        | 800           |

| Bus Set Delay         | 1.6 us        |

| Bus Settle Delay      | 400 ns        |

| QAS Arbitration Delay | 1000 ns       |

| QAS Assertion Delay   | 200 ns        |

| QAS Release Delay     | 200 ns        |

| Selection Abort Time  | 200 μs        |

| System Deskew Delay   | 45 ns         |