**Seagate Technology**

10323 West Reno (West Dock) Oklahoma City, OK 73127-9705 P.O. Box 12313

Oklahoma City, OK 73157-2313

Tel: 405-324-3070 Fax: 405-324-3794

gene\_milligan@notes.seagate.com

9/15/98

John Lohmeyer Chairman T10

Subject: Revision 6 of the Proposal for the Fast 80 Specifications in the SPI-3 Standard

The SPI-3 T10 working group meeting reviewed revision 5 and marked it up with changes to be made as agreed to in the meeting. The working group meeting recommended that revision 5 as marked up be incorporated into SPI-3. Revision 6 incorporates the mark-ups made in the meeting.

Gene E. Milligan Director, Development Strategy

Attachment: Fast 80 Draft for SPI-3 Revision 6 by PDF.

# 1 SCSI parallel bus timing

Unless otherwise indicated, the delay-time measurements for each SCSI device, shown in table 1, shall be calculated from signal conditions existing at that SCSI device's port. Thus, these measurements (except cable skew) may be made without considering delays in the cable. The timing characteristics of each signal are described in the following paragraphs. Timing requirements relating to glitches are defined in clause 7.2.4.1.

Table 1 - SCSI bus control timing values

| Timing description                | Timing values |

|-----------------------------------|---------------|

| Arbitration Delay                 | 2,4 µs        |

| Bus Clear Delay                   | 800 ns        |

| Bus Free Delay                    | 800 ns        |

| Bus Set Delay                     | 1,6 µs        |

| Bus Settle Delay                  | 400 ns        |

| Cable Skew (note 1)               | 4 ns          |

| Data Release Delay                | 400 ns        |

| Disconnection Delay               | 200 us        |

| Power on to Selection (note 2)    | 10 s          |

| Reset Hold Time                   | 25 µs         |

| Reset to Selection (note 2)       | 250 ms        |

| Selection Abort Time              | 200 µs        |

| Selection Time-out Delay (note 2) | 250 ms        |

| System Deskew Delay               | 45 ns         |

| Notes:                            |               |

- 1 <u>Cable Skew is measured at each device</u> <u>connection with the transmitted skew sub-</u> <u>tracted from the received skew.</u>

- 2 This is a recommended time. It is not mandatory.

Table 2 - SCSI bus data & information phase Single Transition timing values

|                                                                  | Timing values (note 5) |        |         |         |         |

|------------------------------------------------------------------|------------------------|--------|---------|---------|---------|

| Timing description                                               | Asynch                 | Fast-5 | Fast-10 | Fast-20 | Fast-40 |

| Cable Skew (note 1)                                              | 4 ns                   | 4 ns   | 4 ns    | 3 ns    | 2.5 ns  |

| Receive Assertion Period (note 2)                                | N/A                    | 70 ns  | 22 ns   | 11 ns   | 6,5 ns  |

| Receive Hold Time (note 2 and note 3)                            | N/A                    | 25 ns  | 25 ns   | 11,5 ns | 4,75 ns |

| Receive Negation Period (note 2)                                 | N/A                    | 70 ns  | 22 ns   | 11 ns   | 6,5 ns  |

| Receive Setup Time (note 2 and note 3)                           | N/A                    | 15 ns  | 15 ns   | 6,5 ns  | 4,75 ns |

| Receive Period Tolerance                                         | N/A                    | 1.1 ns | 1.1 ns  | 1.1 ns  | 1.1 ns  |

| Signal Timing Skew (note 1)                                      | 8 ns                   | 8 ns   | 8 ns    | 5 ns    | 4,5 ns  |

| Transfer Period during Synchronous Data Transfer Phases (note 4) | N/A                    | 200 ns | 100 ns  | 50 ns   | 25 ns   |

| Transmit Assertion Period (note 2)                               | N/A                    | 80 ns  | 30 ns   | 15 ns   | 8 ns    |

| Transmit Hold Time (note 2 and note 3)                           | N/A                    | 53 ns  | 33 ns   | 16,5 ns | 9,25 ns |

| Transmit Negation Period (note 2)                                | N/A                    | 80 ns  | 30 ns   | 15 ns   | 8 ns    |

| Transmit Setup Time (note 2 and note 3)                          | N/A                    | 23 ns  | 23 ns   | 11,5 ns | 9,25 ns |

| Transmit Period Tolerance                                        | N/A                    | 1 ns   | 1 ns    | 1 ns    | 1 ns    |

- 1 <u>Cable Skew is measured at each device connection with the transmitted skew subtracted from the received skew.</u>

- 2 See 1.2 for measurement points for the timing specifications.

- 3 See 1.3 for examples of how to calculate setup and hold timing.

- 4 The transfer period is measured from an assertion edge of <a href="the-REQ/REQQ">the-REQ/REQQ</a> (ACK/ACKQ) signal to the next assertion edge of the <a href="REQ/REQQ">REQQ</a> (ACK/ACKQ) signal.

- 5 SCSI bus timing values specified by the maximum transfer rate <u>for the given range</u> shall apply even if a slower transfer rate <u>within the given range</u> is negotiated.

Table 3 - SCSI bus data & information phase Double Transition timing values

| The land of the same of the sa | Timing Values (note 5) |         |         |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------|---------|---------|

| Timing description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Fast-10                | Fast-20 | Fast-40 | Fast-80 |

| Cable Skew (note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4 ns                   | 3 ns    | 2.5 ns  | 2.5 ns  |

| Receive Assertion Period (note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80 ns                  | 40 ns   | 20 ns   | 10 ns   |

| Receive Hold Time (note 2 and note 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25 ns                  | 11,5 ns | 4,75 ns | 1,45 ns |

| Receive Negation Period (note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80 ns                  | 40 ns   | 20 ns   | 10 ns   |

| Receive Setup Time (note 2 and note 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25 ns                  | 11,5 ns | 4,75 ns | 1,45 ns |

| Receive REQ/REQQ (ACK/ACKQ) Period Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0,7 ns                 | 0,7 ns  | 0,7 ns  | 0,7 ns  |

| Signal Timing Skew (note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26,3 ns                | 13.3 ns | 6,8 ns  | 3,35 ns |

| Transfer REQ/REQQ (ACK/ACKQ) Period during Synchronous Data Transfer Phases (note 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 200 ns                 | 100 ns  | 50 ns   | 25 ns   |

| Transmit Assertion Period (note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 90 ns                  | 45 ns   | 22,5 ns | 11,5 ns |

| Transmit Hold Time (note 2 and note 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37 ns                  | 18,5 ns | 9,25 ns | 4,8 ns  |

| Transmit Negation Period (note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90 ns                  | 45 ns   | 22,5 ns | 11,5 ns |

| Transmit Setup Time (note 2 and note 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37 ns                  | 18,5 ns | 9,25 ns | 4,8 ns  |

| Transmit REQ/REQQ (ACK/ACKQ) Period Tolerance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0,6 ns                 | 0,6 ns  | 0,6 ns  | 0,6 ns  |

- 1 <u>Cable Skew is measured at each device connection with the transmitted skew subtracted from the received skew.</u>

- 2 See 1.2 for measurement points for the timing specifications.

- 3 See 1.3 for examples of how to calculate setup and hold timing.

- 4 The transfer REQ/REQQ (ACK/ACKQ) period is measured from an assertion edge of the REQ/REQQ (ACK/ACKQ) signal to the next assertion edge of the signal. The nominal data transfer period is half that of the transfer period since data is qualified on both the assertion and negation edges of the REQ/REQQ (ACK/ACKQ) signal.

- 5 SCSI bus timing values specified by the maximum transfer rate <u>for the given range</u> shall apply even if a slower transfer rate<u>within the given range</u> is negotiated.

# 1.1 Timing description

### 1.1.1 Arbitration delay

The minimum time an SCSI device shall wait from asserting the BSY signal for arbitration until the DATA BUS is examined to see if arbitration has been won. There is no maximum time.

### 1.1.2 Bus clear delay

The maximum time for an SCSI device to release all SCSI bus signals after:

- a) the BUS FREE phase is detected (the BSY and SEL signals are both false for a bus settle delay);

- b) the SEL signal is received from another SCSI device during the ARBITRATION phase;

- c) the transition of the RST signal to true.

For item a) above, the maximum time for an SCSI device to release all SCSI bus signals is 1200 ns from the BSY and SEL signals first becoming both false. If an SCSI device requires more than a bus settle delay to detect BUS FREE phase, it shall release all SCSI bus signals within a bus clear delay minus the excess time.

### 1.1.3 Bus free delay

The minimum time that an SCSI device shall wait from its detection of the BUS FREE phase (BSY and SEL both false for a bus settle delay) until its assertion of the BSY signal in preparation for entering the ARBITRATION phase.

### 1.1.4 Bus set delay

The maximum time for an SCSI device to assert the BSY signal and its SCSI ID after it detects a BUS FREE phase for the purpose of entering the ARBITRATION phase.

#### 1.1.5 Bus settle delay

The minimum time to wait for the bus to settle after changing certain control signals as called out in the protocol definitions.

#### 1.1.6 Cable skew

The maximum difference in propagation time allowed between any two SCSI bus signals measured between any two SCSI devices excluding any signal distortion skew delays.

### 1.1.7 Data release delay

The maximum time for an initiator to release the DATA BUS signals following the transition of the I/O signal from false to true.

### 1.1.8 Disconnection delay

The minimum time that a target shall wait after releasing BSY before participating in an ARBITRATION phase when honoring a DISCONNECT message from the initiator.

# 1.1.9 Power on to selection

The recommended maximum time from power application until an SCSI target is able to respond with appropriate status and sense data to the TEST UNIT READY, INQUIRY, and REQUEST SENSE commands (See SCSI-3 Primary Commands Standard).

### 1.1.10 Receive assertion period

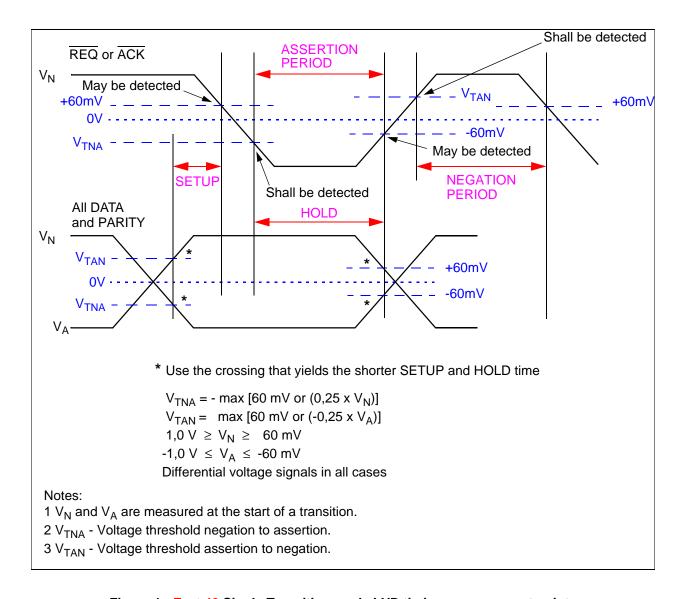

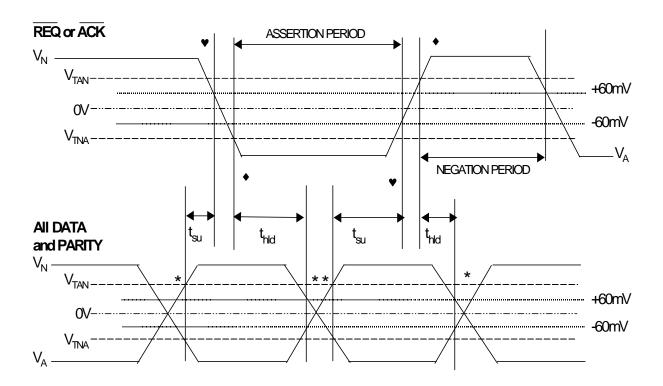

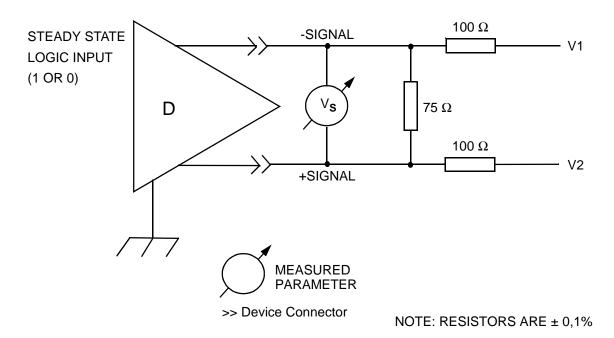

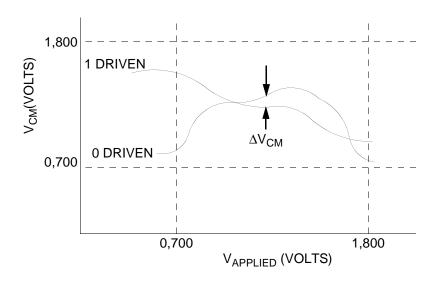

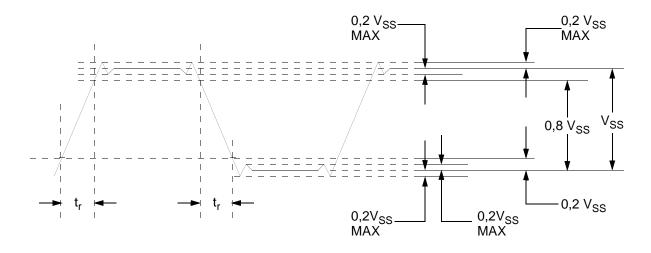

The minimum time required at a SCSI device receiving a REQ or REQQ signal for the signal to be asserted while using synchronous data transfers. Also, the minimum time required at a SCSI device receiving an ACK or ACKQ signal for the signal to be asserted while using synchronous data transfers. For SE fast-5 and fast-10 operation, the time period is measured at the 0,8 V level. For SE fast-20 operation the period is measured at the 1,0 V level. For LVD see Figures 1 and 2 for signal measurement points. The timings for the REQQ and ACKQ signals only apply to 32-bit-wide data transfers.

### 1.1.11 Receive hold time

In single transition mode the minimum time required at the receiving SCSI device between the assertion of the REQ or REQQ signal or the ACK or ACKQ signals and the changing of the DATA BUS while using synchronous data transfers. In double transition mode the minimum time required at the receiving SCSI device between the transition (i.e. assertion or negation) of the REQ or REQQ signal or the ACK or ACKQ signals and the changing of the DATA BUS while using synchronous data transfers. The timings for the REQQ and ACKQ signals only apply to 32-bit-wide data transfers.

### 1.1.12 Receive negation period

The minimum time required at a SCSI device receiving a REQ or REQQ signal for the signal to be negated while using synchronous data transfers. Also, the minimum time required at a SCSI device receiving an ACK or ACKQ signal for the signal to be asserted while using synchronous data transfers. For SE fast-5 and fast-10 operation, the time period is measured at the 2,0 V level. For SE fast-20 operation the period is measured at the 1,9 V level. For LVD see Figures 1 and 2 for signal measurement points. The timings for the REQQ and ACKQ signals only apply to 32-bit-wide data transfers.

# 1.1.13 Receive REQ/REQQ (ACK/ACKQ) period

The receive REQ/REQQ (ACK/ACKQ) period is the average time between assertion edges of the REQ/REQQ (ACK/ACKQ) signal measured without offset interruptions.

## 1.1.14 Receive setup time

In single transition mode the minimum time required at the receiving SCSI device between the changing of DATA BUS and the assertion of the REQ or REQQ signal or the ACK or ACKQ signal while using synchronous data transfers. In double transition mode the minimum time required at the receiving SCSI device between the changing of DATA BUS and the transition of the REQ or REQQ signal or the ACK or ACKQ signal while using synchronous data transfers. The timings for the REQQ and ACKQ signals only apply to 32-bit-wide data transfers.

# 1.1.15 Receive period tolerance

The minimum tolerance that an SCSI device shall allow to be subtracted from the negotiated synchronous period.

### 1.1.16 Reset hold time

The minimum time that the RST signal is asserted. There is no maximum time.

#### 1.1.17 Reset to Selection

The recommended maximum time from after a reset condition until an SCSI target is able to respond with appropriate status and sense data to the TEST UNIT READY, INQUIRY, and REQUEST SENSE commands (See SCSI-3 Primary Commands Standard).

### 1.1.18 Selection abort time

The maximum time that an SCSI device shall take from its most recent detection of being selected or reselected until asserting a the BSY signal in response. This time-out is required to ensure that a target or initiator does not assert the BSY signal after a SELECTION or RESELECTION phase has been aborted.

### 1.1.19 Selection time-out delay

The minimum time that an initiator or target should wait for a the assertion of the BSY signal in response during the SELECTION or RESELECTION phase before starting the time-out procedure. Note that this is only a recommended time period. Editor's Note: "a" in the first line is crossed out. This SPI-2 needs to be expanded to make it clear what "in response" refers to.

### 1.1.20 Signal Timing Skew

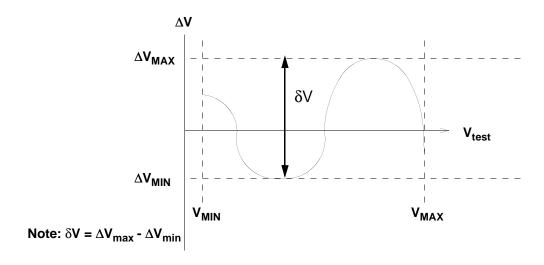

The maximum signal timing skew occurs when transferring random data <u>and in combination with interruptions of the REQ/REQQ (ACK/ACKQ) signal transitions (e.g. offset pauses).</u> The signal timing skew includes cable skew (measured with 0101... patterns) and signal distortion skew caused by random data patterns and transmission line reflections as shown in figure 1, figure 2, figure 1, and figure 2.

The receiver detection range is the part of the signal between the "may detect" level and the "shall detect" level on either edge. (see 1.2)

## 1.1.21 System deskew delay

The minimum time that a SCSI device should wait after receiving an SCSI signal to ensure that any signals transmitted at the same time are valid. The system deskew delay shall not be applied to the synchronous data transfers.

### 1.1.22 Transmit assertion period

The minimum time that a target shall assert the REQ or REQQ signal while using synchronous data transfers. Also, the minimum time that an initiator shall assert the ACK or ACKQ signal while using synchronous data transfers. The timing for the REQQ and ACKQ signals only apply to 32-bit-wide data transfers.

### 1.1.23 Transmit hold time

In single transition mode the minimum time provided by the transmitting SCSI device between the assertion of the REQ or REQQ signal or the ACK or ACKQ signal and the changing of the DATA BUS while using synchronous data transfers. In double transition mode the minimum time provided by the transmitting SCSI device between the transition of the REQ or REQQ signal or the ACK or ACKQ signal and the changing of the DATA BUS while using synchronous data transfers. The timings for the REQQ and ACKQ signals only apply to 32-bit wide data transfers.

### 1.1.24 Transmit negation period

The minimum time that a target shall negate the REQ or REQQ signal while using synchronous data transfers. Also, the minimum time that an initiator shall negate the ACK or ACKQ signal while using synchronous data transfers. The timing for the REQQ and ACKQ signals only apply to 32-bit -wide data transfers.

### 1.1.25 Transmit REQ/REQQ (ACK/ACKQ) period

The transmit period is the average time between assertion edges of the REQ/REQQ (ACK/ACKQ) signal measured without offset interruptions (e.g. offset pauses).

### 1.1.26 Transmit setup time

In single transition mode the minimum time provided by the transmitting SCSI device between the changing of DATA BUS and the assertion of the REQ or REQQ signal or the ACK or ACKQ signal while using synchronous data transfers. In double transition mode the minimum time provided by the transmitting SCSI device between the changing of DATA BUS and the transition of the REQ or REQQ signal or the ACK or ACKQ signal while using synchronous data transfers. The timings for the REQQ and ACKQ signals only apply to 32-bit -wide data transfers.

# 1.1.27 Transmit period tolerance

The maximum tolerance that an SCSI device may subtract from the negotiated synchronous period.

# 1.2 Measurement points

The measurements points for SE and differential ACK, REQ, DATA, and PARITY signals are defined in this clause.

#### 1.2.1 SE fast-10 data transfer rates

SE SCSI devices with data transfer rates up to and including fast-10 shall use the measurement points defined in figure 1 for the measurement of the timing values. The rise and fall times for the SE REQ/ACK signals shall be nominally the same as for the SE DATA/PARITY signals.

### 1.2.2 LVD =<40 MT/s Single Transition

LVD SCSI devices with a single transition agreement shall use the measurement points defined in figure 1 for the measurement of the timing values. The rise and fall times for the LVD REQ/ACK signals shall be nominally the same as for the LVD DATA/PARITY signals.

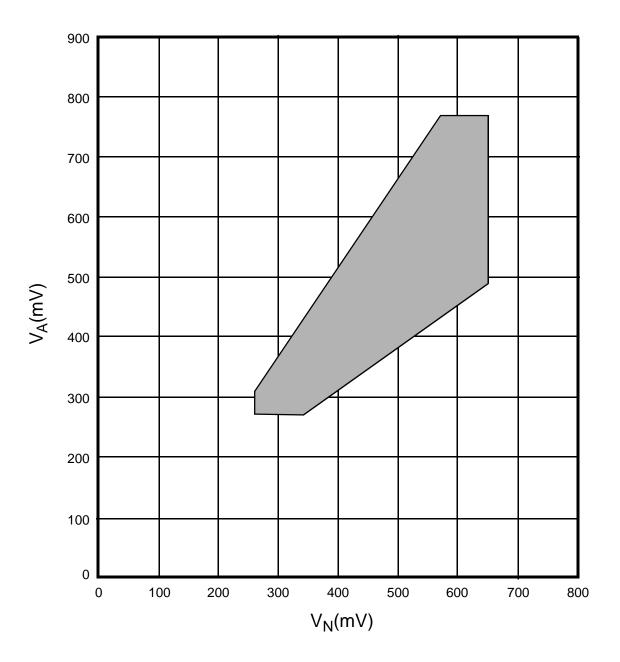

Figure 1 - Fast 40-Single Transition mode LVD timing measurement points

Figure 1 illustrates that receivers may require a larger LVD signal to overcome a strongly asserted or negated state than required for a weakly asserted or negated state. With the maximum assertion level of  $V_A$  it requires a signal that crosses the zero differential level by at least 0,25 x  $V_A$  (but at least by 60 mV in all cases) to guarantee detection of a negation for fast signals. The same relationship applies for the maximum negated level  $V_N$ . Conditions exist with longer loaded SCSI busses and irregular REQ and ACK pulse widths where long assertions or negations produce a much larger signal than short assertions or negations. This sets up an environment where the short REQ or ACK pulses may not have adequate timing margin unless the definitions in figure 1 are used in the measurement of timing parameters.

Measurement of driver timing parameters shall be performed using the circuit and test conditions defined in A.2.5 applied to the device connector. Receiver timing parameters are defined by the waveforms existing at the connector of the receiving SCSI device. The receiver timing parameters include the effects of data pattern. The receiver data pattern is therefore not defined.

### 1.2.3 LVD >40 MT/s Double Transition

LVD SCSI devices, which have a transfer double transition agreement in the Fast 80 range shall use the measurement points defined in figure 1 for the measurement of the timing values. The rise and fall times for the LVD REQ/ACK signals shall be nominally the same as for the LVD DATA/PARITY signals.

- \* Use the crossing that yields the shorter SETUP and HOLD time

- ♦ Shall be detected

$V_{TNA} = -max[60mV \text{ or } (0,25 \text{ xV}_N)]$

$V_{TAN} = max [60 \text{ mV or } (-0.25 \text{ x V}_{A})]$

$1,0 \text{ V} \ge \text{V}_{\text{N}} \ge 60 \text{ mV}$

$-1,0 \text{ V} \le \text{V}_{A} \le -60 \text{ mV}$

Differential voltage signals in all cases

### Notes:

- 1  $V_N$  and  $V_A$  are measured at the start of a transition.

- 2  $V_{TNS}$  Voltage threshold negation to assertion.

- 3 V<sub>TAN</sub> Voltage threshold assertion to negation.

4 t<sub>SU</sub> Setup time.

- 5 t<sub>hld</sub> Hold time.

Figure 2 - Fast 80 Double Transition mode LVD timing measurement points

### 1.2.4 Fast-40 data transfer rates

Figure 3 shows how the setup and hold times are calculated for various physical configurations on SCSI devices that support up to and including fast-40 data transfers. The minimum set up and hold timings specified in figure 3 shall be used. Note that these values are different for the driver and the receiver but that the receiver sensitivity provides the threshold points for both. This is required because both extreme cases of attenuation need to be covered:

- a) receivers connected to drivers with very short interconnect, and

- b) receivers connected to drivers through worst case interconnect.

Fast-40 <u>Single Transition</u> setup and hold times shall apply if a transfer rate <u>>20 and up to 40 MT/S</u> is negotiated <u>along with single transition mode</u>.

FAST 40 SETUP AND HOLD TIMINGS (ALL TIMES IN ns) **PROTOCOL PROTOCOL** CHIP CHIP TX **CABLE** RX**BOARD SKEW BOARD SKEW** CHIPS: **MINIMUM** SETUP INT T/ 9.5 0.25 9,25 4.5 4.75 0.25 4.5 HOLD 4,5 INT R 9,25 4,75 9,5 SEP T/ ! 10,75 1,5 9,25 4,5 4,75 2,0 2,75 SEP R · 10,75 9,25 4,75 2,75 1,5 9,25 4,5 SEP T/ ! 10,75 4,75 0,25 4,5 10,75 INT R 9,25 4,75 4,5 0,25 9,25 4,5 INT T/ 9,5 4,75 2,0 2,75 9,25 2,75 SEP R 9,5 4,75 INT T/R (SEP T/R) indicates integrated (separate) protocol and transceiver chip Board skew includes the separate transceiver and trace skew Signal timing skew includes cable skew and signal distortion skew Distortion skew includes ISI (intersymbol interference) and signal crossing time through the receiver detection range

Figure 3 - Fast-40 Single Transition System setup and hold timings (all times in ns)

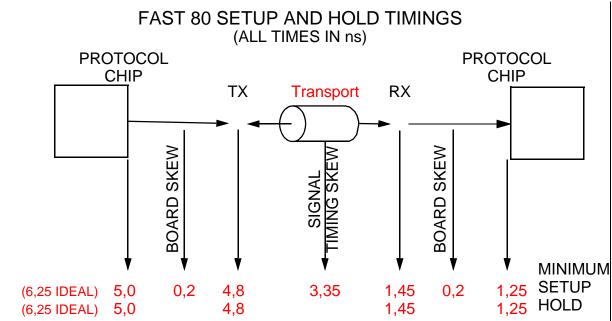

#### 1.2.5 Fast-80 data transfer rates

Figure 5 shows how the setup and hold times are calculated for various physical configurations on SCSI

devices that support up to and including fast-80 data transfers. The minimum set up and hold timings specified in figure 5 shall be used. Note that these values are different for the driver and the receiver but that the receiver sensitivity provides the threshold points for both. This is required because both extreme cases of attenuation need to be covered:

- a) receivers connected to drivers with very short interconnect, and

- b) receivers connected to drivers through worst case interconnect.

Fast-80 <u>Double Transition</u> setup and hold times shall apply if a transfer rate >40 and up to 80 MT/S is

negotiated.

Figure 4 - Fast-80 <u>Double Transition</u> System setup and hold timings (all times in ns)

INT T/R indicates integrated protocol and transceiver chip

Board skew includes the separate transceiver and trace skew

Signal timing skew includes cable skew and signal distortion skew

Distortion skew includes ISI (intersymbol interference) and <u>differences</u> in signal crossing time through the receiver detection range

# 2 SCSI parallel interface electrical characteristics

SPI-3 devices may use the following transmitter implementations:

- a) SE active negation;

- b) LVD.

LVD/MSE transmitters support SE active negation. LVD/MSE device may be damaged if exposed to SE passive negation voltages.

If a transceiver fully complies with the requirements of more than one of the above transmitter implementations then it may interoperate with those transceiver types.

For each transmitter implementation one or more different receiver and capacitance specifications may apply.

For measurements in this clause, SCSI bus termination is assumed to be external to the SCSI device. See 6.4 for the terminating requirements for the RESERVED lines. SCSI devices may have provision for allowing optional internal termination provided the internal termination conforms with 7.1.1, 2.1.1, 2.2.1 or 7.4.1 when enabled and the SCSI device, including the disabled termination, conforms with 7.1.4, 2.1.4, or 7.4.3 when the internal termination is disabled.

In addition to the device electrical requirements defined in the remaining subclauses of this clause, devices shall meet the requirements specified in table 4 and table 5 at the device connector.

Table 4 - Electrical input requirements at the device connector

| Value                                                    | Minimum     | Maximum    | Notes                                                                                                                                                                                              |

|----------------------------------------------------------|-------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SE (active negation) and MSE input voltage               | -0,5 V D.C. | 4,1 V D.C. | Absolute maximum at all operating conditions, including the DIFFSENS connection for SE (active negation), and LVD/MSE SCSI devices, for SCSI devices meeting the fast-20 requirements in table 24. |

| LVD input voltage (D.C. V + or - signal to local ground) | -0,5 V D.C. | 4,1 V D.C. | Absolute maximum at all operating conditions all signals except DIFFSENS.                                                                                                                          |

Table 5 - Input current requirements at the device connector for lines not being driven by the device

| Value                 | Maximum       | Notes                                                                                   |

|-----------------------|---------------|-----------------------------------------------------------------------------------------|

| MSE current magnitude | 20 μA<br>D.C. | Measured from + or - signal $V_{\text{IN}}$ 0 to 4,1 V to local ground each signal pin. |

| LVD current magnitude | 20 μA<br>D.C. | Measured from + or - signal $V_{\rm IN}$ < 2,5 V to local ground each signal pin.       |

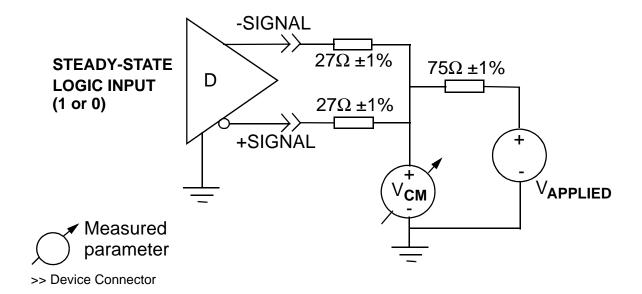

### 2.1 LVD alternative

#### 2.1.1 LVD termination

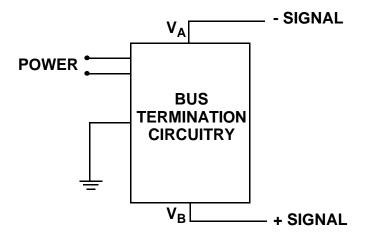

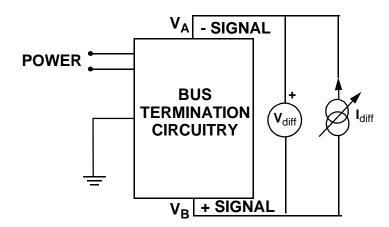

The electrical characteristics of LVD bus termination shall be as specified in this subclause. Figure 5 shows the  $V_B$  and  $V_A$  measurement points, referenced to local ground, for the differential LVD bus terminator.

Figure 5 - Differential LVD bus terminator

Figure 5 through figure 10 define the measurement points for the LVD terminators. Electrical characteristics shall meet the requirements in table 6 and table 7.

**CURRENT IS DRIVEN, VOLTAGE IS MEASURED**

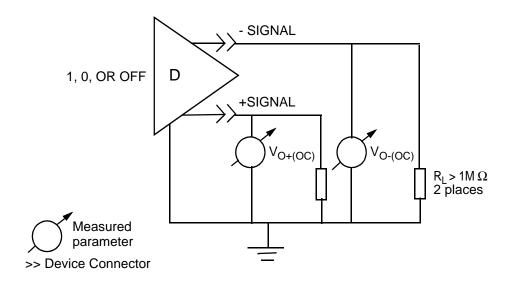

Figure 6 - Test circuit for terminator differential impedance

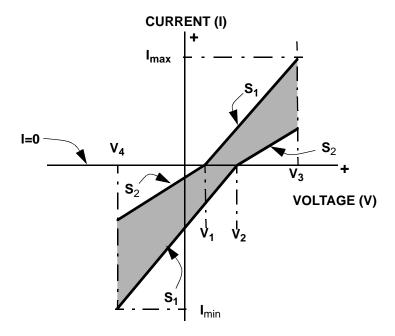

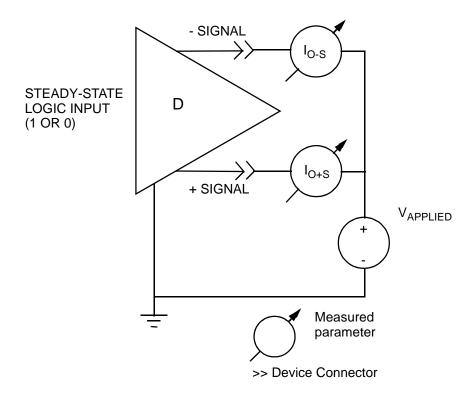

The requirements on the LVD bus termination that relate to differential impedance are specified in figure 6 and table 6. Figure 7 and table 6 show the allowed ranges for  $I_{diff}$  and  $V_{diff}$  in figure 6. The requirements that relate to differential impedance are specified in figure 7 and table 6. Table 6 specifies the allowed ranges for  $I_{diff}$  and  $V_{diff}$  in figure 6. The terminator bias voltage  $V_{BIAS}$  ( $V_{BIAS}$  is the voltage measured when I=0 in figure 27) shall have the values measured between  $V_1$  and  $V_2$  as measured at  $V_{diff}$  in figure 6 with the range values defined in table 6 in the LVD impedance and  $V_{BIAS}$  tests column.

Figure 7 - Termination I-V characteristics for differential and common mode impedance tests

**VOLTAGE IS DRIVEN, CURRENT IS MEASURED**

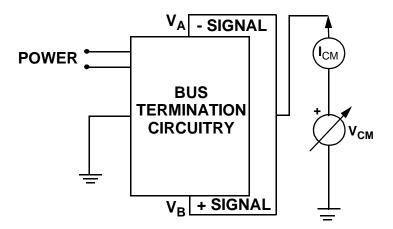

Figure 8 - Test circuit for termination common mode impedance test

The requirements that relate to common mode impedance are specified in figure 7 and table 6. Table 6 specifies the allowed ranges for  $I_{CM}$  and  $V_{CM}$  in figure 8. The terminator bias voltage  $V_{BIAS}$  ( $V_{BIAS}$  is the voltage measured when I=0 in figure 27) shall have the values measured between  $V_1$  and  $V_2$  as measured at  $V_{CM}$  in figure 8 with the range values defined in table 6 in the common mode impedance and  $V_{BIAS}$  tests column.

| Table 6 - I-V requirements for LVD impedance, common mode impedance, and V <sub>BIAS</sub> tests |

|--------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------|

| Values<br>(figure 7)                                 | LVD impedance and V <sub>BIAS</sub> tests (note) (figure 6) | Common mode impedance<br>and V <sub>BIAS</sub> tests<br>(figure 8) |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|

| V <sub>1</sub> (mV)                                  | 100                                                         | 1125                                                               |  |  |  |

| V <sub>2</sub> (mV)                                  | 125                                                         | 1375                                                               |  |  |  |

| V <sub>3</sub> (V)                                   | 1,0                                                         | 2,0                                                                |  |  |  |

| V <sub>4</sub> (V)                                   | -1,0                                                        | 0,5                                                                |  |  |  |

| I <sub>max</sub> (mA)                                | 9,00                                                        | N/A                                                                |  |  |  |

| I <sub>min</sub> (mA)                                | -11.25                                                      | N/A                                                                |  |  |  |

| S <sub>1</sub> (ohms)                                | 100                                                         | 100                                                                |  |  |  |

| S <sub>2</sub> (ohms)                                | 110                                                         | 300                                                                |  |  |  |

| Measurement                                          | D.C.                                                        | D.C.                                                               |  |  |  |

| Note: $V_A + V_B = 2.5 \pm 0.2 \text{ V (figure 6)}$ |                                                             |                                                                    |  |  |  |

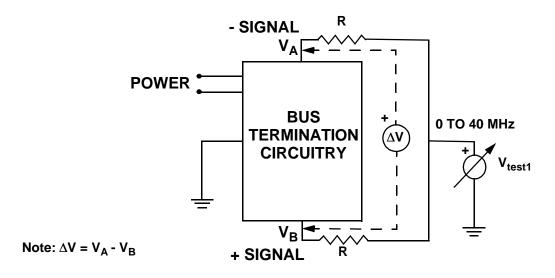

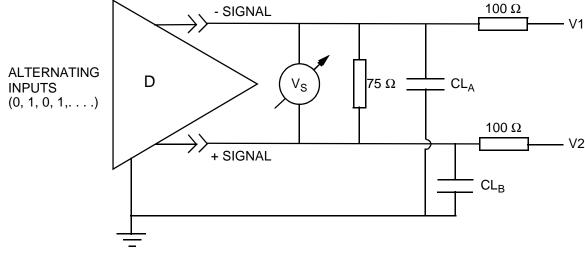

The requirements on termination that relate to electrical balance are specified in figure 9, figure 10, and table 7. The voltage  $V_{test1}$  in figure 9 is varied over frequencies of 0 to 40 MHz with amplitude varied over the range  $V_{MIN}$  to  $V_{MAX}$  specified in table 7 while the voltage named  $\Delta V$  in figure 9 is measured. The maximum difference between values of  $\Delta V$  ( $\Delta V$  in figure 9) measured during this test shall be as specified in table 7.

Figure 9 - Termination balance test configuration

Figure 10 - Termination balance test data definition

Table 7 - Values for LVD termination balance test

| Value                                                                                                                                  | LVD         |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|

| V <sub>MIN</sub> (V <sub>test1</sub> peak)                                                                                             | 0,7         |  |  |  |

| V <sub>MAX</sub> (V <sub>test1</sub> peak)                                                                                             | 1,8         |  |  |  |

| R (ohms)                                                                                                                               | 100 ± 0,01% |  |  |  |

| δV                                                                                                                                     | 20 mV max   |  |  |  |

| Note: $\Delta V$ - Input impedance for instrumentation > 10 Kohms $V_{test1}$ swept through all values between $V_{MIN}$ and $V_{MAX}$ |             |  |  |  |

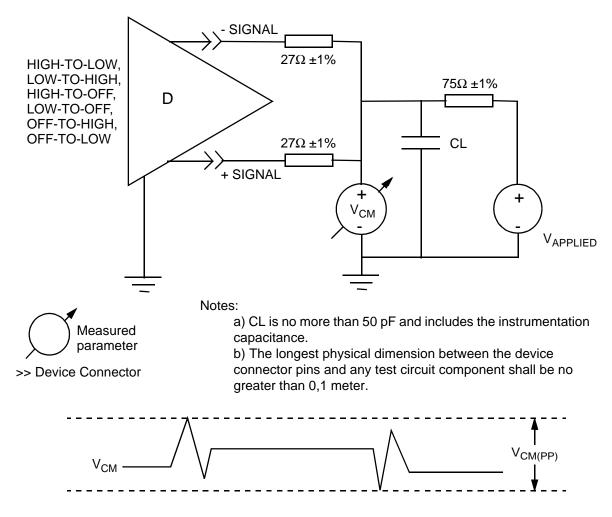

### 2.1.2 LVD driver characteristics

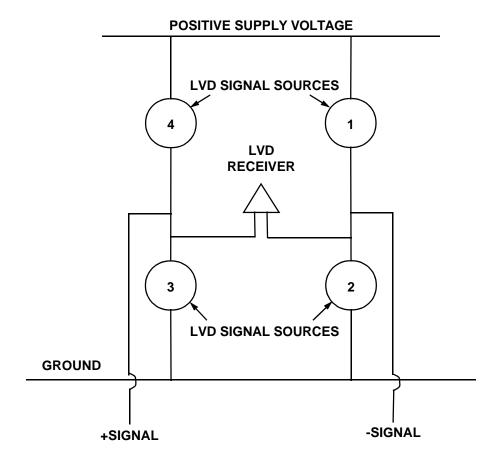

The LVD driver shall provide balanced asymmetrical sources that provide current from positive supply voltage to one signal line while sinking the same current to ground from the other signal line as shown in figure 11. Diagonally opposite sources operate together to produce a signal assertion or a signal negation. An assertion is produced when positive supply voltage current is sourced from source 4 to the +signal line and source 2 sinks the same current from the -signal line to ground. A negation is produced when positive supply voltage current is sourced from source 1 to the -signal line and source 3 sinks the same current from the +signal line to ground.

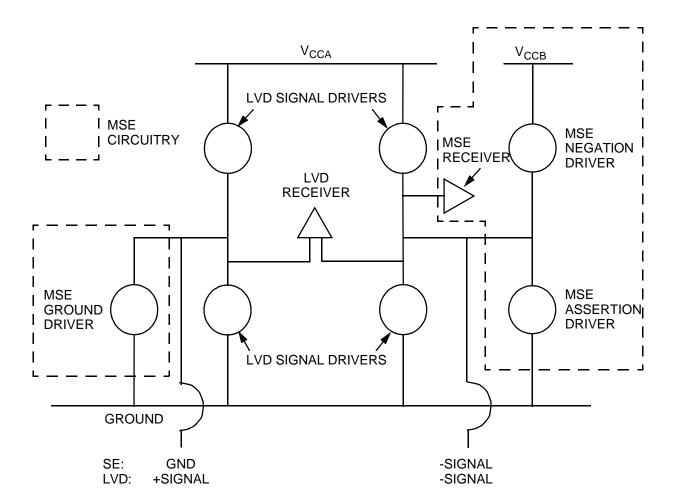

Figure 11 - LVD transceiver architecture

Balanced transmissions occur when the changes in +SIGNAL current and the changes in the -SIGNAL current precisely cancel each other. The balance is important to reduce EMI and common mode signals. Asymmetry occurs when the intensity of the source 2 and 4 assertion pair is different from the source 1 and 3 negation pair. To compensate for the negation biasing effect of the terminators, the 2 and 4 assertion pair is stronger than the 1 and 3 negation pair.

LVD drivers shall meet the specifications in annex A.

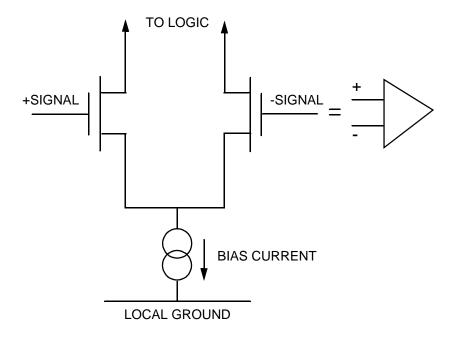

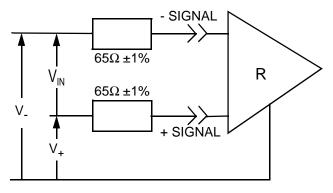

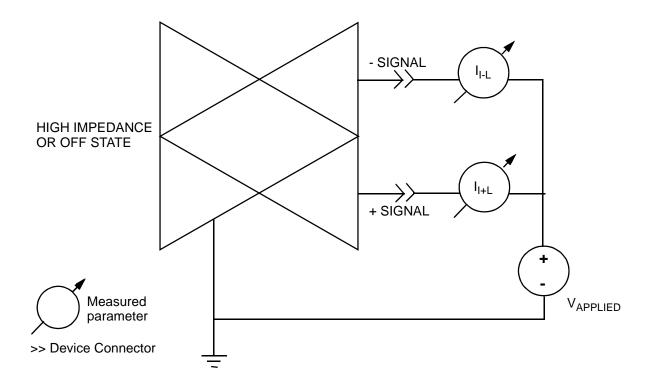

### 2.1.3 LVD receiver characteristics

LVD receivers shall be connected to the +signal and -signal as shown in figure 11. An example of an LVD receiver is shown in figure 12. LVD receivers shall meet the requirements in annex A.

Figure 12 - LVD receiver example

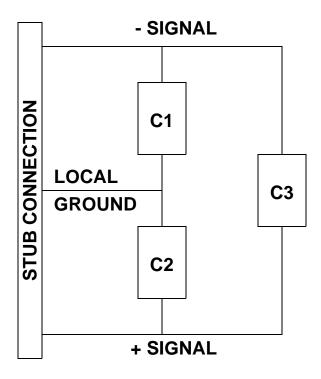

### 2.1.4 LVD capacitive loads

Capacitive loads on differential SCSI busses shall meet the requirements specified in this section.

There are three components to differential SCSI bus capacitive loading: -Signal to local ground (C1), +Signal to local ground (C2), and -signal to +signal (C3) as shown in figure 13. The values C1, C2, and C3 represent measurements between the indicated points and do not represent discrete capacitors. Capacitance measurements shall be made with a nominal 1MHz source with the same nominal D.C. level on the +signal and the -signal as specified in table 8. The driving source from the instrumentation shall apply an A.C. signal level less than 100 mV rms.

.

Figure 13 - Capacitive loads

Table 8 - Values for LVD capacitive loads

| Capacitance measurement                                                                        | Maximum (1) | Notes                                                                                                       |  |  |

|------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------|--|--|

| C1 (pF)                                                                                        | <u>15</u>   | @V=0,7 to 1,8 V D.Csig/gnd<br>REQ, ACK, DATA and PARITY                                                     |  |  |

| C2 (pF)                                                                                        | <u>15</u>   | @V=0,7 to 1,8 V D.C. +sig/gnd REQ, ACK, DATA and PARITY                                                     |  |  |

| C3 (pF)                                                                                        | <u>8</u>    | @V=0,7 to 1,8 V D.C. both - and +sig/gnd<br>V is the same for both sigs ±100mV<br>REQ, ACK, DATA and PARITY |  |  |

| C1 (pF)                                                                                        | <u>25</u>   | @V=0,7 to 1,8 V D.Csig/gnd all other signals                                                                |  |  |

| C2 (pF)                                                                                        | <u>25</u>   | @V=0,7 to 1,8 V D.C. +sig/gnd all other signals                                                             |  |  |

| C3 (pF)                                                                                        | <u>13</u>   | @V=0,7 to 1,8 V D.C. both - and +sig/gnd V is the same for both sigs ±100mV all other signals               |  |  |

| C1 - C2   (pF)                                                                                 | 1,5         | REQ, ACK, DATA and PARITY (same signal)                                                                     |  |  |

| C1 - C2   (pF)                                                                                 | 3           | all other signals (same signal)                                                                             |  |  |

| C1(i) - C1(REQ)   (pF)                                                                         | 2           | For DATA(i) i = 0-15 and PARITY (i) i = 0,1                                                                 |  |  |

| C2(i) - C2(REQ)   (pF)                                                                         | 2           | For DATA(i) i = 0-15 and PARITY (i) i = 0,1                                                                 |  |  |

| C1(i) - C1(ACK)   (pF)                                                                         | 2           | For DATA(i) i = 0-15 and PARITY (i) i = 0,1                                                                 |  |  |

| C2(i) - C2(ACK)   (pF)                                                                         | 2           | For DATA(i) i = 0-15 and PARITY (i) i = 0,1                                                                 |  |  |

| note: It is recommended that implementors design capacitive loads to be as small as practical. |             |                                                                                                             |  |  |

It is recommended that implementors design capacitive loads to be as small as practical.

Devices containing the enabled bus termination shall have maximum values 1,5 times the maximums listed in table 8. Differential bus termination circuitry that is not part of a device shall have maximum values 0,5 times the maximums listed in table 8.

### 2.1.4.1 Management of LVD release glitches

Under some conditions, an LVD signal that transitions from actively negated to released may cause brief pulses to the true signal state. These pulses are called "release glitches" and may last up to a bus settle delay. Requirements are defined in this subclause to avoid adverse affects from release glitches.

SCSI devices shall incorporate the requirements specified in table 9 when using LVD drivers and optionally may incorporate the requirements when using other drivers. The usage of active negation increases cross

talk noise margin and increases the true-to-false transition speed as compared to passive negation.

Table 9 - Glitch management requirements for devices using LVD drivers

| Signals                                                                                      | Mode                                                         | Active negation | Transmitting device                                                                                                                            | Receiving device                                                                                                                                         |  |  |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BSY, SEL, RST                                                                                | I,T                                                          | Р               |                                                                                                                                                |                                                                                                                                                          |  |  |

| ACK, ATN                                                                                     | _                                                            | R               | The initiator shall wait for a BUS FREE phase (note) before releasing the ACK and ATN signals from the actively negated state.                 | Starting no later than a Bus Settle Delay after releasing the BSY signal, the target shall ignore the ACK and ATN signals until a subsequent connection. |  |  |

| REQ                                                                                          | Т                                                            | R               | The target shall wait 2,5 x (Bus Settle Delay) after releasing the BSY signal before releasing the REQ signal from the actively negated state. | The initiator shall begin to ignore the REQ signal within 1,5 x (Bus Settle Delay) of the transition of the BSY signal from true to false                |  |  |

| C/D, I/O, MSG                                                                                | Т                                                            | R               | After a selection or reselection phase, these signals shall not be released until the BSY signal is released.                                  | No glitch management required.                                                                                                                           |  |  |

| DATA BUS<br>(SELECTION<br>and<br>RSELECTION<br>phases)                                       | I,T                                                          | Р               | The transmitting device shall release all false data bits during these phases.                                                                 | No glitch management required.                                                                                                                           |  |  |

| DATA BUS<br>(During<br>information<br>transfers)                                             | I,T                                                          | R               | No glitch management required.                                                                                                                 | No glitch management required.                                                                                                                           |  |  |

| Key: I = initia                                                                              | Key: I = initiator; P = prohibited; R = required; T = target |                 |                                                                                                                                                |                                                                                                                                                          |  |  |

| Note: BUS FREE phase starts a Bus Settle Delay after the BSY and SEL signals are both false. |                                                              |                 |                                                                                                                                                |                                                                                                                                                          |  |  |

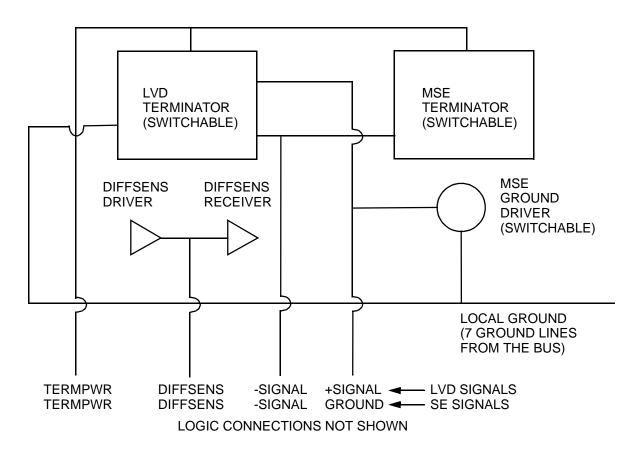

### 2.1.5 SE/HVD transmission mode detection

Transmission mode detection by LVD SCSI devices of SE and HVD SCSI devices is accomplished through the use of the DIFFSENS line. Requirements for devices and terminators for DIFFSENS are not the same as for "signal" lines because DIFFSENS is driven and detected using its own SE transmission and detection scheme.

LVD termination shall drive the DIFFSENS line as specified in 2.1.5.1 and LVD SCSI devices shall sense the DIFFSENS signal as specified in 2.1.5.2.

Devices and terminators connected to the DIFFSENS line shall comply with the requirements in table 4 and table 5.

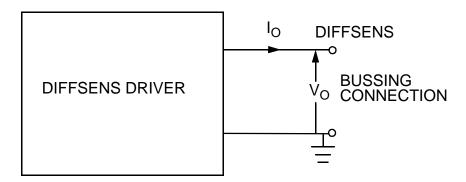

### 2.1.5.1 LVD DIFFSENS driver

The LVD DIFFSENS driver sets a voltage level on the DIFFSENS line that uniquely defines a LVD transmission mode. LVD terminators and multimode terminators (see 2.2.1) shall provide a LVD DIFFSENS driver according to the specifications in table 10.

| Value                                                                      | max. | nominal | min. | notes                                                                                                                |

|----------------------------------------------------------------------------|------|---------|------|----------------------------------------------------------------------------------------------------------------------|

| V <sub>O</sub> (volts) when I <sub>O</sub> = 0 (shorted to ground) to 5 mA | 1,4  | 1,3     | 1,2  |                                                                                                                      |

| I <sub>OS</sub> (mA)                                                       | 15   | 5       |      | With TERMPWR at operational levels and $V_0 = 0$ .                                                                   |

| Input current D.C.  (μΑ)                                                   | 10   |         |      | With terminator disabled.                                                                                            |

| Input sink current D.C. ( $\mu$ A) at V <sub>O</sub> = 2,75V               | 200  |         | 20   | Required to prevent the line from floating and to ensure the HVD DIFFSENS drivers dominate the LVD DIFFSENS drivers. |

Table 10 - LVD DIFFSENS driver specifications

### Note:

- All requirements apply at the terminator bussing connection (see figure 4).

- All measurements per figure 14.

Figure 14 - LVD DIFFSENS driver signal definitions

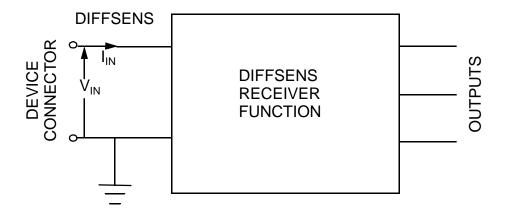

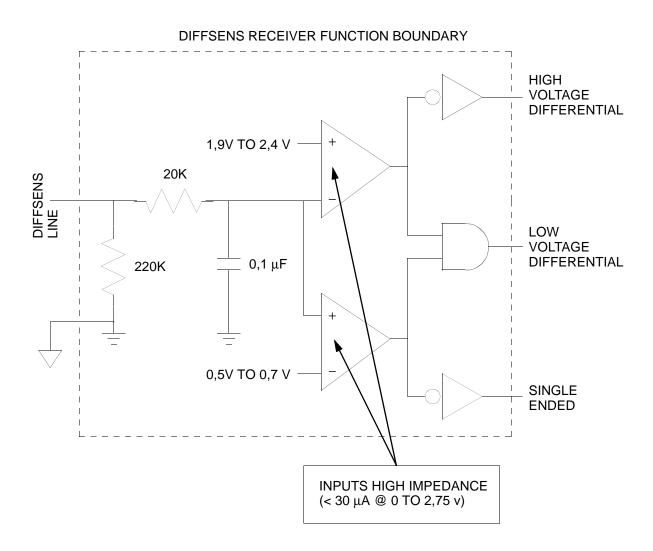

### 2.1.5.2 LVD DIFFSENS receiver

LVD SCSI devices shall incorporate a LVD DIFFSENS receiver that detects the voltage level on the DIFFSENS line for purposes of informing the device of the transmission mode being used by the bus. The LVD DIFFSENS receiver shall be capable of detecting SE, LVD, and HVD SCSI devices. Table 11 and figure 15 define the receiver input levels for each of the three modes.

Figure 15 - DIFFSENS receiver function

Table 11 - DIFFSENS receiver operating requirements

| V <sub>in</sub> range                                                                                                                                                                                                                        | Sensed differential driver type           |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|

| -0,35V to +0,5V                                                                                                                                                                                                                              | SE                                        |  |  |  |

| > +0,5V to < 0,7V                                                                                                                                                                                                                            | indeterminate for detecting a driver type |  |  |  |

| 0,7V to 1,9V                                                                                                                                                                                                                                 | LVD                                       |  |  |  |