To:SPI-3 Physical Working GroupFrom:Vincent Bastiani (vince\_bastiani@corp.adaptec.com)Subject:Initial test results on dual-edge clock signalsDate:Tuesday, December 02, 1997

The presentaion on dual-edge clock signals follows.

## TEST SETUP

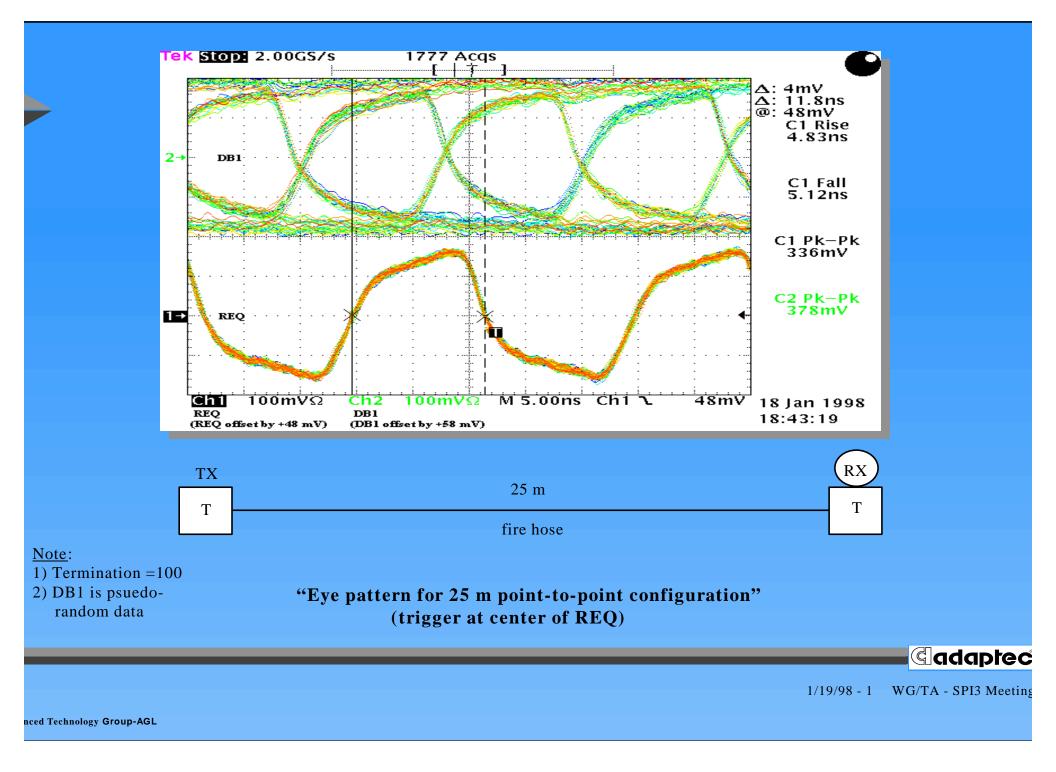

- •Data and Req signal driven as in dual edge

- •Data is pseudo random pattern of 127 bits with run length of 7

- •All lines driven with same pattern but different phase (except D0)

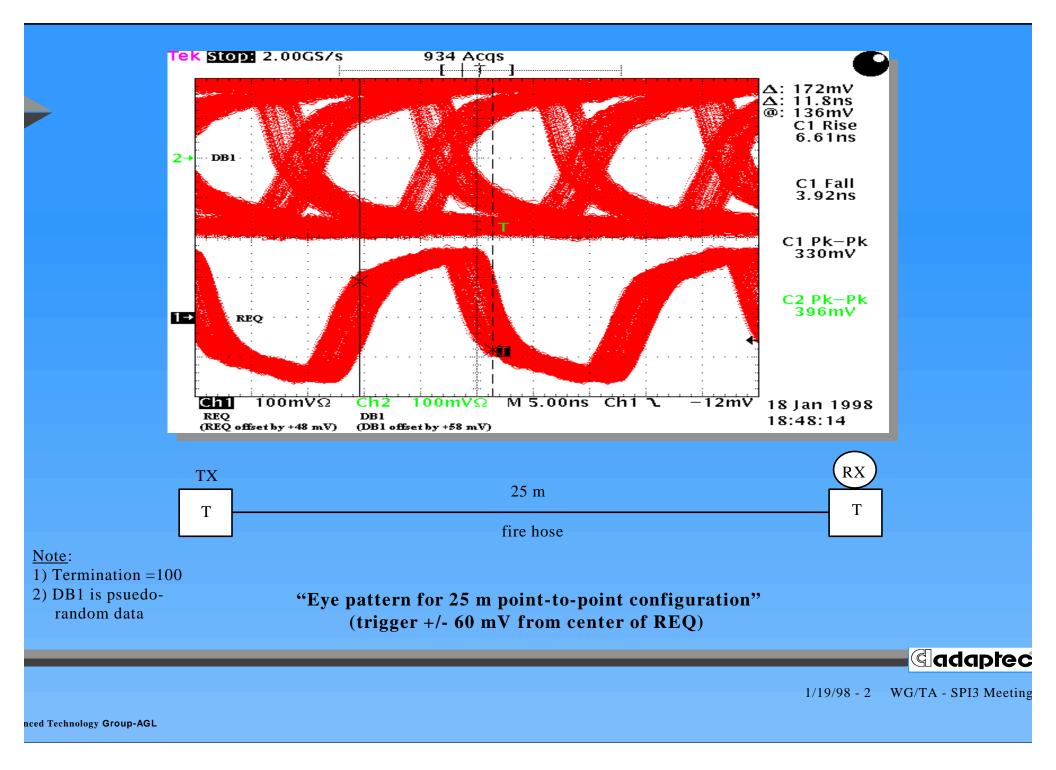

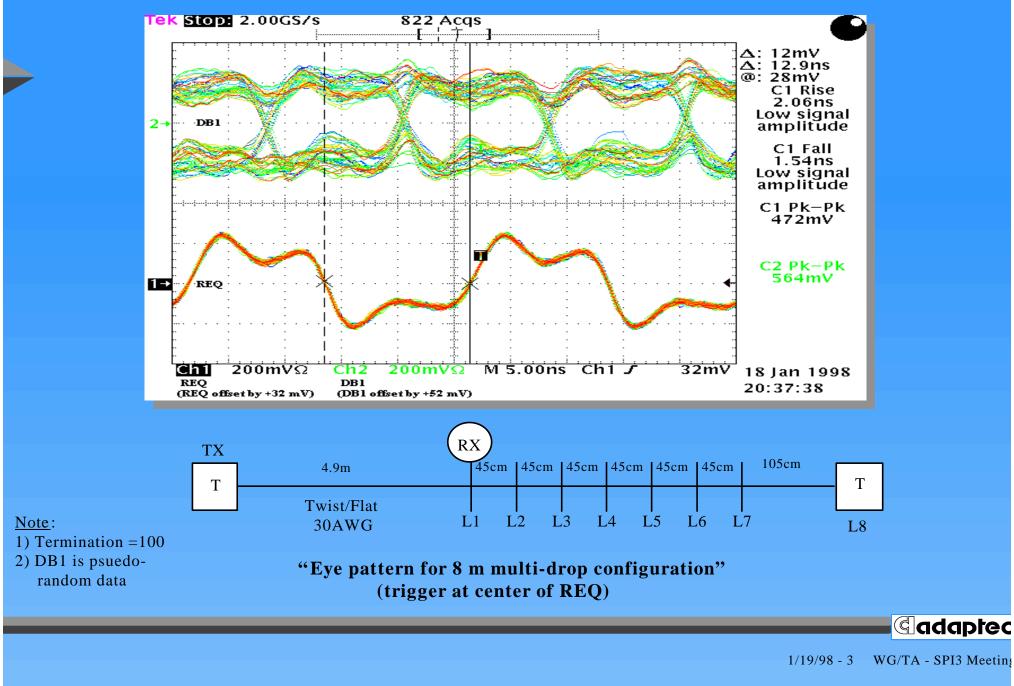

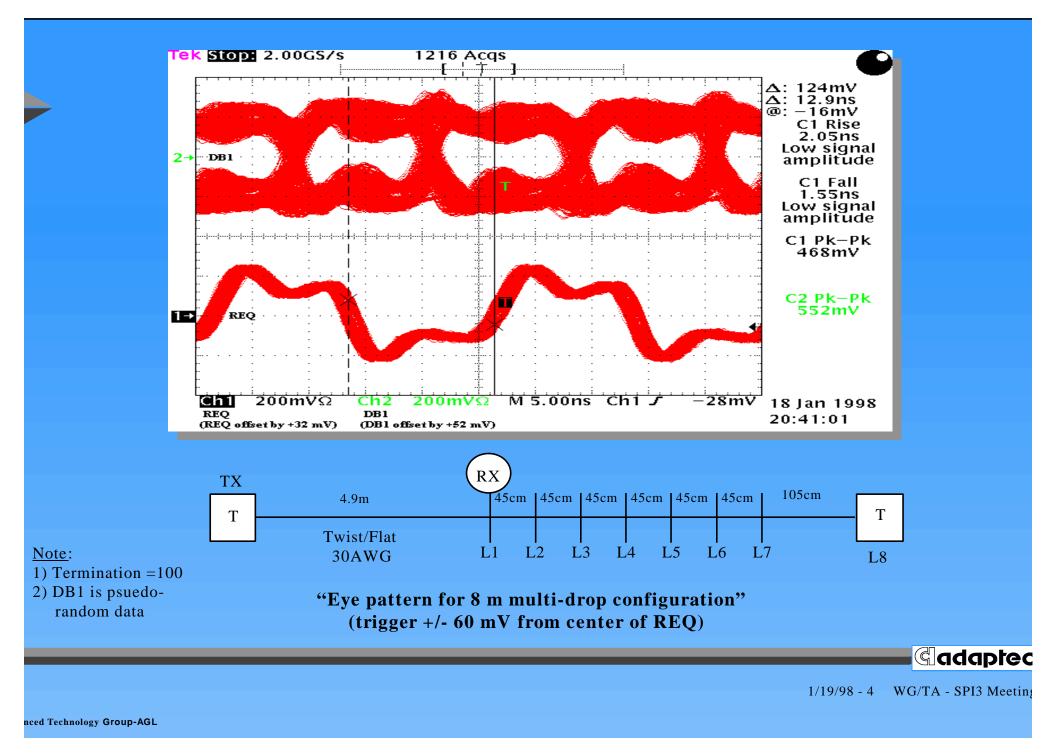

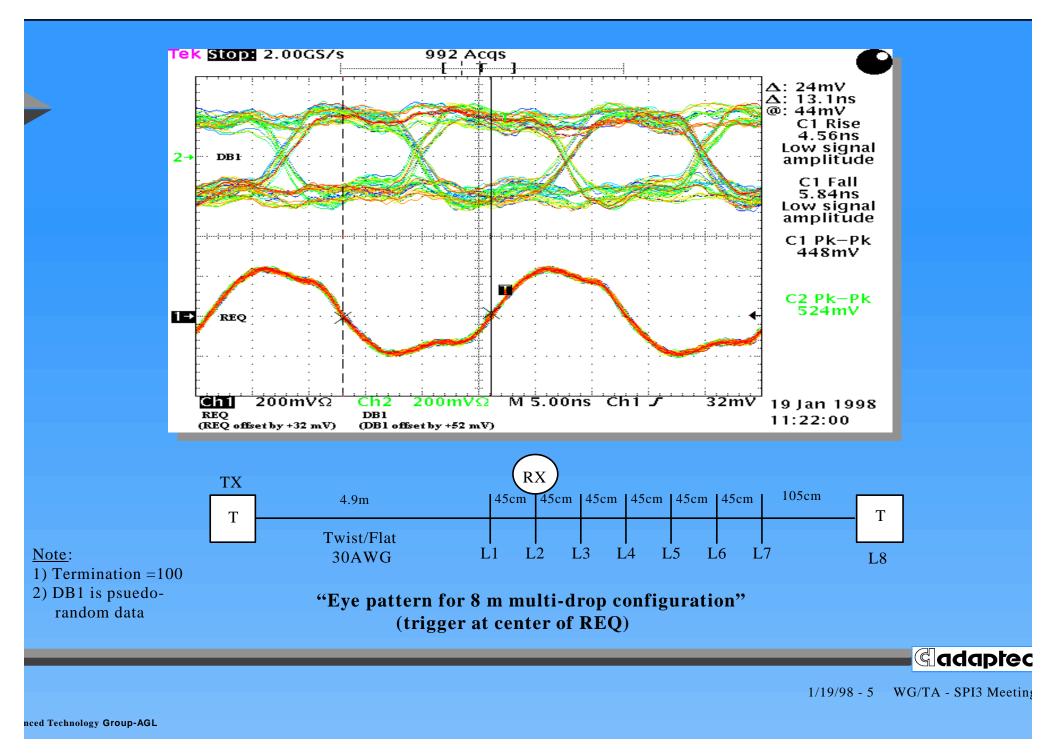

- •Various loaded cables used

- •Signal monitered at different positions

- •Data not checked if received correctly but observed eye pattern at each device.

dadaptec

•REQ and DATA Monitered

•Driver is 0.35 micron design used in Adaptec Target Ultra 2 chip

•Drive and Bias level nominal

Gadaptec

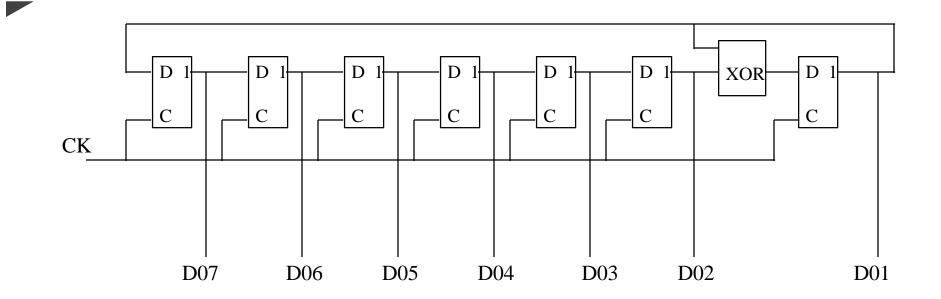

## D00 IS SQUARE WAVE AT BIT RATE

**Gadaptec**

anced Technology Group-AGL

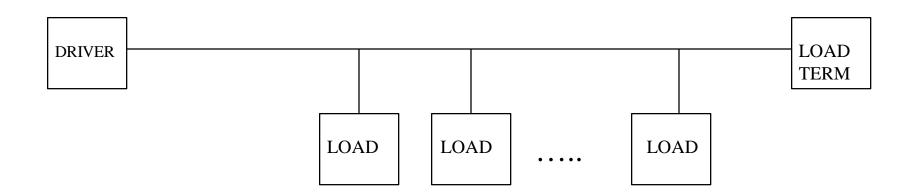

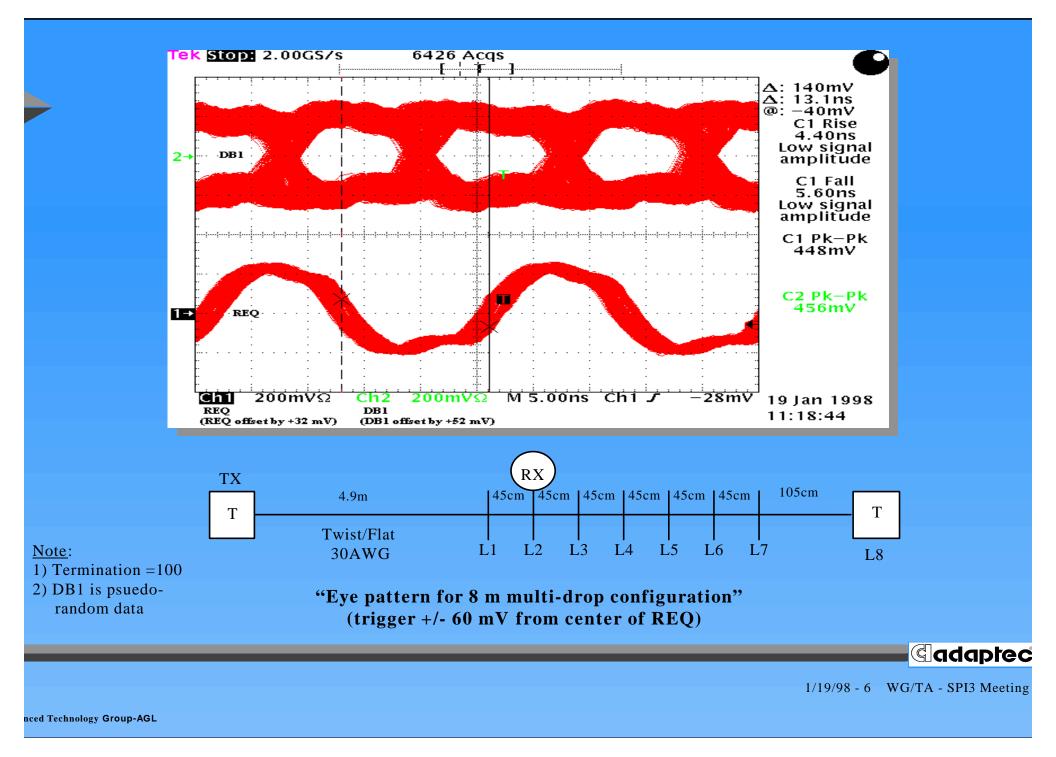

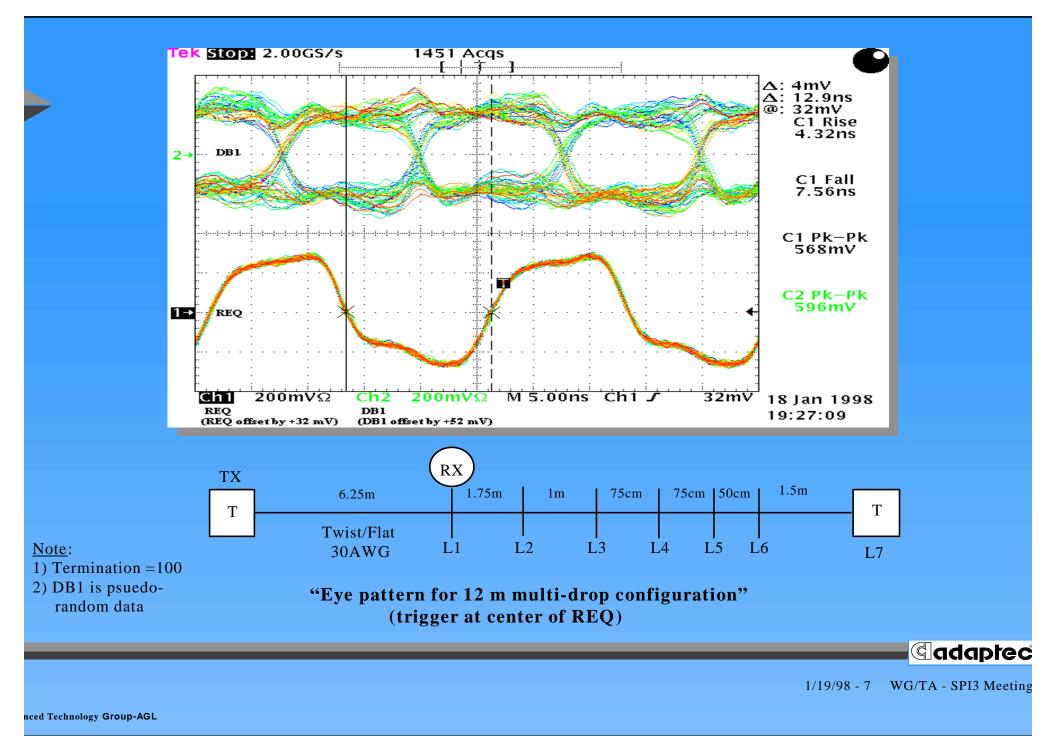

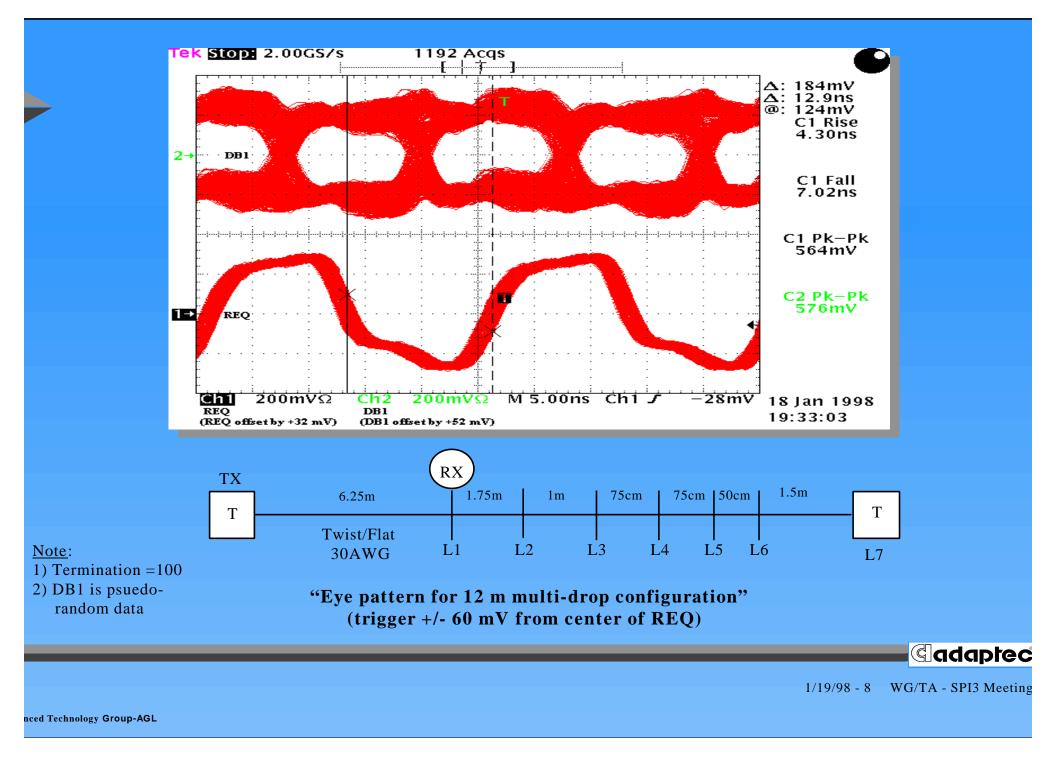

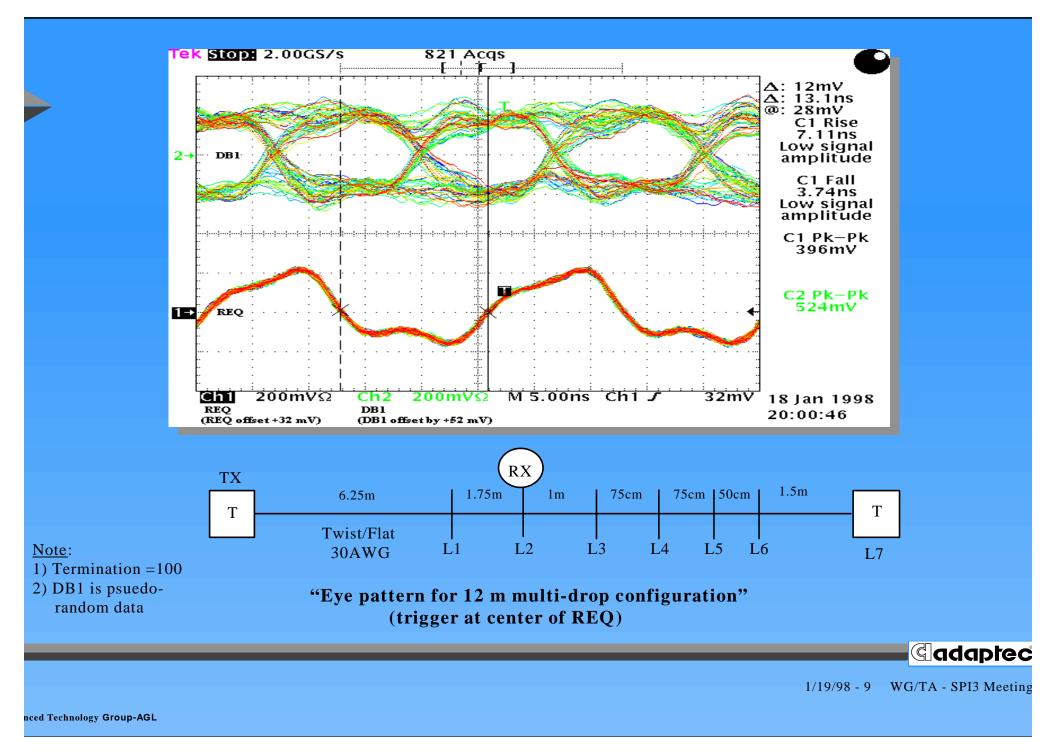

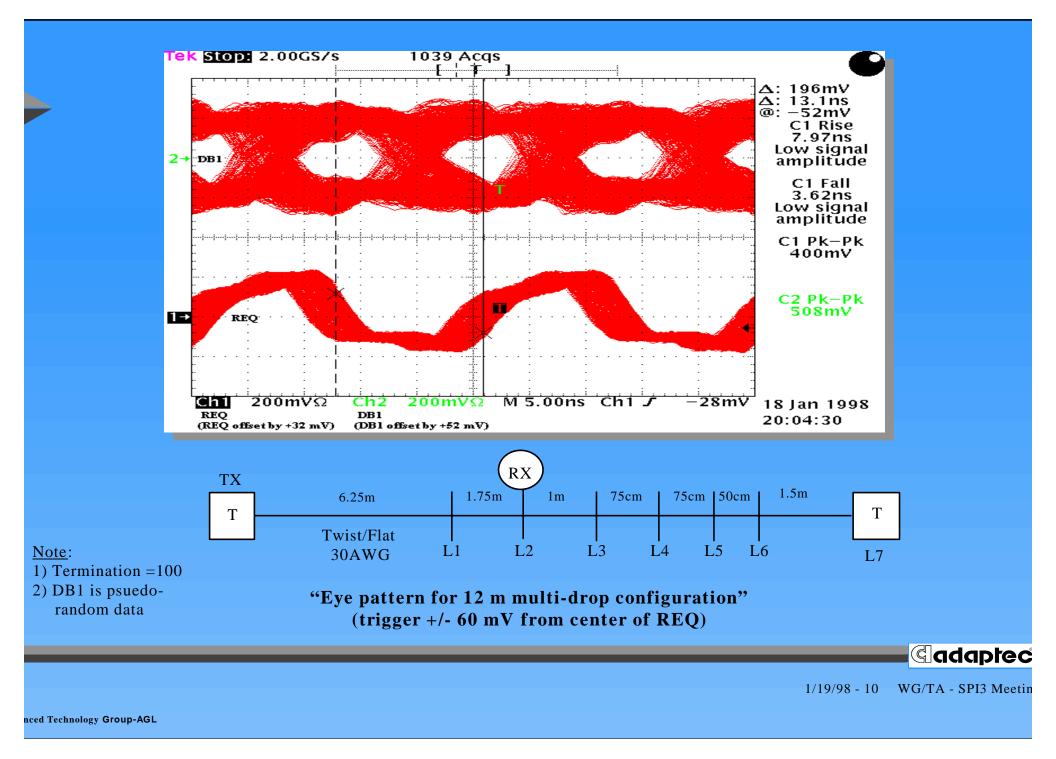

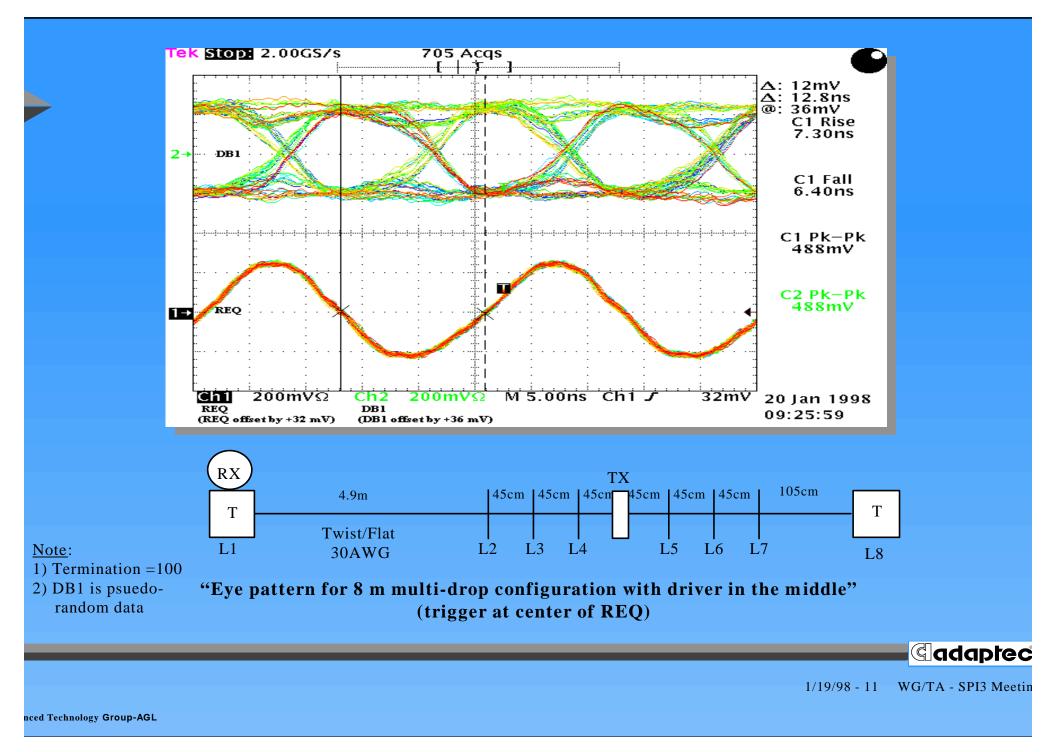

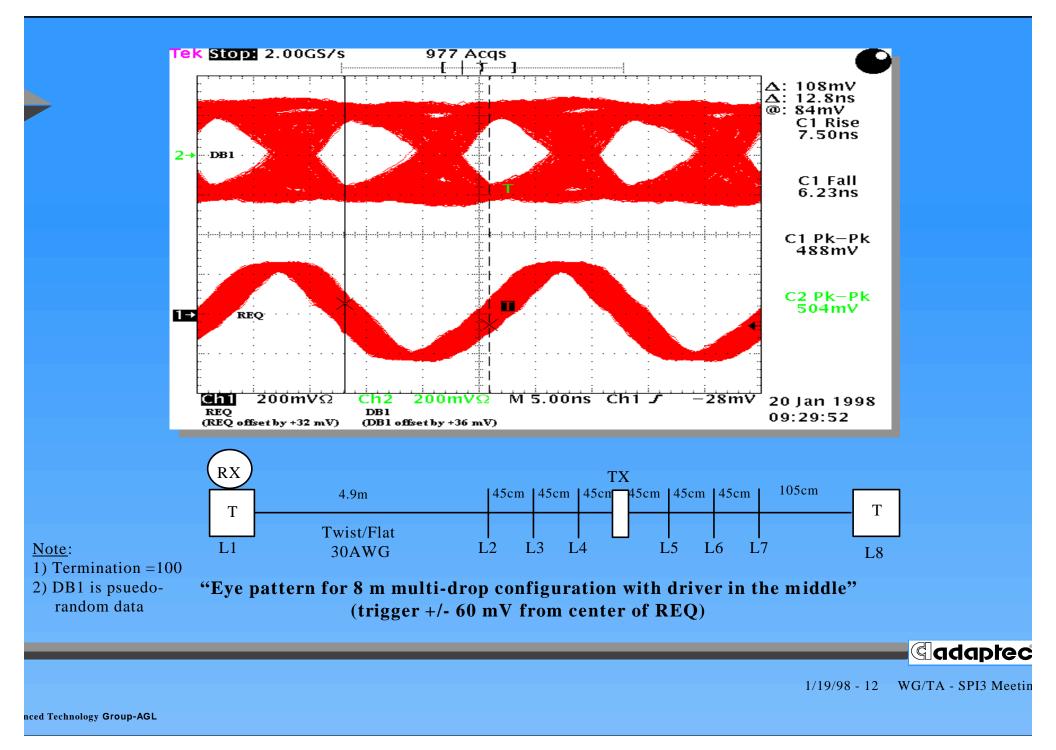

- •Worst case is tightly spaced loads

- •Drive level is important when reflections are present

- •More sensitive receiver would provide more margin

- •Must add in worst case cable skew

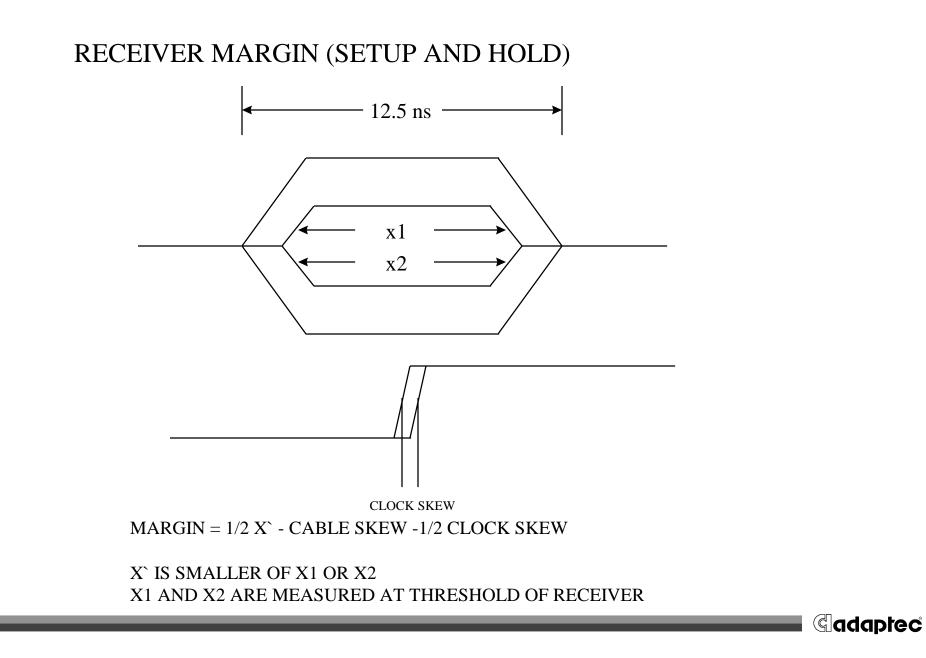

## SPECIFY MARGIN USING EYE PATTERNS

Use eye pattern to evaluate driver and receiver compliance

FC and 1394 specify this way but clock embedded in data

In parallel system like SCSI need to account for cable skew

dadaptec