# Reduced Block Commands (RBC)

# **Draft Proposal (T10/97-260r0)**

Reduced Block Commands Editor:

Michael Bryan Seagate Technology 2400 Trade Centre Longmont, CO 80503 Tel. (303) 684-1407 Fax (303) 684-1133

E-mail: mike\_bryan@notes.seagate.com

# **Working Draft**

# T10 Project 00XXXD

Revision 0 October 13, 1997

# Information technology — Reduced Block Commands

This is a draft proposed American National Standard under development by T10, a Technical Committee of the National Committee for Information Technology Standardization (NCITS). As such, this is not a completed standard and has not been approved. The Technical Committee may modify this document as a result of comments received during public review and its approval as a standard.

Permission is granted to members of NCITS, its technical committees and their associated task groups to reproduce this document for the purposes of NCITS standardization activities without further permission, provided this notice is included. All other rights are reserved. Any commercial or for-profit replication or republication is prohibited.

T10 Technical Editor:

Michael Bryan Seagate Technology 2400 Trade Centre Longmont, CO 80503 USA

(303)684-1407 (303)684-1133 FAX

mike\_bryan@notes.seagate.com

Reference numbers ISO/IEC xxxxx:199x ANSI NCITS.xxx-199x

Printed October 13, 1997

# **Points of contact**

| T10 Chair:             | John B. Lohmeyer<br>Symbios Logic, Inc.<br>4420 Arrows West Drive<br>Colorado Springs, CO 80907<br>USA |

|------------------------|--------------------------------------------------------------------------------------------------------|

|                        | (719) 533-7560<br>(719) 533-7036 FAX<br>john.lohmeyer@symbios.com                                      |

| T10 Vice-chair:        | Lawrence J. Lamers<br>Adaptec, Inc.<br>691 South Milpitas Boulevard<br>Milpitas, CA 95035              |

|                        | (408) 957-7817<br>(408) 957-7193 FAX<br>Ijlamers@aol.com                                               |

| NCITS Secretariat:     | NCITS Secretariat<br>1250 I Street NW, Suite 200<br>Washington, DC 2000<br>USA                         |

|                        | (202) 737-8888<br>(202) 638-4922 FAX                                                                   |

| T10 Bulletin board:    | (719) 533-7950                                                                                         |

| T10 FTP:               | ftp.symbios.com/pub/standards/io/x3t10                                                                 |

| T10 Home page:         | http://www.symbios.com/x3t10                                                                           |

| T10 Reflector:         | scsi@symbios.com<br>majordomo@symbios.com (to subscribe)                                               |

| IEEE 1394 Reflector:   | p1394@sun.com<br>bob.snively@sun.com (to subscribe)                                                    |

| Document distribution: | Global Engineering<br>15 Inverness Way East<br>Englewood, CO 80112-5704<br>USA                         |

|                        | (800) 854-7179<br>(303) 792-2181<br>(303) 792-2192 FAX                                                 |

|                        |                                                                                                        |

|           | ANSI <sup>®</sup> |

|-----------|-------------------|

| NCITS.xxx | x-199x            |

American National Standard for Information Systems –

# Reduced Block Commands (RBC)

Secretariat

**Information Technology Industry Council**

Not yet approved

American National Standards Institute, Inc.

## **Abstract**

This standard specifies the functional requirements for the SCSI Reduced Block Commands (RBC). RBC provides a subset of SBC, yet permits SCSI block logical units such as flexible disks, rigid disks, optical disks, etc., to attach to computers and provides the definition for their use.

An annex is provided that contains information required to implement the Serial Bus Protocol - 2 (SBP-2) command and control protocol on block devices.

# American National Standard

Approval of an American National Standard requires verification by ANSI that the requirements for due process, consensus and other criteria for approval have been met by the standards developer.

Consensus is established when, in the judgment of the ANSI Board of Standards Review, substantial agreement has been reached by directly and materially affected interests. Substantial agreement means much more than a simple majority, but not necessarily unanimity. Consensus requires that all views and objections be considered and that effort be made towards their resolution.

The use of American National Standards is completely voluntary; their existence does not in any respect preclude anyone, whether he has approved the standards or not, from manufacturing, marketing, purchasing, or using products, processes, or procedures not conforming to the standards.

The American National Standards Institute does not develop standards and will in no circumstances give interpretation on any American National Standard. Moreover, no person shall have the right or authority to issue an interpretation of an American National Standard in the name of the American National Standards Institute. Requests for interpretations should be addressed to the secretariat or sponsor whose name appears on the title page of this standard.

**CAUTION NOTICE:** This American National Standard may be revised or withdrawn at any time. The procedures of the American National Standards Institute require that action be taken periodically to reaffirm, revise, or withdraw this standard. Purchasers of American National Standards may receive current information on all standards by calling or writing the American National Standards Institute.

**CAUTION NOTICE**: The developers of this standard have requested that holder's of patents that may be required for the implementation of this standard, disclose such patents to the publisher. However, neither the developers nor the publisher has undertaken a patent search in order to identify which, if any, patents may apply to this standard.

Published by

American National Standards Institute 1430 Broadway, New York, NY 10018

Copyright © 1997 by American National Standards Institute All rights reserved.

Printed in the United States of America

# Contents

| oreword       |                                                     | iii      |

|---------------|-----------------------------------------------------|----------|

| Revision hist | ory                                                 | 5        |

| 1 Scope ar    | nd purpose                                          | 6        |

|               | De                                                  |          |

|               | iose                                                |          |

|               | /e references                                       |          |

|               | oved references                                     |          |

| 2.1 Appl      | erences under development                           | <i>1</i> |

| 3 Keyword     | s and Notation                                      | ، ه      |

|               | words                                               |          |

|               | sary                                                |          |

|               | reviations                                          |          |

|               | ventions                                            |          |

| 0.1.0011      |                                                     |          |

| 3.4.1         | Non-numeric values                                  | 10       |

| 3421          | Numeric values                                      | 10       |

|               | Block Commands                                      |          |

|               | D(10) Command                                       |          |

|               | RT STOP UNIT Command                                |          |

| 4.3 SYN       | CHRONIZE CACHE Command                              | 14       |

|               | TE(10) Command                                      |          |

|               | TE AND VERIFY Command                               |          |

|               | DE SELECT/SENSE page parameters                     |          |

|               |                                                     |          |

|               | Annex A                                             | 18       |

|               | Annex B                                             | 31       |

|               | Annex C                                             | 35       |

|               | Annex D                                             | 39       |

|               |                                                     |          |

|               | Annex E                                             | 40       |

|               |                                                     |          |

| Tables -      |                                                     |          |

| Γable 1 - Red | duce Block Command Set                              | 11       |

| Γable 2 - RE  | AD(10) command format                               | 12       |

|               | ART STOP UNIT command format                        |          |

|               | wer Condition Descriptions                          |          |

|               | NCHRONIZE CACHE command format                      |          |

| Γable 6 - WR  | RITE(10) command format                             | 15       |

|               | RITE AND VERIFY command format                      |          |

|               | C Device Parameters Page Format (3E <sub>16</sub> ) |          |

|               | C-2 commands for simple SBP-2 Disk Drives           |          |

|               | ODE SELECT(10) command format                       |          |

|               | ODE SENSE(10) command format                        |          |

|               | mple Hard Disk Page Control Values                  |          |

|               | EST UNIT READY command format                       |          |

| Γable 14 - Pr | referred TEST UNIT READY sense values               | 22       |

| Table 15 - SMART ASCQ values                                   | 23 |

|----------------------------------------------------------------|----|

| Table 16 - WRITE BUFFER command format                         |    |

| Table 17 - WRITE BUFFER Mode field                             | 25 |

| Table 18 - Unsolicited Status Sense Key/Code Values            | 26 |

| Table 19 - Power Management Information Values - Event Field   |    |

| Table 20 - Power Management Information Values - Status Field  |    |

| Table 21 - Media Event Information Value - Event Field         | 28 |

| Table 22 - Media Event Information Value - Status Field        | 29 |

| Table 23 - Device Busy Event Information Values - Event Field  | 29 |

| Table 24 - Device Busy Event Information Values - Status Field | 30 |

| Table 25 - Voltage Field Definition                            | 32 |

| Table 26 - Voltage Field Definition                            | 33 |

| Table 27 - Voltage Field Definition                            | 34 |

| Table 28 - Node Power Management registers                     | 35 |

| Table 29 - SRC field values                                    | 36 |

| Table 30 - Unit Power Management registers                     | 37 |

| Table 31 - SRC field values                                    | 38 |

|                                                                |    |

| Figures                                                        |    |

| Figure 1 - Event Status Information Format                     | 27 |

|                                                                |    |

| Figure 2 - Power Management Information Format                 |    |

| Figure 4 - Device Busy Information Format                      |    |

| Figure 5 - Command Set entry                                   |    |

| Figure 6 - Command_Set_Revision entry                          |    |

| Figure 7 - Logical_Unit_Number entry                           |    |

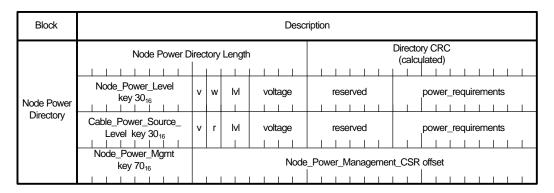

| Figure 8 - Node Power Directory Sample                         |    |

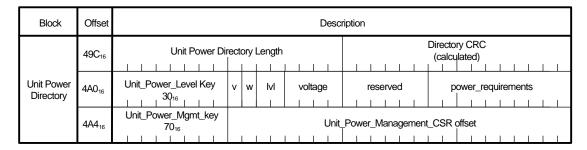

| Figure 9 - Unit Power Directory Sample                         | 3Z |

| Figure 10 - Node_Power_State register format                   |    |

| Figure 10 - Node_Fower_State register format                   |    |

| Figure 12 - Unit Power State register format                   |    |

| Figure 12 - Offit_Fower_State register format                  |    |

| i iyure 10 - iyiass sidraye iirlehace didok Diagram            | 40 |

Foreword (This foreword is not part of American National Standard NCITS.xxx -199x)

The Reduced Block Command set is designed to provide very efficient initiator-to-target operation of input/output logical units (disks, tapes, printers, etc.) by an operating system. RBC assumes that the underlying command-response protocol is SBP-2.

There are five annexes in this standard. Annexes and Error! Reference source not found. are normative and part of this standard. Annexes Error! Reference source not found., Error! Reference source not found., Error! Reference source not found. are informative and are not considered part of this standard.

Requests for interpretation, suggestions for improvement and addenda, or defect reports are welcome. They should be sent to the NCITS Secretariat, Information Technology Industry Council, 1250 I Street NW, Suite 200, Washington, DC 20005-3922.

This standard was processed and approved for submittal to ANSI by National Committee for Information Technology Standardization (NCITS). Committee approval of this standard does not necessarily imply that all committee members voted for approval. At the time it approved this standard, NCITS had the following members:

James D. Converse, Chair Donald C. Loughry, Vice-chair Joanne M. Flanagan, Secretary

| Organization Represented                                        | Name of Representative |

|-----------------------------------------------------------------|------------------------|

| American Nuclear Society                                        | . Geraldine C. Main    |

| AMP, Inc.                                                       |                        |

| Apple Computer                                                  | .Karen Higginbottom    |

| Association of the Institute for Certification of Professionals |                        |

| AT&T/NCR                                                        | .Thomas W. Kern        |

| Boeing Company                                                  | Catherine Howells      |

| Bull HN Information Systems, Inc.                               | . William George       |

| Compaq Computer Corporation                                     | . James Barnes         |

| Digital Equipment Corporation                                   | . Delbert Shoemaker    |

| Eastman Kodak                                                   |                        |

| GUIDE International                                             | . Frank Kirshenbaum    |

| Hewlett-Packard                                                 |                        |

| Hitachi America, Ltd                                            |                        |

| Hughes Aircraft Company                                         |                        |

| IBM Corporation                                                 |                        |

| National Communication Systems                                  |                        |

| National Institute of Standards and Technology                  |                        |

| Northern Telecom, Inc.                                          | -                      |

| Neville & Associates                                            |                        |

| Recognition Technology Users Association                        |                        |

| Share, Inc.                                                     |                        |

| Sony Corporation                                                |                        |

| Storage Technology Corporation                                  |                        |

| Sun Microsystems                                                |                        |

| 3M Company                                                      |                        |

| Unisys Corporation                                              |                        |

| US Department of Defense                                        |                        |

| US Department of Energy                                         | . Alton Cox            |

#### T10/97-260r0 Reduced Block Commands

| US General Services Administration | Douglas Arai  |

|------------------------------------|---------------|

| Wintergreen Information Services   | Joun Wheeler  |

| Xerox Corporation                  | Dwight McBain |

Technical Committee T10 on Lower Level Interfaces, which developed and reviewed this standard, had the following members:

John B. Lohmeyer, Chair Lawrence J. Lamers, Vice-chair Ralph O. Weber, Secretary

J. McGrath I. D. Allan P. D. Aloisi P. McLean G. Barton P. Mercer R. Bellino G. Milligan C. Brill C. Monia J. Chen D. Moore R. Cummings I. Morrell J. Moy Z. Daggett J. Dambach S. Nadershahi J. V. Dedek E. Oetting D. Pak E. Fong E. A. Gardner G. Penokie L. Grantham A. E. Pione D. Guss D. Piper K. J. Hallam R. Reisch N. Harris S. D. Schueler R. N. Snively E. Haske S. F. Heil G. R. Stephens C. E. Strang, Jr. S. Holmstead P. Johansson T. Totani G. Johnsen D. Wagner S. Jones D. Wallace T. J. Kulesza J. L. Williams E. Lappin M. Wingard R. Liu M. Yokoyama B. McFerrin

# **Revision history**

Revision 0 (October 13, 1997)

First release of working draft. Created from prior work performed by the SBP-2 adhoc working group during 1996 and 1997.

# American National Standard for Information Systems –

# Reduced Block Commands (RBC)

#### 1 Scope and purpose

#### 1.1 Scope

This standard defines the reduced command set extensions to facilitate operation of RBC units. The clause(s) of this standard implemented in conjunction with the applicable clauses of SPC-2, fully specify the command set for RBC logical units.

The objectives of the Reduced Block Command set standard is to provide the following:

- a) Permit a host to communicate with a logical unit that declares itself to be an RBC logical unit in the Device Type field of the INQUIRY command response data.

- b) Define a limited set of commands and supported fields unique to this class of block logical units.

- c) Define a limited set of control commands and supported fields to manage the operation of RBC logical units.

- d) Application of RBC to devices supporting SBP-2.

#### 1.2 Purpose

The purpose of this document is to provide a command set of reduced requirements and options from SBC for RBC logical units. The reduced command set is intended to more closely match the requirements and options necessary for simple block logical units. The command set is intended to place no restrictions on device performance. The initial focus of this command set is rigid disks and removable media devices attached to Serial Bus and utilizing SBP-2 for command and control.

#### 2 Normative references

The standards named in this section contain provisions which, through reference in this text, constitute provisions of this American National Standard. At the time of publication, the editions indicated were valid. All standards are subject to revision; parties to agreements based on this American National Standard are encouraged to investigate the possibility of applying the most recent editions of the standards indicated below.

Copies of the following documents can be obtained from ANSI:

Approved ANSI standards;

Approved and draft regional and international standards (ISO, IEC, CEN/CENELEC and ITUT); and

Approved and draft foreign standards (including BIS, JIS and DIN).

For further information, contact the ANSI Customer Service Department by telephone at (212) 642-4900, by FAX at (212) 302-1286 or *via* the world wide web at http://www.ansi.org.

Additional contact information for document availability is provided below as needed.

#### 2.1 Approved references

The following approved ANSI, international and regional standards (ISO, IEC, CEN/CENELEC and ITUT) may be obtained from the international and regional organizations that control them.

IEEE Std 1394-1995, Standard for a High Performance Serial Bus

ISO/IEC 13213:1994, Control and Status Register (CSR) Architecture for Microcomputer Buses

#### 2.2 References under development

At the time of publication, the following referenced standards were still under development.

IEEE P1394a, Draft Standard for a High Performance Serial Bus (Supplement)

T10 Project 1155D Serial Bus Protocol 2 (SBP-2)

T10 Project 1236D SCSI Primary Commands 2 (SPC-2)

#### 3 Keywords and Notation

#### 3.1 Keywords

Several keywords are used to differentiate levels of requirements and optionality, as follows:

- **3.1.1 expected:** A keyword used to describe the behavior of the hardware or software in the design models assumed by this standard. Other hardware and software design models may also be implemented.

- **3.1.2 ignored:** A keyword that describes bits, bytes, quadlets, octlets or fields whose values are not checked by the recipient.

- **3.1.3 mandatory:** A keyword that indicates items required to be implemented as defined by this standard.

- **3.1.4 may:** A keyword that indicates flexibility of choice with no implied preference.

- **3.1.5 non-volatile medium:** A physical storage medium that retains data written to it for a subsequent read operation through power off/on cycles. An example of this is a disk within a device that stores data as magnetic field changes that do not require device power to exist.

- **3.1.6 optional:** A keyword that describes features which are not required to be implemented by this standard. However, if any optional feature defined by the standard is implemented, it shall be implemented as defined by the standard.

- **3.1.7 shall:** A keyword that indicates a mandatory requirement. Designers are required to implement all such mandatory requirements to assure interoperability with other products conforming to this standard.

- **3.1.8 should:** A keyword that denotes flexibility of choice with a strongly preferred alternative. Equivalent to the phrase "is recommended."

#### 3.2 Glossary

The following terms are used in this standard:

- 3.2.1 byte: Eight bits of data.

- **3.2.2 command block:** Space reserved within an ORB to describe a command intended for a logical unit that controls device functions or the transfer of data to or from device medium. The format and meaning of command blocks are outside of the scope of SBP-2 and are command set- or device-dependent.

- **3.2.3 initial node space:** The 256 terabytes of Serial Bus address space that is available to each node. Addresses within initial node space are 48 bits and are based at zero. The initial node space includes initial memory space, private space, initial register space and initial units space. See either ISO/IEC 13213:1994 or IEEE Std 1394-1995 for more information on address spaces.

- **3.2.4 initial register space:** A two kilobyte portion of initial node space with a base address of FFFF F000 0000<sub>16</sub>. Core registers defined by ISO/IEC 13213:1994 are located within initial register space as are Serial Bus-dependent registers defined by IEEE Std 1394-1995.

- **3.2.5 initial units space**: A portion of initial node space with a base address of FFFF F000 0400<sub>16</sub>. This places initial units space adjacent to and above initial register space. The CSR's and other facilities defined by unit architectures are expected to lie within this space.

- **3.2.6 kilobyte:** A quantity of data equal to 2 <sup>10</sup> bytes.

- **3.2.7 logical unit:** The part of the unit architecture that is an instance of a device model, *e.g.*, mass storage, CD-ROM or printer. Targets implement one or more logical units; the device type of the logical units may differ.

- **3.2.8 login:** The process by which an initiator obtains access to a set of target fetch agents. The target fetch agents and their control and status registers provide a mechanism for an initiator to signal ORB's to the target.

- **3.2.9 octlet:** Eight bytes, or 64 bits, of data.

- **3.2.10 operation request block:** A data structure fetched from system memory by a target in order to execute the command encapsulated within it.

- **3.2.11 quadlet:** Four bytes, or 32 bits, of data.

- **3.2.12 receive:** When any form of this verb is used in the context of Serial Bus primary packets, it indicates that the packet is made available to the transaction or application layers, *i.e.*, layers above the link layer. Neither a packet repeated by the PHY nor a packet examined by the link is "received" by the node unless the preceding is also true.

- **3.2.13 register:** A term used to describe quadlet aligned addresses that may be read or written by Serial Bus transactions. In the context of this standard, the use of the term register does not imply a specific hardware implementation. For example, the behavior of registers may be emulated by a processor.

- **3.2.14 status block:** A data structure written to system memory by a target when an operation request block has been completed.

- **3.2.15 system memory:** The portions of any node's memory that are directly addressable by a Serial Bus address and which accepts, at a minimum, quadlet read and write access. Computers are the most common example of nodes that make system memory addressable from Serial Bus, but any node, including those usually thought of as peripheral devices, may have system memory.

- **3.2.16 transaction:** An exchange between a requester and a responder that consists of a request and a response subaction. The request subaction transmits a Serial Bus transaction such as quadlet read, block write or lock, from the requesting node to the node intended to respond. Some Serial Bus commands include data as well as transaction codes. The response subaction returns completion status and sometimes data from the responding node to the requesting node.

- **3.2.17 unit:** A component of a Serial Bus node that provides processing, memory, I/O or some other functionality. Once the node is initialized, the unit provides a CSR interface that is typically accessed by device driver software at an initiator. A node may have multiple units, which normally operate independently of each other. Within this standard, a unit is equivalent to a target.

- **3.2.18 unit architecture:** The specification of the interface to and the services provided by a unit implemented within a Serial Bus node. This standard is a unit architecture for SBP-2 targets.

- **3.2.19 unit attention:** A state that a logical unit maintains while it has unsolicited status information to report to one or more logged-in initiators. A unit attention condition shall be created as described elsewhere in this standard or in the applicable command set- and device-dependent documents. A unit

attention condition shall persist for a logged-in initiator until a) unsolicited status that reports the unit attention condition is successfully stored at the initiator or b) the initiator's login becomes invalid or is released. Logical units may queue unit attention conditions; after the first unit attention condition is cleared, another unit attention condition may exist.

#### 3.3 Abbreviations

The following are abbreviations that are used in this standard:

CDB Command descriptor block

CSR Control and status register

EUI-64 Extended Unique Identifier, 64-bits

ORB Operation request block

SBP-2 Serial Bus Protocol 2 (this standard itself)

#### 3.4 Conventions

The following conventions should be understood by the reader in order to comprehend this standard.

#### 3.4.1 Non-numeric values

- a) The names of abbreviations, commands, fields, and acronyms used as signal names are in all uppercase (e.g., IDENTIFY DEVICE).

- b) Fields containing only one bit are usually referred to as the "name" bit instead of the "name" field.

- c) If a field is specified as not meaningful or it is to be ignored, the entity that receives the field shall not check that field.

#### 3.4.2 Numeric values

Decimal, hexadecimal and, occasionally, binary numbers are used within this standard. By editorial convention, decimal numbers are most frequently used to represent quantities or counts. Addresses are uniformly represented by hexadecimal numbers. Hexadecimal numbers are also used when the value represented has an underlying structure that is more apparent in a hexadecimal format than in a decimal format. Binary numbers are used infrequently and generally limited to the representation of bit patterns within a field.

- a) Decimal numbers are represented by Arabic numerals without subscripts or by their English names.

- b) Hexadecimal numbers are represented by digits from the character set 0 9 and A F followed by the subscript 16.

- c) Binary numbers are represented by digits from the character set 0 and 1 followed by the subscript 2.

For the sake of legibility, binary and hexadecimal numbers are separated into groups of four digits separated by spaces.

As an example, 42, 2A<sub>16</sub> and 0010 1010<sub>2</sub> all represent the same numeric value.

## **4 Reduced Block Commands**

The Reduced Block Command set (RBC) for SCSI block device logical units is shown in Table 1. Each command is mandatory.

**Table 1 - Reduce Block Command Set**

| Command Name          | Opcode                  | Reference |  |

|-----------------------|-------------------------|-----------|--|

| INQUIRY               | 12 <sub>16</sub>        | SPC-2     |  |

| MODE SELECT           | <b>55</b> <sub>16</sub> | SPC-2     |  |

| MODE SENSE            | 5A <sub>16</sub>        | SPC-2     |  |

| READ (10)             | 28 <sub>16</sub>        | RBC       |  |

| START/STOP UNIT       | 1B <sub>16</sub>        | RBC       |  |

| SYNCHRONIZE CACHE     | 35 <sub>16</sub>        | RBC       |  |

| TEST UNIT READY       | 00 <sub>16</sub>        | SPC-2     |  |

| WRITE (10)            | 2A <sub>16</sub>        | RBC       |  |

| WRITE AND VERIFY (10) | 2E <sub>16</sub>        | RBC       |  |

| WRITE BUFFER          | 3B <sub>16</sub>        | SPC-2     |  |

The Control byte (the last byte of the Command Descriptor Bytes) is described in SBP-2, Annex Q. In addition, the supported field and bit values are defined.

# 4.1 READ(10) Command

The READ(10) command (see Table 2) requests that the device transfer data to the initiator. The most recent data value written in the addressed logical block shall be returned.

Table 2 - READ(10) command format

| Bit<br>Byte | 7     | 6                     | 5 | 4           | 3                        | 2    | 1     | 0        |

|-------------|-------|-----------------------|---|-------------|--------------------------|------|-------|----------|

| 0           |       |                       |   | Operation ( | Code (28 <sub>16</sub> ) |      |       |          |

| 1           |       | Reserved              |   | DPO = 0     | FUA = 0                  | Rese | erved | RelAdr=0 |

| 2           | (MSB) |                       |   |             |                          |      |       |          |

| 3           |       | •                     |   | Logical Blo | ck Address               |      |       |          |

| 4           |       | •                     | • |             |                          |      |       |          |

| 5           |       | •                     |   |             |                          |      |       | (LSB)    |

| 6           |       |                       |   | Rese        | erved                    |      |       |          |

| 7           | (MSB) | SB) Transfer Length   |   |             |                          |      |       |          |

| 8           |       | Transfer Length (LSB) |   |             |                          |      | (LSB) |          |

| 9           |       |                       |   | Cor         | ntrol                    |      |       |          |

The disable page out (DPO) bit shall be set to zero indicating that retention priority shall be determined by the device.

The Force Unit Access (FUA) bit shall be set to zero indicating that the device may satisfy the command by accessing the cache memory. For read operations, any logical blocks that are contained in the cache memory may be transferred to the initiator directly from the cache memory.

The Relative Address (RelAdr) bit is NOT supported.

The Logical Block Address field specifies the starting logical block address on the device for the read data to be accessed.

The Transfer Length field specifies the number of contiguous logical blocks of data that shall be transferred. A transfer length of zero indicates that no logical blocks shall be transferred. This condition shall not be considered an error. Any other value indicates the number of logical blocks that shall be transferred.

#### 4.2 START STOP UNIT Command

The START STOP UNIT command (see Table 3) requests that the device enable or disable the logical unit for media access operations and controls certain power conditions.

Table 3 - START STOP UNIT command format

| Bit<br>Byte | 7                                | 6                                  | 5 | 4    | 3     | 2 | 1     | 0     |

|-------------|----------------------------------|------------------------------------|---|------|-------|---|-------|-------|

| 0           |                                  | Operation Code (1B <sub>16</sub> ) |   |      |       |   |       |       |

| 1           |                                  |                                    |   | Rese | erved |   |       | Immed |

| 2           | Reserved                         |                                    |   |      |       |   |       |       |

| 3           | Reserved                         |                                    |   |      |       |   |       |       |

| 4           | Power Conditions Reserved LoEj S |                                    |   |      |       |   | Start |       |

| 5           | Control                          |                                    |   |      |       |   |       |       |

An *Immediate* (Immed) bit of one indicates that status shall be returned as soon as the command descriptor block has been validated. An *Immed* bit of zero indicates that status shall be returned after the operation is completed.

The power conditions field requests the logical unit to be placed into the power condition defined in Table 4. If this field contains any value other than  $0_{16}$  then the Start and the LoEj bits shall be ignored.

The logical unit may notify the initiator of the change of power state via unsolicited status, depending on the value of the unsolicited\_status\_enable variable.

**Table 4 - Power Condition Descriptions**

| Code                              | Description                    |  |  |  |  |

|-----------------------------------|--------------------------------|--|--|--|--|

| 0 <sub>16</sub>                   | No change in power conditions. |  |  |  |  |

| <b>1</b> <sub>16</sub>            | Place device in Active state   |  |  |  |  |

| 2 <sub>16</sub>                   | Place device in Idle state     |  |  |  |  |

| 3 <sub>16</sub>                   | Place device in Standby state  |  |  |  |  |

| 4 <sub>16</sub>                   | Reserved                       |  |  |  |  |

| <b>5</b> <sub>16</sub>            | Place device in Sleep state    |  |  |  |  |

| 6 <sub>16</sub> - F <sub>16</sub> | Reserved                       |  |  |  |  |

If the START STOP UNIT command is issued with the Power Conditions field set to 1<sub>16</sub>, 2<sub>16</sub>, or 3<sub>16</sub> the device shall terminate any command received that requires more power than allowed by the START

STOP UNIT command's most recent power condition setting with a CHECK CONDITION status, sense key of ILLEGAL REQUEST and sense code of POWER CONDITION ACTIVE.

If the START STOP UNIT command is issued with the Power Conditions field set to 5<sub>16</sub>, the device shall ignore the Immediate bit.

Prior to entering the Sleep state or executing the STOP UNIT command, a SYNCHRONIZE CACHE operation shall be performed.

It is not an error to request a device be placed into the same power state that it currently occupies.

The LOAD/EJECT (LoEi) bit shall NOT be supported by simple hard disk drives.

A *Start* bit of zero requests that the device be stopped (media shall not be accessed by the initiator). A *Start* bit of one request the device be made ready for use.

#### 4.3 SYNCHRONIZE CACHE Command

The SYNCHRONIZE CACHE command (see Table 5) ensures that logical blocks in cache have their most recent data value recorded on the physical medium. If a more recent data value for a logical clock exists in the cache memory than on the physical medium, then the logical block from the cache memory shall be written to the physical medium. Logical blocks are not necessarily removed from the cache memory as a result of the synchronize cache operation. The SYNCHRONIZE CACHE function is also required implicitly by other functions as defined in other clauses of this standard.

**Table 5 - SYNCHRONIZE CACHE command format**

| Bit<br>Byte | 7     | 6                                  | 5                                 | 4   | 3     | 2   | 1       | 0        |  |

|-------------|-------|------------------------------------|-----------------------------------|-----|-------|-----|---------|----------|--|

| 0           |       | Operation Code (35 <sub>16</sub> ) |                                   |     |       |     |         |          |  |

| 1           |       |                                    | Reserved                          |     |       | WCD | Immed=0 | RelAdr=0 |  |

| 2           | (MSB) |                                    | Logical Block Address = 0000 0000 |     |       |     |         |          |  |

| 3           |       | -                                  |                                   |     |       |     |         |          |  |

| 4           |       |                                    |                                   |     |       |     |         |          |  |

| 5           |       |                                    |                                   |     |       |     |         |          |  |

| 6           |       | Reserved                           |                                   |     |       |     |         |          |  |

| 7           | (MSB) |                                    | Number of Blocks = 0000           |     |       |     |         |          |  |

| 8           |       |                                    |                                   |     |       |     |         |          |  |

| 9           |       |                                    |                                   | Cor | ntrol |     |         |          |  |

A Write Cache Disable (WCD) bit of zero specifies that the device server may return GOOD status for a WRITE command after successfully receiving the data and prior to having successfully written it to the

medium. A WCD bit of one specifies that the device shall return GOOD status for a WRITE command after successfully writing all of the data to the medium.

The Immediate (Immed) bit is NOT supported.

The Relative Address (RelAdr) bit is NOT supported.

The Logical Block Address field is NOT supported.

The Number Of Blocks field is NOT supported.

## 4.4 WRITE(10) Command

The WRITE(10) command (see Table 6) requests that the device write data transferred from the initiator to the medium.

Table 6 - WRITE(10) command format

| Bit<br>Byte | 7     | 6                     | 5 | 4           | 3                        | 2    | 1     | 0        |

|-------------|-------|-----------------------|---|-------------|--------------------------|------|-------|----------|

| 0           |       |                       |   | Operation ( | Code (2A <sub>16</sub> ) |      |       |          |

| 1           |       | Reserved              |   | DPO = 0     | FUA                      | Rese | erved | RelAdr=0 |

| 2           | (MSB) |                       |   |             |                          |      |       |          |

| 3           |       | -                     |   | Logical Blo | ck Address               |      |       |          |

| 4           |       | -                     |   |             |                          |      |       |          |

| 5           |       | -                     |   |             |                          |      |       | (LSB)    |

| 6           |       |                       |   | Rese        | erved                    |      |       |          |

| 7           | (MSB) | Transfer Length       |   |             |                          |      |       |          |

| 8           |       | Transfer Length (LSB) |   |             |                          |      |       |          |

| 9           |       | Control               |   |             |                          |      |       |          |

The disable page out (DPO) bit shall be set to zero indicating that retention priority shall be determined by the device.

A Force Unit Access (FUA) bit of zero indicates that the device may satisfy the command by accessing the cache memory. For write operations, logical blocks may be transferred directly to the cache memory. GOOD status may be returned to the initiator prior to writing the logical blocks to the medium. Any error that occurs after the GOOD status is returned is a deferred error, and information regarding the error is not reported until a subsequent command.

An FUA bit of one indicates that the device shall access the media in performing the command prior to returning GOOD status. Write commands shall not return GOOD status until the logical blocks have actually been written on the media (i.e. the data is not write cached).

The Relative Address (RelAdr) bit is NOT supported.

The Logical Block Address field specifies the starting logical block address on the device for the read data to be accessed.

The Transfer Length field specifies the number of contiguous logical blocks of data that shall be transferred. A transfer length of zero indicates that no logical blocks shall be transferred. This condition shall not be considered an error. Any other value indicates the number of logical blocks that shall be transferred.

#### 4.5 WRITE AND VERIFY Command

The WRITE AND VERIFY command (see Table 7) requests that the device write the data transferred from the initiator to the medium and then verify that the data is correctly written. The data is only transferred once from the application client to the device server.

Table 7 - WRITE AND VERIFY command format

| Bit<br>Byte | 7     | 6                     | 5 | 4           | 3                        | 2     | 1        | 0        |

|-------------|-------|-----------------------|---|-------------|--------------------------|-------|----------|----------|

| 0           |       |                       |   | Operation ( | Code (2E <sub>16</sub> ) |       |          |          |

| 1           |       | Reserved              |   | DPO = 0     | Rese                     | erved | BytChk=0 | RelAdr=0 |

| 2           | (MSB) |                       |   |             |                          |       |          |          |

| 3           |       |                       |   | Logical Blo | ck Address               |       |          |          |

| 4           |       |                       |   |             |                          |       |          |          |

| 5           |       |                       |   |             |                          |       |          | (LSB)    |

| 6           |       |                       |   | Rese        | erved                    |       |          |          |

| 7           | (MSB) | Transfer Length       |   |             |                          |       |          |          |

| 8           |       | Transfer Length (LSB) |   |             |                          |       |          | (LSB)    |

| 9           |       |                       |   | Cor         | ntrol                    |       |          |          |

The disable page out (DPO) bit shall be set to zero indicating that retention priority shall be determined by the device.

The byte check (BytChk) bit shall be set to zero requesting a medium verification to be performed with no data comparison

The Relative Address (RelAdr) bit is NOT supported.

The Logical Block Address field specifies the starting logical block address on the device for the read data to be accessed.

The Transfer Length field specifies the number of contiguous logical blocks of data that shall be transferred. A transfer length of zero indicates that no logical blocks shall be transferred. This condition

shall not be considered an error. Any other value indicates the number of logical blocks that shall be transferred.

#### 4.6 MODE SELECT/SENSE page parameters

The RBC Device Parameters page is intended to provide general configuration information and to modify that configuration where necessary.

Table 8 -RBC Device Parameters Page Format (3E 16)

| Bit<br>Byte | 7      | 6    | 5                  | 4            | 3                       | 2                      | 1 | 0     |

|-------------|--------|------|--------------------|--------------|-------------------------|------------------------|---|-------|

| 0           | PS = 1 | Rsvd |                    |              | Page Co                 | de (3E <sub>16</sub> ) |   |       |

| 1           |        |      |                    | Page Le      | ngth (8 <sub>16</sub> ) |                        |   |       |

| 2           |        |      |                    | Reserved     |                         |                        |   | WCD   |

| 3           | (MSB)  |      | Logical Block Size |              |                         |                        |   |       |

| 4           |        |      |                    | Logical E    | Block Size              |                        |   | (LSB) |

| 5           | (MSB)  |      | N                  | lumber of Lo | ogical Block            | (S                     |   |       |

| 6           |        |      |                    |              |                         |                        |   |       |

| 7           |        |      |                    |              |                         |                        |   |       |

| 8           |        |      |                    |              |                         |                        |   |       |

| 9           |        |      | N                  | lumber of Lo | ogical Block            | (S                     |   | (LSB) |

Write Cache Enable (WCD) reflects the setting of the WCD bit in the SYNCHRONIZE CACHE command.

#### (This bit is NOT changeable)

The *Logical Block Size* field indicates the number of use data bytes contained in a logical block. **(This field is NOT changeable)**

The *Number of Logical Blocks* field indicates the number of logical blocks contained in the user data area. **(This field is changeable)**

NOTE – The default Number of Logical Blocks value may be obtained by requesting the Default Mode Sense data for this page. The current Number of Logical Blocks value may be obtained by requesting the Saved Mode Sense data for this page.

## Annex A

# **SPC-2 Compliance for Simple SBP-2 Disk Drives**

(Normative)

Table 9 - SPC-2 commands for simple SBP-2 Disk Drives

| Command Name    | Opcode           | Reference |

|-----------------|------------------|-----------|

| INQUIRY         | 12 <sub>16</sub> | SPC-2     |

| MODE SELECT     | 55 <sub>16</sub> | SPC-2     |

| MODE SENSE      | 5A <sub>16</sub> | SPC-2     |

| TEST UNIT READY | 00 <sub>16</sub> | SPC-2     |

| WRITE BUFFER    | 3B <sub>16</sub> | SPC-2     |

# A.1 MODE SELECT(10) Command

The MODE SELECT(10) command provides a means for the initiator to specify device parameters to the mass storage device. Devices shall also implement the MODE SENSE(10) command.

Table 10 - MODE SELECT(10) command format

| Bit<br>Byte | 7     | 6                           | 5 | 4         | 3                        | 2 | 1 | 0      |

|-------------|-------|-----------------------------|---|-----------|--------------------------|---|---|--------|

| 0           |       |                             |   | Operation | Code (55 <sub>16</sub> ) |   |   |        |

| 1           |       |                             |   | PF = 1    |                          |   |   | SP = 1 |

| 2           |       |                             |   | Rese      | erved                    |   |   |        |

| 3           |       |                             |   | Rese      | erved                    |   |   |        |

| 4           |       |                             |   | Rese      | erved                    |   |   |        |

| 5           |       |                             |   | Rese      | erved                    |   |   |        |

| 6           |       |                             |   | Rese      | erved                    |   |   |        |

| 7           | (MSB) | (MSB) Parameter list length |   |           |                          |   |   |        |

| 8           |       | Parameter list length (LSB) |   |           |                          |   |   |        |

| 9           |       |                             |   | Cor       | ntrol                    |   |   |        |

The Page Format (PF) bit shall be set to one, indicating that all parameters following the header are structured as pages of related parameters and are specified in this standard.

The Save Pages (SP) bit shall be set to one, indicating that the device shall perform the specified MODE SELECT operation and shall save, to a non-volatile vendor-specific location, all the *changeable* pages, including any sent with the command.

The Parameter List Length field specifies the length, in bytes, of the mode parameter list that shall be transferred in the MODE SELECT parameter read data request from the device. A Parameter List Length of zero shall not be considered an error.

If the Parameter List Length results in the truncation of any mode parameter header or mode page, the device shall terminate the command with CHECK CONDITION status, set the sense key to ILLEGAL REQUEST, and the sense code to PARAMETER LIST LENGTH ERROR.

The device shall terminate the MODE SELECT command with CHECK CONDITION status, set the sense key to ILLEGAL REQUEST, set the sense code to INVALID FIELDS IN PARAMETER LIST, and refrain from changing any mode parameters for the following conditions:

- a) If the initiator sets any field in the mode parameter header to an unsupported value.

- b) If an initiator sends a mode page with a page length not equal to the page length returned by the MODE SENSE command for that page;

- c) If the initiator sends an unsupported value for a mode parameter and rounding is not implemented for that parameter.

A device may alter any mode parameter in any mode page as a result of changes to other mode parameters.

The device shall NOT validate the non-changeable parameters against the current values that existed for those mode parameters prior to executing the MODE SELECT command.

# A.2 MODE SENSE(10) Command

Table 11 - MODE SENSE(10) command format

| Bit<br>Byte | 7     | 6                       | 5 4 3 2 1 |             |                          |      |  | 0 |

|-------------|-------|-------------------------|-----------|-------------|--------------------------|------|--|---|

| 0           |       |                         |           | Operation ( | Code (5A <sub>16</sub> ) |      |  |   |

| 1           |       |                         |           |             | DBD = 1                  |      |  |   |

| 2           | Р     | С                       |           |             | Page                     | Code |  |   |

| 3           |       |                         |           | Rese        | erved                    |      |  |   |

| 4           |       | Reserved                |           |             |                          |      |  |   |

| 5           |       |                         |           | Rese        | erved                    |      |  |   |

| 6           |       |                         |           | Rese        | erved                    |      |  |   |

| 7           | (MSB) | (MSB) Allocation length |           |             |                          |      |  |   |

| 8           |       | Allocation length (LSB) |           |             |                          |      |  |   |

| 9           |       |                         |           | Cor         | ntrol                    |      |  |   |

The Disable Block Descriptors (DBD) bit shall be set to one, indicating that the device shall not return any block descriptors in the returned MODE SENSE data.

The Page Control (PC) field defines the type of mode parameter values to be returned in the mode pages. The Page Control field is defined in Table 12.

Table 12 - Simple Hard Disk Page Control Values

| Code            | Type of parameter | Support       |

|-----------------|-------------------|---------------|

| 00 <sub>b</sub> | Current           | Optional      |

| 01 <sub>b</sub> | Changeable        | Not supported |

| 10 <sub>b</sub> | Default           | Mandatory     |

| 11 <sub>b</sub> | Saved             | Mandatory     |

$\mathsf{NOTE}-\mathsf{RBC}$  devices only support Saved and Default parameter values. Since the SP bit is required to be one for the MODE SELECT command, Current and Saved values are the same.

An initiator may request any one or all of the supported mode pages from the device. If an initiator issues a MODE SENSE command with a Page Code value not implemented by the device, the device shall return CHECK CONDITION status, set the sense key to ILLEGAL REQUEST and set the sense code to INVALID FIELD IN CDB.

A Page Code of  $3F_{16}$  indicates that all mode pages implemented by the device shall be returned to the initiator. If the mode parameter list exceeds 65 536 bytes, the device shall return CHECK CONDITION status, set the sense key to ILLEGAL REQUEST and set the sense code to INVALID FIELD IN CDB.

Mode pages should be returned in ascending Page Code order.

## A.2.1 Current Values (00 b)

If an RBC logical unit returns values when current values are requested, those values shall be the same as saved values.

# A.2.2 Changeable Values (01 b)

Changeable values shall not be supported by RBC logical units.

#### A.2.3 Default Values (10 b)

Unsupported parameters shall be set to zero. Default values should be accessible even if the device is not ready.

#### A.2.4 Saved Values (11 b)

Unsupported parameters shall be set to zero.

NOTE – The method of saving parameters is vendor-specific. The parameters shall be preserved in such a manner that they are retained when the device is powered down.

# A.2.5 Initial Response

After a power-up condition or hard reset condition, the device shall respond in the following manner:

- a) If default values are requested, report the default values;

- b) If saved values are requested, report valid restored mode parameters, or restore the mode parameters and report them. If the saved values of the mode parameters are not able to be accessed from the non-volatile vendor-specific location, terminate the command with CHECK CONDITION status and set the sense key to NOT READY.

- c) If current values are requested, report saved values as described in b).

#### A.3 TEST UNIT READY Command

The TEST UNIT READY command (see Table 13) provides a means to check if the device is ready. This is not a request for a self-test. If the device is able to accept an appropriate medium-access command without returning CHECK CONDITION status, this command shall return GOOD status. If the device cannot become operational or is in a state such that an application client action (e.g., START UNIT command) is required to make the unit ready, the device shall return CHECK CONDITION status with a sense key of NOT READY.

Table 13 - TEST UNIT READY command format

| Bit<br>Byte | 7 | 7 6 5 4 3 2 1 0 |  |             |                          |  |  |  |

|-------------|---|-----------------|--|-------------|--------------------------|--|--|--|

| 0           |   |                 |  | Operation ( | Code (00 <sub>16</sub> ) |  |  |  |

| 1           |   |                 |  | Rese        | erved                    |  |  |  |

| 2           |   | Reserved        |  |             |                          |  |  |  |

| 3           |   |                 |  | Rese        | erved                    |  |  |  |

| 4           |   | Reserved        |  |             |                          |  |  |  |

| 5           |   | Control         |  |             |                          |  |  |  |

Table 14 defines the suggested GOOD and CHECK CONDITION status responses to the TEST UNIT READY command. Other conditions, including deferred errors, may result in other responses (e.g., BUSY status).

RBC devices shall report SMART status via the TEST UNIT READY status response. The required Key, Code and ASCQ values are described in Table 14 and Table 15.

Table 14 - Preferred TEST UNIT READY sense values

| Status                             | Sense Key                          | ASC, ASCQ                                                             |

|------------------------------------|------------------------------------|-----------------------------------------------------------------------|

| 00 <sub>16</sub> - Good            | 00 <sub>16</sub> - No Sense        | 00 <sub>16</sub> , 00 <sub>16</sub> - No additional sense information |

| 02 <sub>16</sub> - Check Condition | 05 <sub>16</sub> - Illegal Request | 25 <sub>16</sub> , 00 <sub>16</sub> - Logical Unit not supported      |

| 02 <sub>16</sub> - Check Condition | 02 <sub>16</sub> - Not Ready       | $04_{16}$ , $00_{16}$ - Logical Unit not ready cause not reportable   |

| 02 <sub>16</sub> - Check Condition | 02 <sub>16</sub> - Not Ready       | 04 <sub>16</sub> , 01 <sub>16</sub> - Logical Unit becoming ready     |

| 02 <sub>16</sub> - Check Condition | 01 <sub>16</sub> - Recovered Error | 5D <sub>16</sub> , <sup>1</sup> - SMART threshold exceeded,           |

NOTE 1 - See Table 15 for SMART ASCQ responses.

Table 15 - SMART ASCQ values

| Value                               | Definition                                     |

|-------------------------------------|------------------------------------------------|

| X0 <sub>16</sub>                    | General hard drive failure                     |

| X1 <sub>16</sub>                    | Drive Error threshold exceeding limits.        |

| X2 <sub>16</sub>                    | Data Error Rate exceeding limits.              |

| X3 <sub>16</sub>                    | Seek Error Rate exceeding limits.              |

| X4 <sub>16</sub>                    | LBA reassignment exceeding limits.             |

| X5 <sub>16</sub>                    | Access Times exceeding limits.                 |

| X6 <sub>16</sub>                    | Start Unit Times exceeding limits.             |

| X7 <sub>16</sub>                    | Channel parametrics indicate impending failure |

| X8 <sub>16</sub>                    | Controller detected impending failure.         |

| X9 <sub>16</sub>                    | Throughput performance                         |

| $XA_{16}$                           | Seek time performance                          |

| XB <sub>16</sub>                    | Spin-up retry count                            |

| XC <sub>16</sub>                    | Drive calibration retry count                  |

| 0D <sub>16</sub> - 0F <sub>16</sub> | Reserved                                       |

| 1X <sub>16</sub>                    | Hardware impending failure                     |

| 2X <sub>16</sub>                    | Controller impending failure                   |

| 3X <sub>16</sub>                    | Data Channel impending failure                 |

| 4X <sub>16</sub>                    | Servo impending failure                        |

| 5X <sub>16</sub>                    | Spindle impending failure                      |

| 6X <sub>16</sub>                    | Firmware impending failure                     |

| 7X <sub>16</sub> - FX <sub>16</sub> | Reserved                                       |

# A.4 WRITE BUFFER Command

The WRITE BUFFER command (see Table 16) is used to download and save microcode.

**Table 16 - WRITE BUFFER command format**

| Bit<br>Byte | 7     | 6       | 5             | 4           | 3                        | 2 | 1    | 0     |

|-------------|-------|---------|---------------|-------------|--------------------------|---|------|-------|

| 0           |       |         |               | Operation ( | Code (3B <sub>16</sub> ) |   |      |       |

| 1           |       |         | Reserved      |             |                          |   | Mode |       |

| 2           |       |         |               | Buffe       | er ID                    |   |      |       |

| 3           | (MSB) |         |               |             |                          |   |      |       |

| 4           |       | •       | Buffer Offset |             |                          |   |      |       |

| 5           |       |         |               |             |                          |   |      | (LSB) |

|             | (MSB) |         |               |             |                          |   |      |       |

| 7           |       |         |               | Parameter   | List Length              |   |      |       |

| 8           |       | (LSB)   |               |             |                          |   |      | (LSB) |

| 9           |       | Control |               |             |                          |   |      |       |

The function of this command and the meaning of the fields within the command descriptor block depend on the contents of the Mode field. The Mode field is defined in Table 17.

Table 17 - WRITE BUFFER Mode field

| Mode             | Description                             | Implementation<br>Requirements |

|------------------|-----------------------------------------|--------------------------------|

| 000 <sub>b</sub> | Write combined header and data          | Not Supported                  |

| 001 <sub>b</sub> | Vendor specific                         | Vendor specific                |

| 010 <sub>b</sub> | Write data                              | Not Supported                  |

| 011 <sub>b</sub> | Reserved                                | Reserved                       |

| 100 <sub>b</sub> | Download microcode                      | Not Supported                  |

| 101 <sub>b</sub> | Download microcode and save             | Mandatory                      |

| 110 <sub>b</sub> | Download microcode with offset          | Not Supported                  |

| 111 <sub>b</sub> | Download microcode with offset and save | Not Supported                  |

## A.4.1 Download Microcode and Save Mode (101 b)

If the logical unit cannot accept this command because of some device condition, the device shall terminate each WRITE BUFFER command with this mode (101<sub>b</sub>) with a CHECK CONDITION status, a sense key of ILLEGAL REQUEST, and an additional sense code of COMMAND SEQUENCE ERROR.

In this mode, vendor-specific microcode or control information shall be transferred to the device and, if the WRITE BUFFER command is completed successfully, also shall be saved in a non-volatile memory space (semiconductor, disk, or other). the downloaded code shall then be effective after each power-cycle and reset until it is supplanted in another download microcode and save operation. The meaning of the Buffer ID, Buffer Offset, and Parameter List Length fields are not specified by this standard and are not required to be zero filled. When the download microcode and save command has completed successfully the device server shall generate a Unit Attention status block and send it, via unsolicited status, to all initiators except the one that issued the WRITE BUFFER command. When reporting the Unit Attention condition, the device shall set the additional sense code to MICROCODE HAS BEEN CHANGED.

#### A.5 Event Status Notification

Previous mass storage device interfaces have been unable to consistently and reliably support asynchronous event notification. As a substitute, initiators have used the GET EVENT STATUS NOTIFICATION command to acquire asynchronous event status from devices. The GESN command was used to either poll the device's event status or, if the device supported queued commands, the GESN command did not complete until an event occurred. The polling method requires the initiator to provide a timer in order to repetitively acquire device status. The queued command method requires a device to process the GESN command in a different manner from all other queued commands. To solve this problem asynchronous event notification has been made a fundamental part of SBP-2 and RBC devices.

Through the use of Unsolicited Status, mass storage devices may report asynchronous events the moment that they occur. The initiator need only process the status block to determine the cause of the event. The device is no longer required to support the GESN command in the polled or queued mode. It simply builds and transmits a status block whenever an event occurs.

#### A.5.1 Unsolicited Status Sense Definitions

The following table describes unsolicited status sense key and sense code values that may be written to an initiator's Status\_FIFO if the initiator has previously written to the device's unsolicited\_status\_enable register.

Table 18 - Unsolicited Status Sense Key/Code Values

| Sense            | Sense                   | Description                                                    |  |

|------------------|-------------------------|----------------------------------------------------------------|--|

| Key              | Code                    |                                                                |  |

| 02 <sub>16</sub> | 04 <sub>16</sub>        | Device Not Ready (reported only on transition or at power on.) |  |

| 06 <sub>16</sub> | <b>28</b> <sub>16</sub> | Not Ready to Ready transition. Medium may have changed         |  |

| 06 <sub>16</sub> | 29 <sub>16</sub>        | Power on reset, bus reset, etc.                                |  |

Deferred errors may also be reported as unsolicited status.

#### A.5.1.1 Event Status Sense Information

In order to support traditional Event Status Notification through the use of Unsolicited Status, specific Status, Sense Key, and Sense Code values must be combined.

Status = 02<sub>16</sub>, Check Condition, indicates that the condition of the device has changed.

Sense Key =  $06_{16}$ , Unit Attention, indicates that an event has occurred that the device must communicate to the initiator.

Sense Code = 7F<sub>16</sub>, Event Status Notification, indicates that an asynchronous event has occurred.

Sense Qualifier values are:

- 02<sub>16</sub>, Power Management Class Event, indicates that a Power Management event has occurred.

- 04<sub>16</sub>, Media Class Event, indicates that a Media Class event has occurred.

- 06<sub>16</sub>, Device Busy Class Event, indicates that a Device Busy Class event has occurred.

The contents of the Information field further define the event status. Interpretation of the values are dependent upon the Sense Key, Code, and Qualifier values. The following tables provide the Event Status Information values for each Sense Qualifier type described above.

| information |                             |  |  |  |  |  |

|-------------|-----------------------------|--|--|--|--|--|

| byte 0      | byte 0 byte 1 byte 2 byte 3 |  |  |  |  |  |

| event       | event specific              |  |  |  |  |  |

**Figure 1 - Event Status Information Format**

# A.5.1.2 Power Management Information Values

| information                    |  |  |  |  |  |

|--------------------------------|--|--|--|--|--|

| byte 0 byte 1 byte 2 byte 3    |  |  |  |  |  |

| event status reserved reserved |  |  |  |  |  |

Figure 2 - Power Management Information Format

**Table 19 - Power Management Information Values - Event Field**

| Event Field                         | Description                                                                                                                        |  |  |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 00 <sub>16</sub>                    | No power state change                                                                                                              |  |  |

| 01 <sub>16</sub>                    | The device successfully changed to the specified power state.                                                                      |  |  |

| 02 <sub>16</sub>                    | The device failed to enter the last requested power state and is still operating at the state specified in the Power Status field. |  |  |

| 03 <sub>16</sub> - FF <sub>16</sub> | Reserved                                                                                                                           |  |  |

Table 20 - Power Management Information Values - Status Field

| Status Field                        | Description                        |  |  |

|-------------------------------------|------------------------------------|--|--|

| 0016                                | Reserved                           |  |  |

| 01 <sub>16</sub>                    | The device is in the Active state  |  |  |

| 02 <sub>16</sub>                    | The device is in the Idle state    |  |  |

| 03 <sub>16</sub>                    | The device is in the Standby state |  |  |

| 04 <sub>16</sub> - FF <sub>16</sub> | Reserved                           |  |  |

# A.5.1.3 Media Event Information Values

| information                      |                             |  |  |  |  |  |

|----------------------------------|-----------------------------|--|--|--|--|--|

| byte 0                           | byte 0 byte 1 byte 2 byte 3 |  |  |  |  |  |

| event status start slot end slot |                             |  |  |  |  |  |

**Figure 3 - Media Event Information Format**

Table 21 - Media Event Information Value - Event Field

| Event Field                         | Description                                                                                                                               |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 0016                                | Media status is unchanged                                                                                                                 |

| 01 <sub>16</sub>                    | Eject request. The user has issued a request to eject the slot or media                                                                   |

| 02 <sub>16</sub>                    | The specified slot has received new media and the media is ready to be accessed.                                                          |

| 03 <sub>16</sub>                    | Media Removal. The media has been removed from the specified slot and the target is unable to access the media without user intervention. |

| 04 <sub>16</sub> - FF <sub>16</sub> | Reserved                                                                                                                                  |

Table 22 - Media Event Information Value - Status Field

| Bit<br>Byte | 7 | 6 | 5    | 4     | 3 | 2 | 1                | 0                       |

|-------------|---|---|------|-------|---|---|------------------|-------------------------|

| 1           |   |   | Rese | erved |   |   | Media<br>Present | Door or<br>Tray<br>Open |

The **Door or Tray Open bit** indicates the mechanical position of the device's door or tray. A **Door or Tray Open** value of 1 indicates that the door or tray is open. A value of 0 indicates that the door or tray is closed.

The **Media Present** bit indicates whether media is installed in the device. A value of 1 indicates that media is present in the device. A value of 0 indicates that no media is present. The **Media Present** bit is reported independently from the Door or Tray Open bit. If the device cannot report the media state while the door or tray is open, this bit shall be set to 0 when the Door or Tray Open bit is 0.

The **Start Slot** field defines the first slot of a multiple slot device that the media status notification applies to. For devices that do not support multiple slots, this field shall be reserved.

The **End Slot** field defines the last slot of a multiple slot device that the media status notification applies to. For devices that do not support multiple slots, this field shall be reserved.

# A.5.1.4 Device Busy Event Information Values

| information                 |        |            |            |  |  |

|-----------------------------|--------|------------|------------|--|--|

| byte 0 byte 1 byte 2 byte 3 |        |            |            |  |  |

| event                       | status | Time (MSB) | Time (LSB) |  |  |

**Figure 4 - Device Busy Information Format**

Table 23 - Device Busy Event Information Values - Event Field

| Event Field                         | Description             |  |  |

|-------------------------------------|-------------------------|--|--|

| 0016                                | No event is available   |  |  |

| 01 <sub>16</sub>                    | A time-out has occurred |  |  |

| 02 <sub>16</sub> - FF <sub>16</sub> | Reserved                |  |  |

Table 24 - Device Busy Event Information Values - Status Field

| Status Field                        | Description                                                                       |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------|--|--|

| 0016                                | No event. The device is ready to accept commands                                  |  |  |

| 01 <sub>16</sub>                    | The device is in the process of waking up from a lower power state                |  |  |

| 02 <sub>16</sub>                    | The device is in the process of completing an earlier command                     |  |  |

| 03 <sub>16</sub>                    | The device is in the process of completing a deferred operation, such as a write. |  |  |

| 04 <sub>16</sub> - FF <sub>16</sub> | Reserved                                                                          |  |  |

The **Time** field is the predicted amount of time remaining for the device to become not busy, in unit of 100ms.

#### Annex B

#### **RBC Logical Unit Configuration ROM Requirements**

(normative)

Although most Configuration ROM entries are generic, several contain information that is specific to each device type. Hard disk drive specific Configuration ROM information is defined in this section.

## **B.1 Unit Directory - Command\_Set**

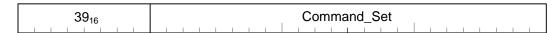

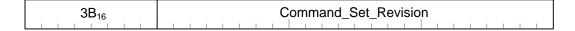

The  $Command\_Set\ entry\ (key\ -\ 3A_{16})$  is an immediate entry that, in combination with the  $Command\_Set\_Spec\_ID$  entry specifies the command set supported by the unit.