THE ELEMENTS OF SPI-2 ARE TAKING SHAPE:

- A BASIC INTERFACE ARCHITECTURE IS PROPOSED

- SUPPORTS BOTH SE AND DF IN THE SAME SILICON

- USES THE SAME CONNECTORS AND CABLES AS SPI/FAST 20

- AUTODETECTS TRANSMISSION SCHEME BEING USED AND SETS TRANSCEIVERS ACCORDINGLY

- REQUIRES FULL DF PATH EVERYWHERE FOR DF BUT IS COMPATIBLE WITH A SE ONLY (COMMONED GROUNDS ETC) OR DF PATH (BOTH + AND - SIGNALS) FOR SE

- HAS BETTER REAL COMMON MODE PERFORMANCE THAN TODAY'S DF

- REPINS THE DF TO BE FUNCTIONALLY COMPATIBLE WITH SE

THE ELEMENTS OF SPI-2 ARE TAKING SHAPE:

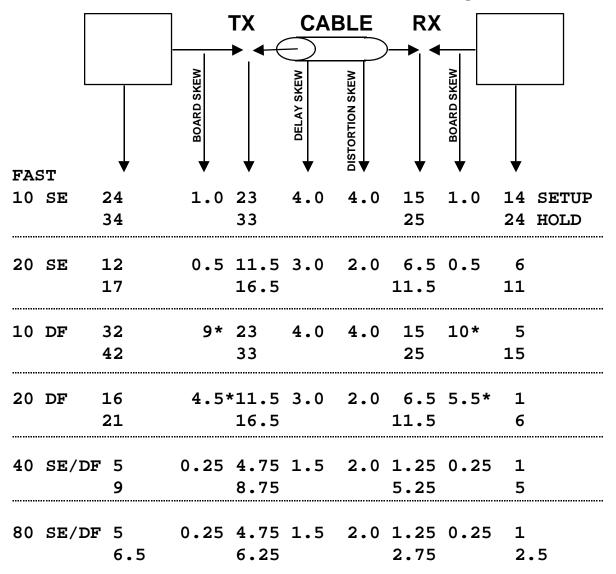

- A TIMING BUDGET FOR FAST 40 AND FAST 80 IS PROPOSED

- BUILDS OFF THE PRESENT FAST 20 DF RECEIVER TIMINGS

- PRESERVES ALL THE FAST 20 PULSE

DISTORTION SKEW

- RECLAIMS HALF OF THE "FAT" IN THE PRESENT CABLE SKEW (SAME CABLES)

- GAINS MUCH FROM THE ELIMINATION OF SEPARATE TRANSCEIVERS

- THE VHDCI CONNECTION SCHEME IS STABILIZING FOR CABLED CONNECTIONS

- THE SCA-2 DEVICE CONNECTOR IS STABILIZING

- NEW UNIVERSAL AUTOSENSE TERMINATORS ARE PROPOSED

BILL HAM DIGITAL EQUIPMENT SPI-2 WORKING GROUP JULY 10, 1995

THE ELEMENTS OF SPI-2 ARE TAKING SHAPE:

- COST IMPACTS OF "EXTRA" PINS HAVE BEEN ADDRESSED

- THE MAJOR IMPACTS OF 3.3 VOLT SUPPLIES HAVE BEEN ADDRESSED:

- DROPOUT VOLTAGES FOR SE TERMINATORS

- EFFECTS OF TERMPWR DISTRIBUTION

- CHIP INPUT LEVELS

- COMPLETE DIFFSENS STRATEGY IS PROPOSED (INCLUDING LOW FREQUENCY GROUND SHIFT)

- HIGH FREQUENCY COMMON MODE

ACTUALLY BETTER THAN WITH HIGH

POWER DIFFERENTIAL

#### **SETUP AND HOLD TIMINGS**

PROTOCOL CHIP

PROTOCOL CHIP

\* INCLUDES SEPARATE TRANSCEIVER SKEW

BILL HAM DIGITAL EQUIPMENT SPI-2 WORKING GROUP JULY 10, 1995

**COST IMPACT OF "EXTRA PINS"**

- WIDE DIFFERENTIAL REQUIRES MORE PINS THAN SINGLE ENDED (APPROX 20 - NOT 27 - MORE) -- ALL SIGNALS, EVEN "LOW SPEED" CONTROL SIGNALS NEED TO BE DIFFERENTIAL

- FAST 40/80 REQUIRES DIFFERENTIAL

- A UNIVERSAL SCSI INTERFACE MUST SUPPORT DIFFERENTIAL

- THEREFORE THE UNIVERSAL SOLUTION IMPOSES A COST PREMIUM FOR SINGLE ENDED ONLY APPLICATIONS DUE TO THE PIN COUNT INCREASE

- THIS COST NEEDS TO BE UNDERSTOOD AND WEIGHED AGAINST THE BENEFITS OF NOT NEEDING MULTIPLE SCSI INTERFACES

- ESTIMATES OF THE CHIP PACKAGING ARE:

160 SE VS 180 DF PINS FOR 32 BIT PCI HOST CHIPS 144 SE VS 164 DF PINS FOR TARGET CHIPS ~208 SE VS 230 DF PINS FOR 64 BIT PCI HOST CHIPS

THIS DRIVES ~\$1 TO 3 INCREASE / INTERFACE FOR THE UNIVERSAL SOLUTION

**KEY QUESTION:**

HOW SHOULD WE ADDRESS THE INCREASING PROTOCOL OVERHEAD AS THE DATA PHASE SPEED INCREASES??

HOW MUCH OF THIS OVERHEAD IS PROTOCOL LIMITED AND HOW MUCH IS IMPLEMENTATION INEFFECIENCY??

CAN WE GAIN MAJOR OVERHEAD REDUCTIONS BY REDUCING THE OVERALL PROPAGATION DELAY RELATED PARAMETERS (IN EFFECT BY REDUCING THE BUS LENGTH)??

DO WE NEED A NEW MESSAGING SYSTEM??

SHOULD THIS BE A SPI-2 ISSUE??

BILL HAM DIGITAL EQUIPMENT SPI-2 WORKING GROUP JULY 10, 1995