T10/07-304r2 Zero-Length Test Load TextSAS-2 Zero-Length Test Load Section

To: T10 Technical Committee

From: Barry Olawsky, HP (barry.olawsky@hp.com)

Date: 10 July 2007

Subject: T10/07-304r2 SAS-2 Zero-Length Test Load Section

## **Revision History**

Revision 0 (3 July 2007) first revision

Revision 1 (10 July 2007) added comments after July 5<sup>th</sup> conference call. Mostly editorial.

Modified equation to allow for VNA calibration tolerance at low frequencies.

Revision 2 (10 July 2007) includes editorial changes made at July 10<sup>th</sup> face-to-face.

## **Related Documents**

sas2r10.pdf - Serial Attached SCSI 2 revision

07-013R6 SAS-2 Zero-Length Test Load Characterization (Barry Olawsky, Hewlett Packard)

#### **Overview**

Physically implementable zero-length test loads are not ideal. Measurement errors induced by the zero-length test load can be removed by de-embedding although the procedure is not ideal itself. Compliance of fixturing to some performance standards will reduce the measurement error and improve the accuracy of de-embedding.

## Suggested Changes

Replace the zero-length test load section with the following text and graphics.

#### 1.1.1.1 Zero-length test load

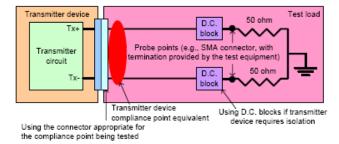

Figure 105 shows the zero-length test load as used for testing a transmitter device compliance point.

Figure 105 — Zero-length test load for transmitter device compliance point

#### Figure 105 — Zero-length test load for transmitter device compliance point

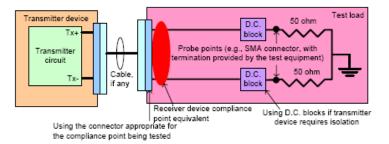

Figure 106 shows the zero-length test load as used for testing a receiver device compliance point.

#### T10/07-304r2 Zero-Length Test Load TextSAS-2 Zero-Length Test Load Section

Figure 106 — Zero-length test load for receiver device compliance point Test loads in a figure 105 and figure 106 show ideal designs. Actual designs include: Deleted: Physically implementable insertion loss between the compliance and probe points; and Formatted: Bullets and Numbering return loss due one or more impedance mismatches between the compliance point and 50 ohm termination points. Deleted: s Not shown are non-ideal effects of the test equipment raw measurements (e.g., additional Deleted: Also n insertion and return loss). For de-embedding methods to remove non ideal effects see annex B Deleted: such as Deleted: Refer to <u>U</u>sage of fixturing and test equipment <u>shall comly with the requirements defined in this subclause</u> The requirements in this subclause include, the combined effects of the fixturing and test Deleted: Annex B f equipment. Deleted: such effects NOTE: The zero-length test load performance specifications defined in this subclause were not Deleted: Since the de-embedding process can be difficult to perform required for previous versions of this standard accurately, u Deleted: that complies with the following specification is 50021 (f) recommended Deleted: is specification applies to Deleted: ¶ SAMPLE VALID ZERO-LENGTH TEST LOAD

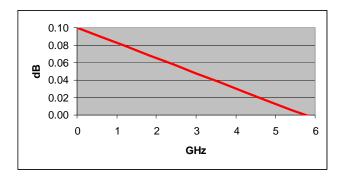

6,0 GH2 > f

-4d B

|   | Figure X, Zero-Length Sdd21 ◆                                                                                                                                            | Formatted: Centered |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| I | The zero-length test load, including all fixturing and instrumentation required for the                                                                                  | Deleted: (          |

| I | measurement, shall comply with the following equations:                                                                                                                  | Deleted: )          |

|   | For 10 MHz <= f <= 6,0 GHz:                                                                                                                                              |                     |

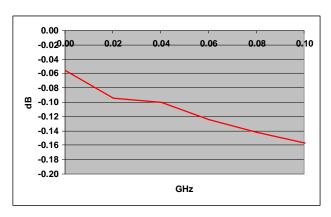

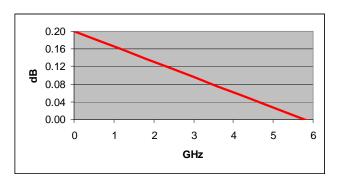

|   | $ SDD21(f)  \ge = -20 \log_{10}(e) \times ((1,0 \times 10-6 \times f_{0,5}) + (3,2 \times 10-11 \times f) + (5,3 \times 10-21 \times f_{2})) dB $ (see figure $\times$ ) | Deleted: <          |

| I | SDD11(f)                                                                                                                                                                 | Deleted: >          |

# THE FOLLOWING INFORMATION IS DISCUSSION PURPOSES ONLY. IT IS NOT TO BE INCLUDED IN THE SPECIFICATION.

Adding a DC loss of 0.1dB and rescalling the "f" term to "3" to force 4.0dB loss at 6GHz the additional margin is:

Adding a DC loss of 0.1dB and rescalling the "f" term to "2.8" to force 4.0dB loss at 6GHz the additional margin is:

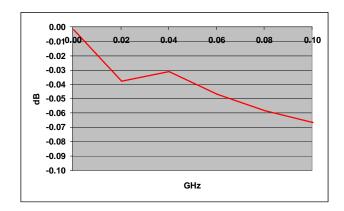

T10/07-304r2 Zero-Length Test Load TextSAS-2 Zero-Length Test Load Section The original fixture sample data at low frequencies is as follows:

Case 1:

Case 2: