Barry Olawsky

Hewlett Packard

(2/22/2007)

### Zero-Length Test Load

- Provides ideal connection between compliance point and instrumentation reference plane.

- May consist of printed circuit board traces, connectors and cables

- Trace structure variations of width, length and dielectric material are typical. Test board designs need to meet impedance targets but exact effect of insertion loss is considered negligible but usually unknown

- Connector footprint variations are a common source of varied test board performance.

- Instrumentation cables vary in length, insertion loss, termination quality and type (rigid, semi-rigid, hand-formable, etc)

- These effects can be de-embedded when using some instrumentation but can not with most

#### Zero-Length Test Load Misconceptions

- All good quality SMA cables have similar electrical characteristics

- If you use connector footprint provided in the standard you will meet the impedance specifications of the standard

- The common mode impedance of trace structures on the test fixture has no effect. Only the differential impedance is important.

#### Challenges of Characterization

- Some compliance points utilize connectors while others don't.

How do we account for these differences?

- Of those that use connectors not all are the same

- Connector and IC component footprints dictate PCB routing methodology

- Must resolve the discrepancies or de-embed the PCB effects

#### Challenges of Characterization

- To limit the insertion loss variations an S<sub>21</sub> mask is one possible approach. This approach is problematic if other parameters are less than ideal

- Can we make that assumption?

- Just how good do the other parameters have to be?

- Simulations can help answer this question

#### Measurement Objectives

- Network analyzer measurements are suited to deembedding. Frequency limitations exist with calibration structures but we may be below those limits

- Time domain instrumentation (oscilloscope) does not yet have the same level of de-embedding features

- Need to evaluate each usage case for zero-length test load and determine what specifications are necessary and appropriate

# Test Fixture Budgeting (Early Targets)

|                | Printed Circuit<br>Board | Cable                | Connectors & Footprints |

|----------------|--------------------------|----------------------|-------------------------|

| Insertion Loss | < 2dB @ 3GHz             | < 1dB @ 3GHz         | < 1dB @ 3GHz            |

| Return Loss    | < -20dB thru<br>3GHz     | < -30dB thru<br>3GHz | < -15dB thru<br>3GHz    |

| Conversion     | < -30dB thru<br>3GHz     | < -30dB thru<br>3GHz | < -30dB thru<br>3GHz    |

| Common Mode    | ?                        | Not Applicable       | ?                       |

Since most of these parameters are sensitive to interaction with other components, individual budgeting is of minimal value beyond a first guess estimate

#### **Next Actions**

- The biggest issue is probably how to specify parameters that will yield consistent zero-length fixtures. Simulations should help.

- Zero-length specification should be influenced by the types of measurements to be performed in SAS-2. We must consider each type.

### Simulation Approach

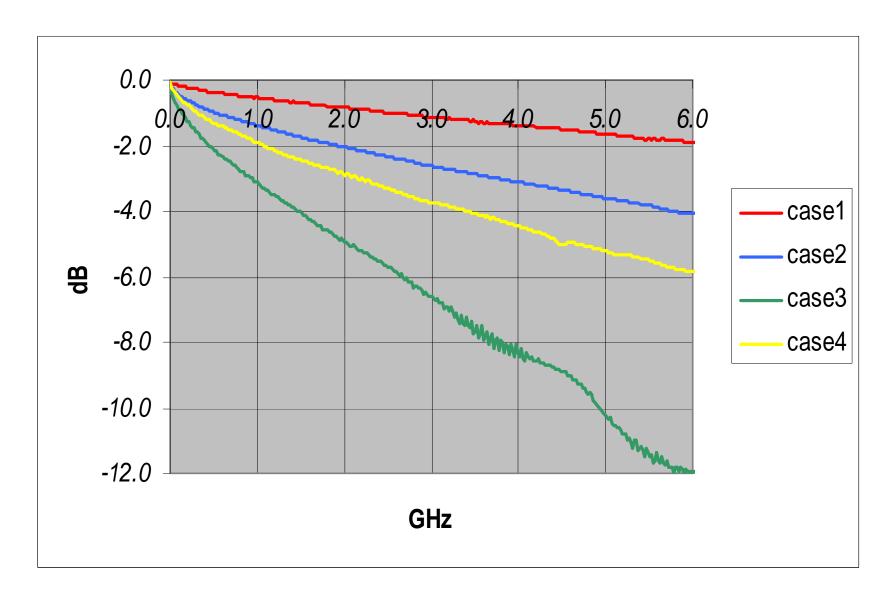

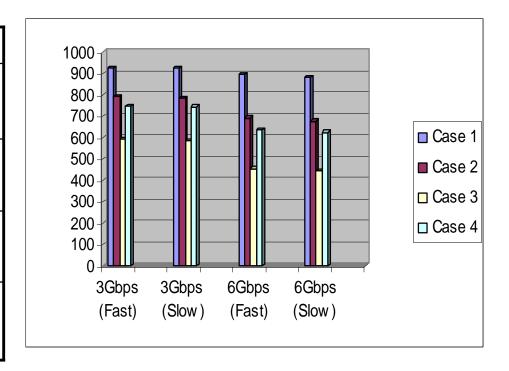

- Three different fixtures will be considered

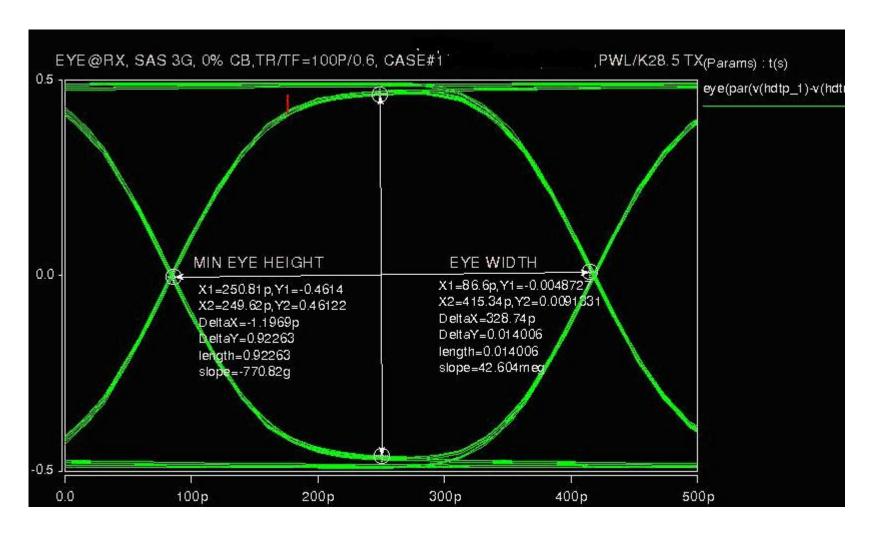

- Case #1: Lowest insertion loss (short trace, SMA launch and bulky 24 inch instrumentation cable)

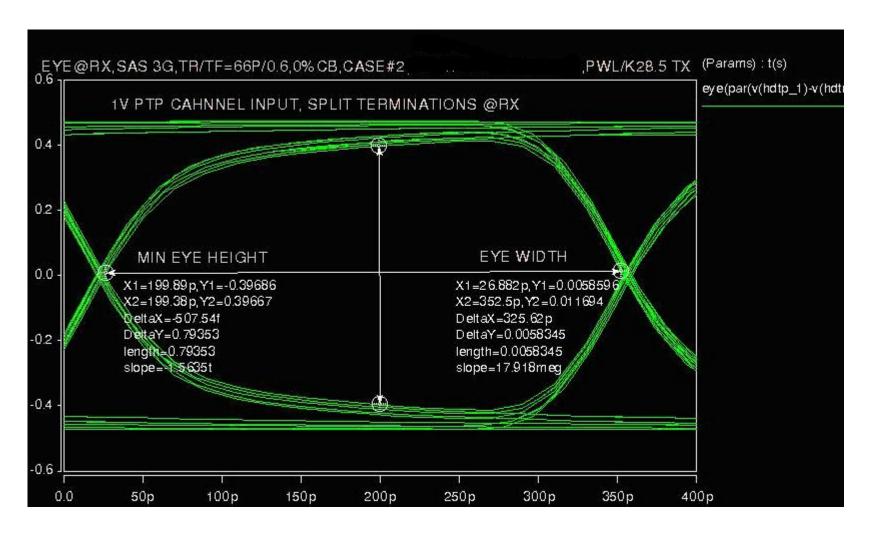

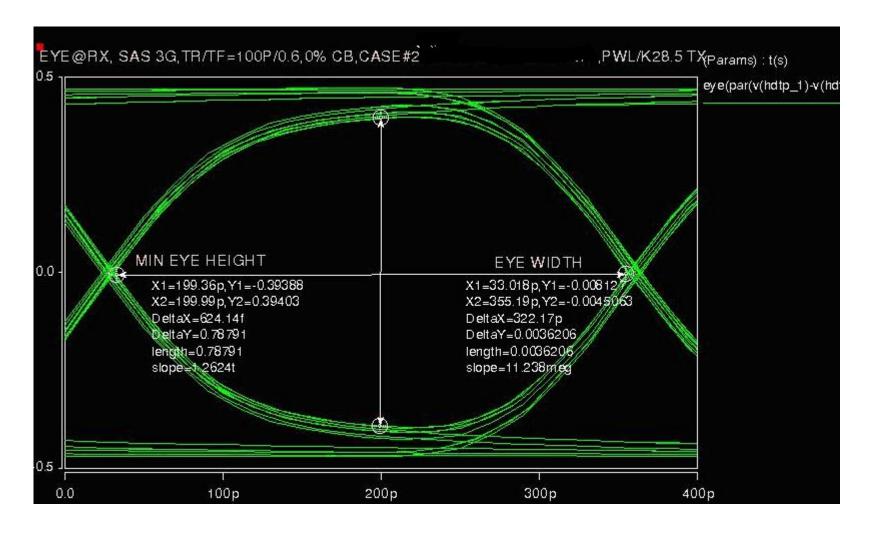

- Case #2: Lowest return loss (slightly longer trace, better SMA launch and thin 1 meter instrumentation cable)

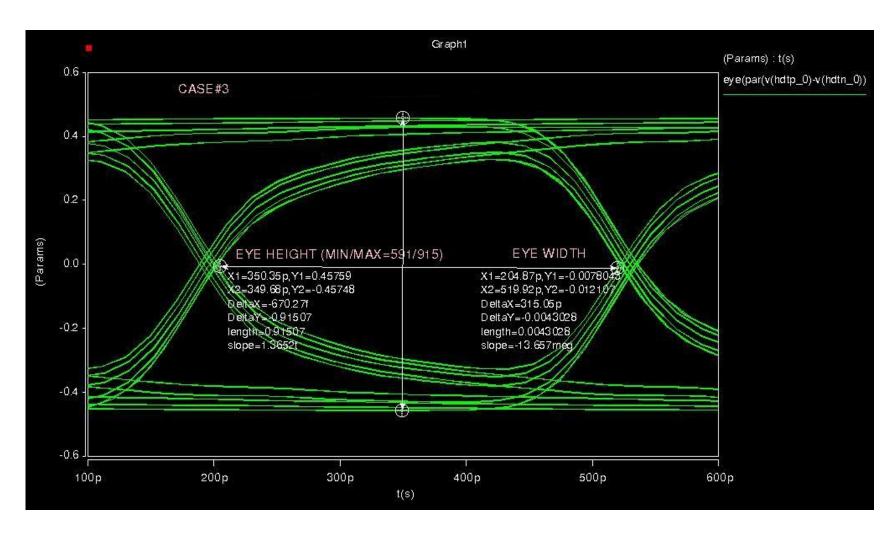

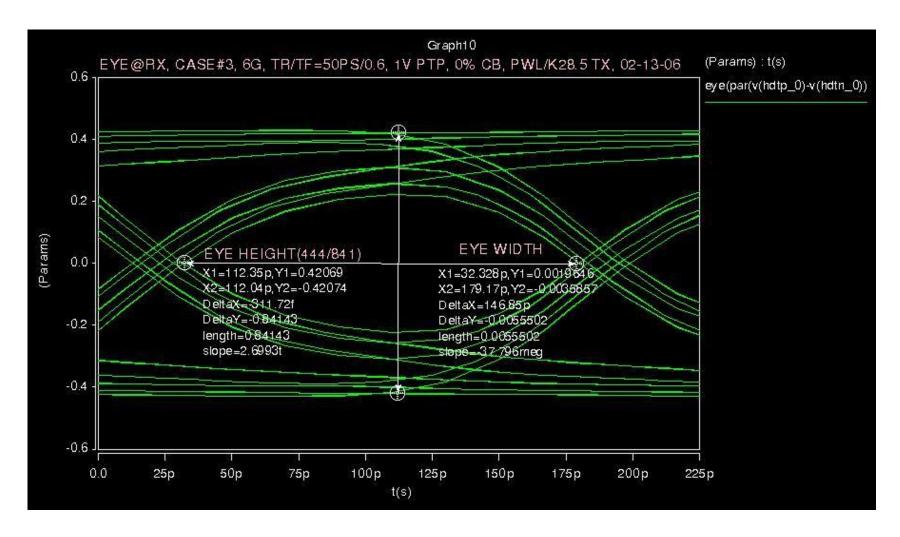

- Case #3: 2 meter miniSAS (includes fixturing losses)

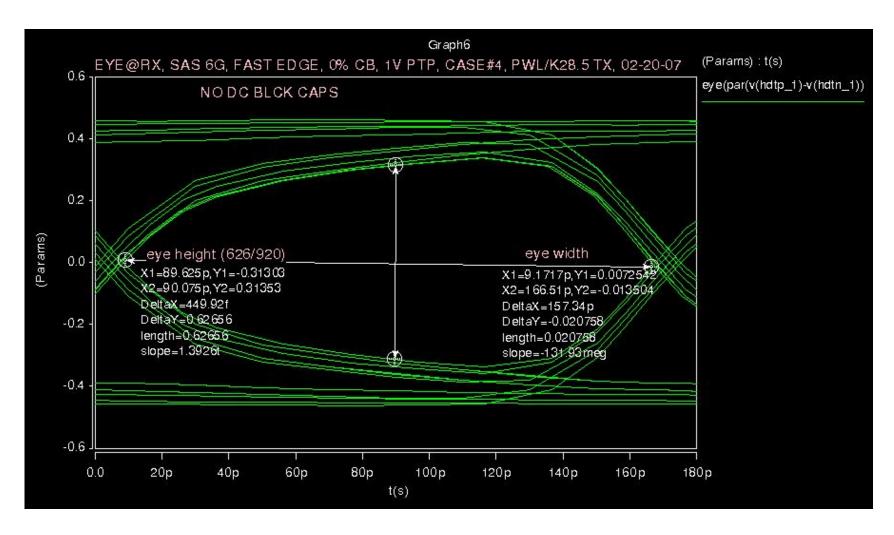

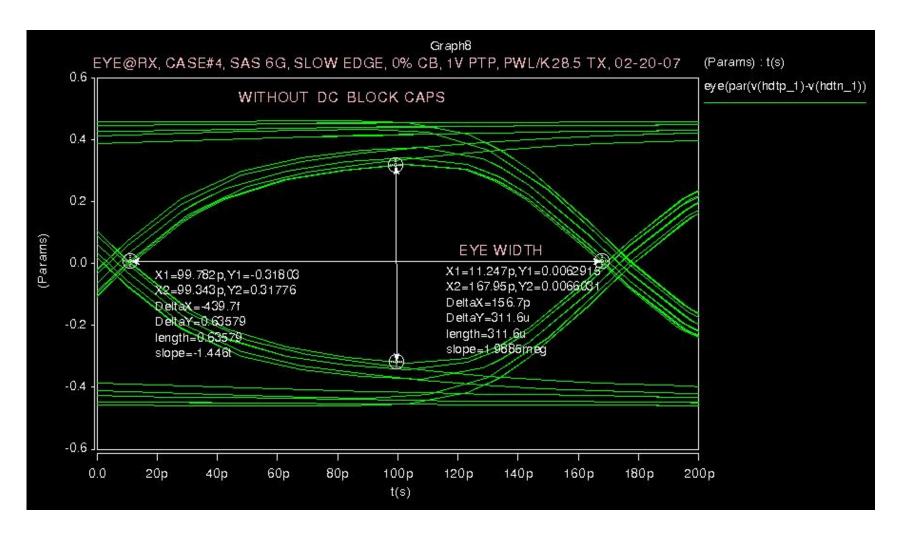

- Case#4: Mated miniSAS interface (slightly longer trace, same SMA launch and cable as #2)

- Characterize each and simulate eye diagrams to compare effects of fixtures at 3 and 6Gbps. Use 1000mV K28.5 transmitter model with fast and slow edge rates.

# Zero-Length Fixture Insertion Loss

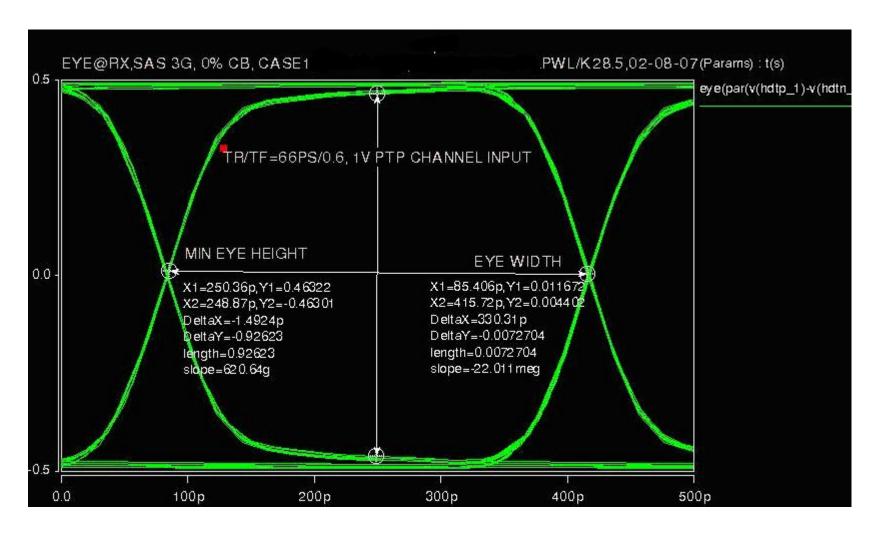

# Case #1, 3Gbps, Tr: 66ps

Eye Height: 926mV

# Case #1, 3Gbps, Tr: 100ps

Eye Height: 923mV

# Case #2, 3Gbps, Tr: 66ps

Eye Height: 794mV

# Case #2, 3Gbps, Tr: 100ps

Eye Height: 788mV

# Case #3, 3Gbps, Tr: 66ps

Eye Height: 591mV

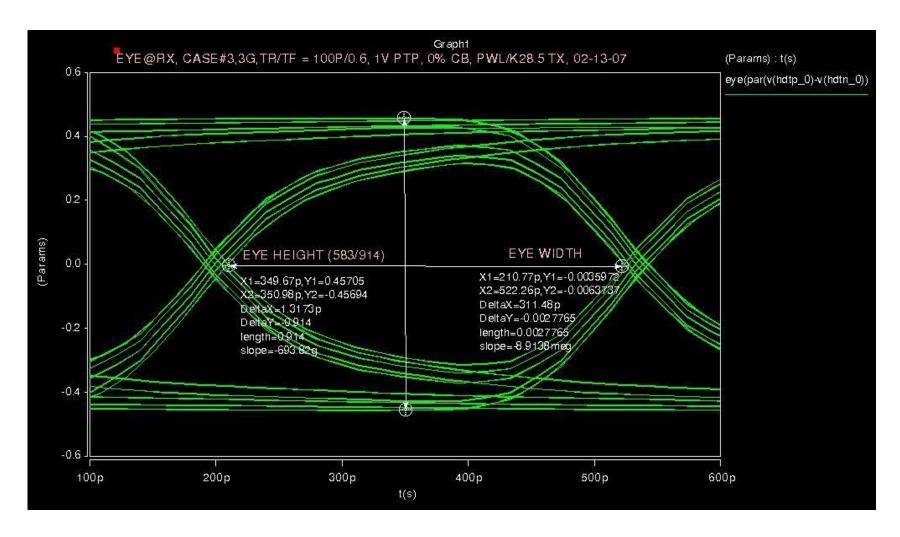

# Case #3, 3Gbps, Tr: 100ps

Eye Height: 583mV

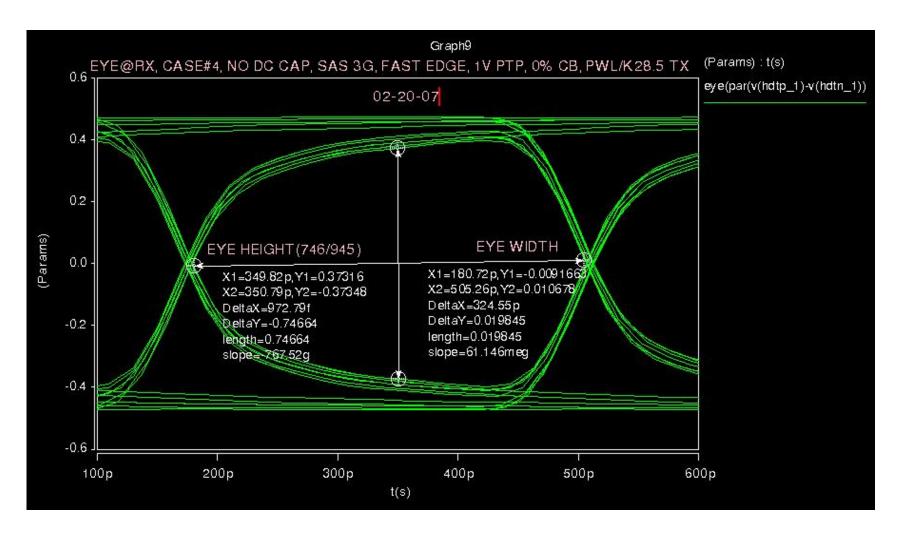

# Case #4, 3Gbps, Tr: 66ps

Eye Height: 746mV

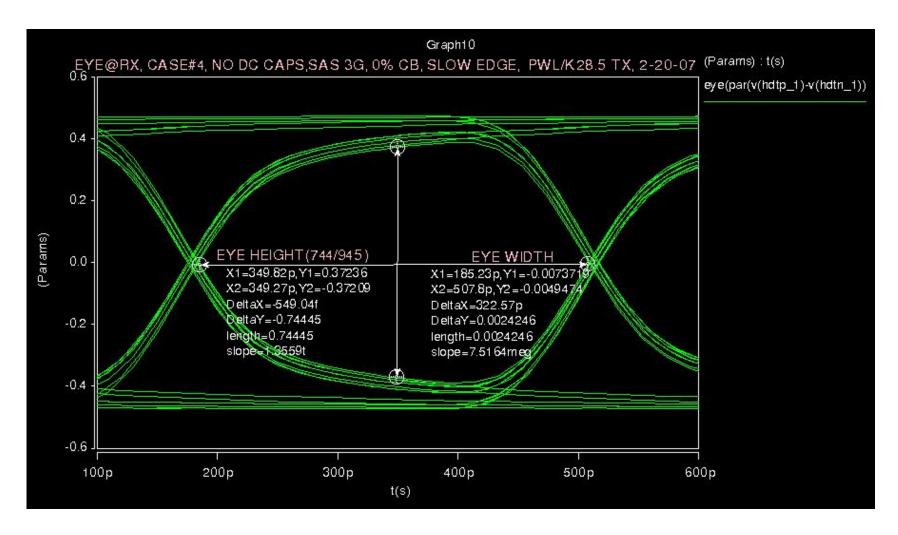

# Case #4, 3Gbps, Tr: 100ps

Eye Height: 744mV

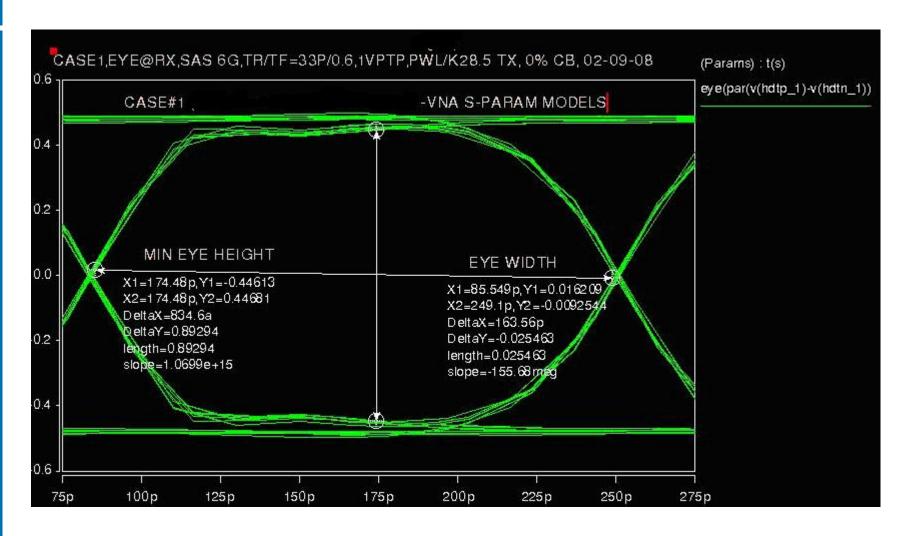

# Case #1, 6Gbps, Tr: 33ps

Eye Height: 893mV

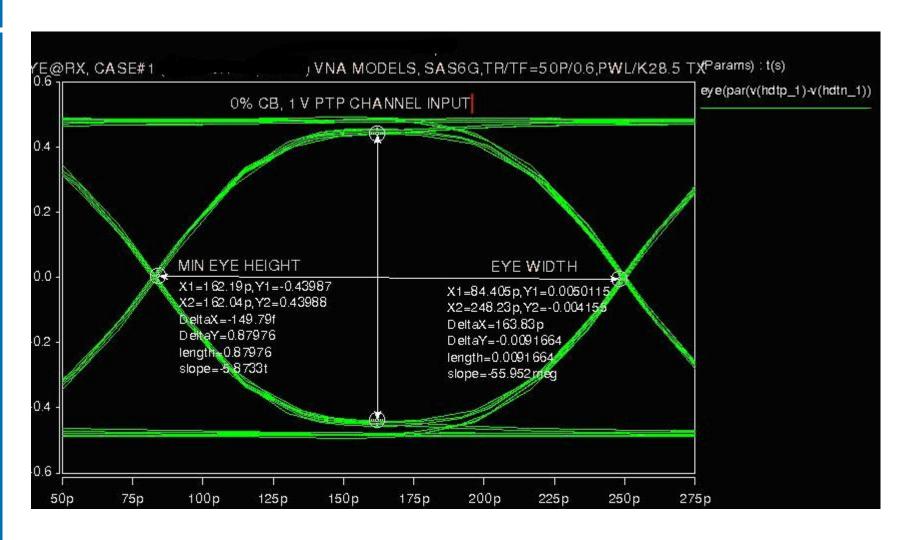

### Case #1, 6Gbps, Tr: 50ps

Eye Height: 880mV

# Case #2, 6Gbps, Tr: 33ps

Eye Height: 692mV

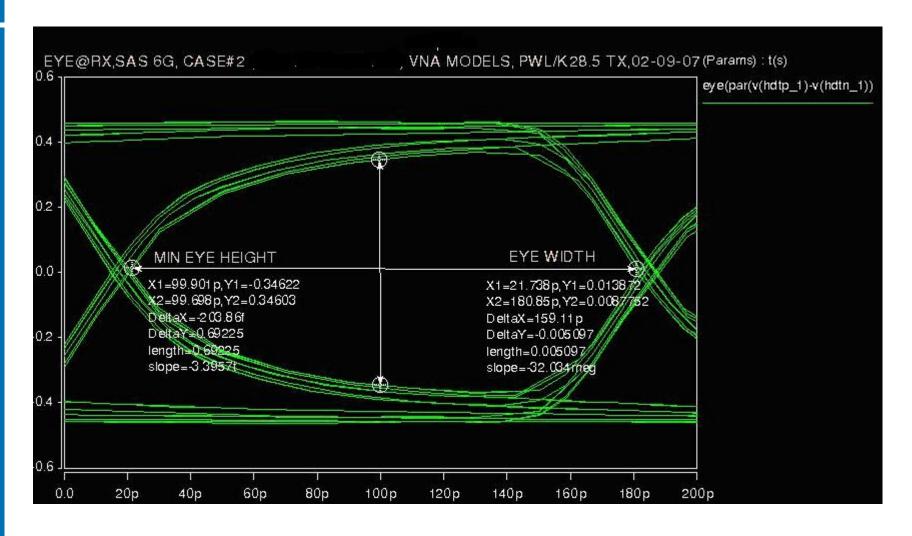

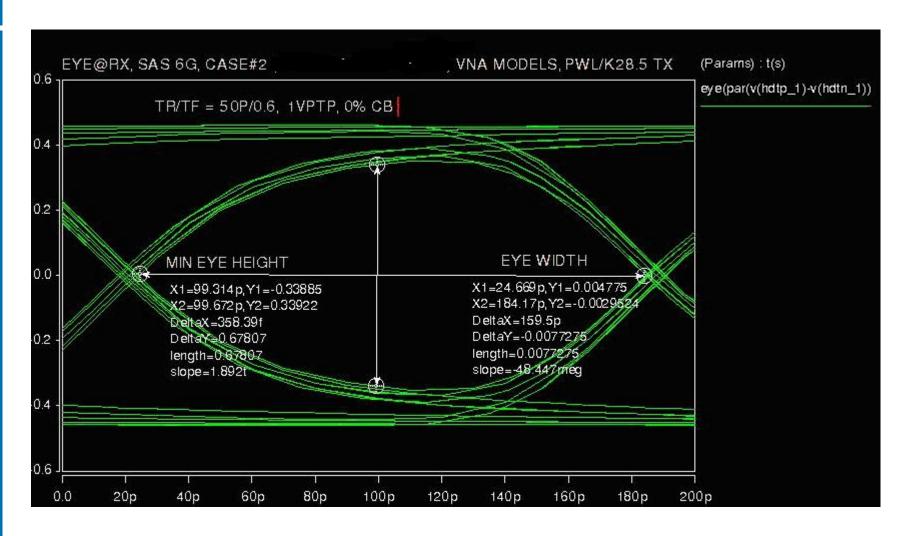

# Case #2, 6Gbps, Tr: 50ps

Eye Height: 678mV

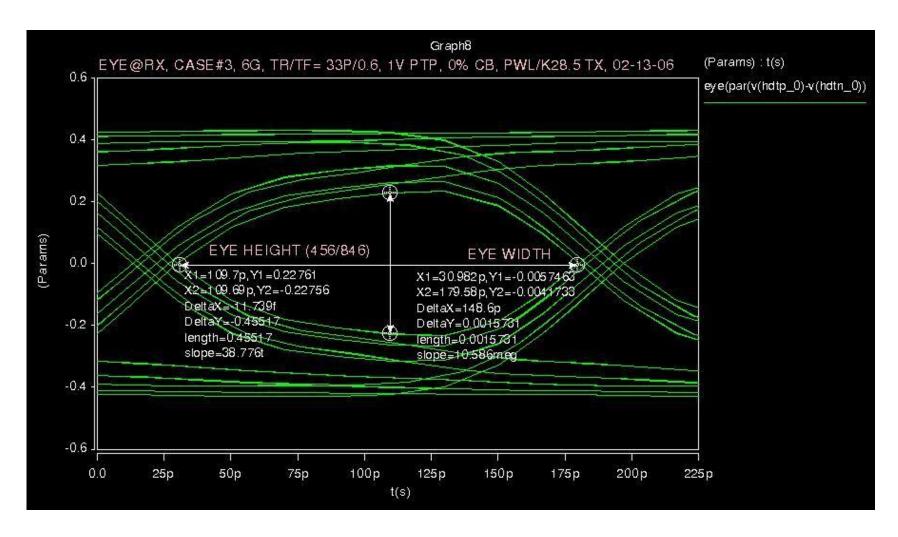

# Case #3, 6Gbps, Tr: 33ps

Eye Height: 456mV

# Case #3, 6Gbps, Tr: 50ps

Eye Height: 444mV

# Case #4, 6Gbps, Tr: 33ps

Eye Height: 626mV

### Case #4, 6Gbps, Tr: 50ps

Eye Height: 636mV

# Simulation Summary

|                | Case 1 | Case 2 | Case 3 | Case 3 |

|----------------|--------|--------|--------|--------|

| 3Gbp<br>(Fast) | 926mV  | 794mV  | 591mV  | 746mV  |

| 3Gbp<br>(Slow  | 923mV  | 788mV  | 583mV  | 744mV  |

| 6Gbp<br>(Fast) | 893mV  | 692mV  | 456mV  | 636mV  |

| 6Gbp<br>(Slow  | 880mV  | 678mV  | 444mV  | 626mV  |

#### No pre-emphasis used

#### Fixture Return Loss

- Clearly the insertion loss is a major factor in the waveform degradation. The return loss may also be a factor.

- Cases 1 and 2 may be constructed to instrumentation quality standards and minimize reflected power. How do they compare to the 3<sup>rd</sup> case?