#### Spread Spectrum Clocking Considerations T10/06-192r0

April 6, 2006

ADS

Never stop thinking

## Spread Spectrum Clock Considerations

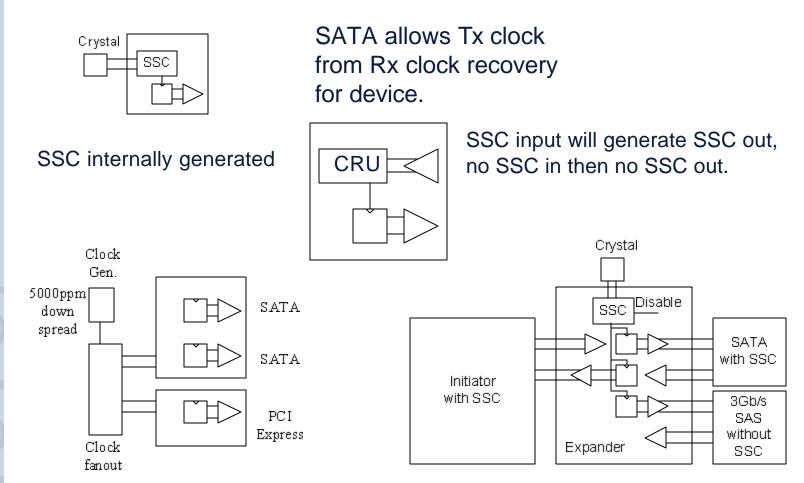

Distributed system clock

Expander with common clock.

ey Newman

**6-192r0 6, 2006** 2

# Spread Spectrum Clock Considerations

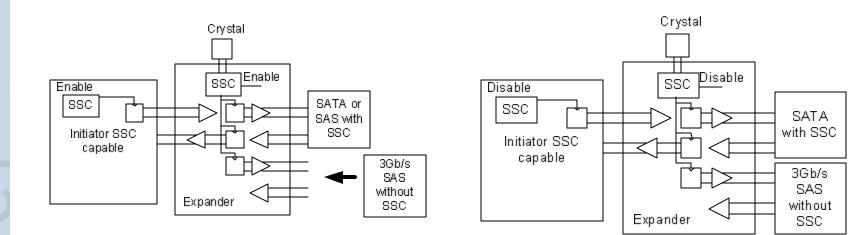

All or nothing issue: If an expander expects to use a common clock with SSC enabled or disabled and legacy SAS can not tolerate SSC then entire domain must disable SSC when a legacy device is detected.

Expander with common clock. All or none for SSC Tx. How to enable/disable?

ey Newman

**6-192r0 6, 2006** 3

## Spread Spectrum Clock Considerations

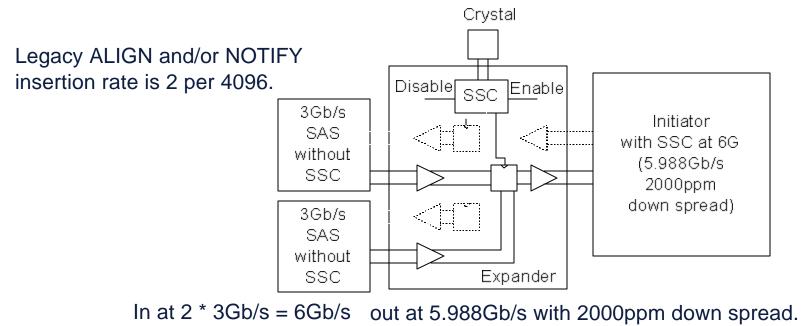

Interleaving issue: If 6Gb/s is down spread.

The number of ALIGN primitives in the legacy SAS does not allow enough elasticity buffer management.

Buffer the difference?

y Newman

**6-192r0** 6, 2006 4

## nfineon

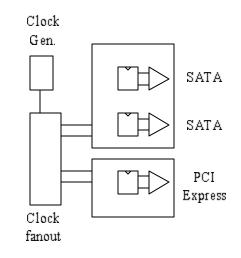

#### Clock Generator is common between SATA & PCI Express. Spread Spectrum Clocking is 5000ppm down spread.

y Newman

**6-192r0 6, 2006** 5

أht Intel® ICH7 and System Clock Domains Figure 4-1. Desktop Only Conceptual System Clock Diagram PCI 33MHz Clocks (33 MHz) 14.31818MHz Clock Gen. 48.000MHz 14.31818MHz 48.000MHz Intel<sup>®</sup> 100MHz ICH7 Diff.Pair 1 to 6 Differential PCI Express SATA100MHzDiff, Pair 100MHz ClockFan DMI 100 MHzDiff. Pair Diff. Pairs OutDevice 50MHz LAN Connect 12 288MHz AC '97 Codec(s) 24MHz HighDefinitionAudioCodec(s 32kHz SUSCLK#(32 KHZ) XTAL

ftp://download.intel.com/design/chipsets/datashts/30701302.pdf Page 94

SSC on system clock. SATA will likely have 5000ppm down spread at 6Gb/s due to this architecture and feedback from SATA phy call April 5th