## LSI LOGIC '

## Title: Overview of Signaling and Equalization Methods Considered in OIF and IEEE 802.3 ap for 6G and 10 Gbps

Sources: Joe Caroselli and Mike Jenkins

#### LSI Logic

```

Date: May 26, 2005

```

#### Abstract:

The presentation gives an overview and comparison of signaling methods and equalization techniques considered for backplane transceivers at 6 and 10 Gbps in other standards bodies. In particular, NRZ, PAM-4 Duobinary, and PR4 are the signaling schemes considered and linear and decision feedback equalization are discussed.

# Introduction

- Many signaling techniques have been examined

- NRZ

- PAM-4

- Duobinary

- PR4

- Several equalization techniques have been considered

- FIR linear filter on TX or RX

- Continuous time linear equalizer in Rx

- Decision Feedback Equalizer in Rx

# Introduction

- Simulation Model Overview

- Linear Equalizer versus Decision Feedback Equalization (DFE)

- NRZ vs. PAM-4

- NRZ, Duobinary, and PR4

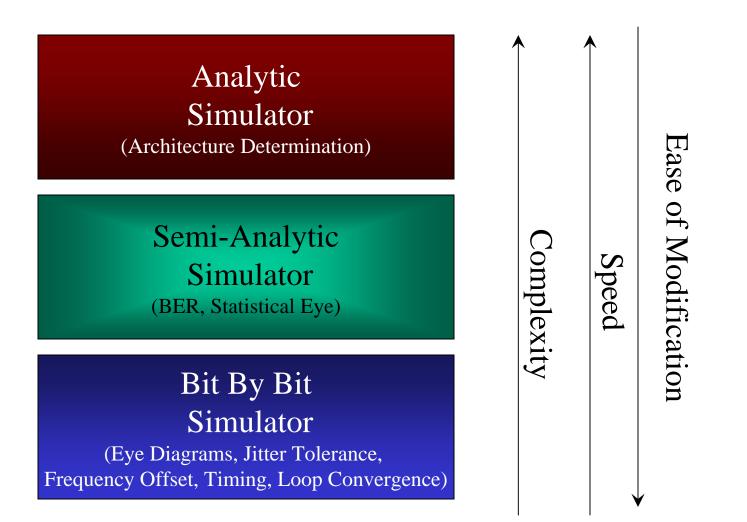

# Simulator Overview

## Three System Modeling Approach

# Analytic Model

- Includes

- Inter-symbol Interference

- Tx Jitter

- Electronics (White) Noise

- Crosstalk

- Does Not Include

- Receiver Sensitivity

- Duty Cycle Distortion

- Other Sources of DJ

## **Overview of Simulations**

- Equalization architectures with a linear FIR feedforward (FF) filter in the TX, and a decision feedback (FB) equalizer in the Rx are compared.

- The number of taps in the feedforward and feedback equalizers are varied.

- The effect of one worst-case near-end crosstalk aggressor is considered.

- A simple RC model with pole at 0.75\*baud rate is used for the transmitter.

- Mellitz capacitor-like package model included on both transmitter and receiver.

## Parameters Used

- Only DJ is from ISI

- No DCD, PJ included

- 0.010UI  $\sigma$  RJ added, unless otherwise noted

- Not more than 13.4ps peak-to-peak RJ at 8.5Gbps data rate with probability 1-10<sup>-12</sup>

- Not more than 15.6ps peak-to-peak RJ max at 8.5Gbps data rate with probability 1-10<sup>-15</sup>

- Signal-To-Electronics Noise Ratio 45dB, unless otherwise noted

- Crosstalk added as noted

- Ideal receiver sensitivity assumed

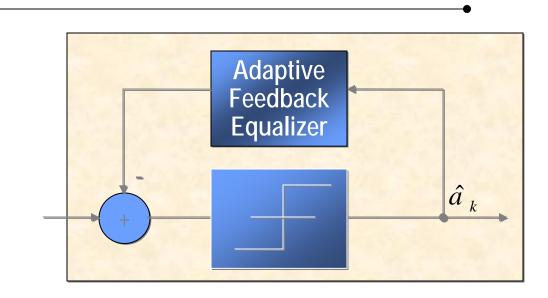

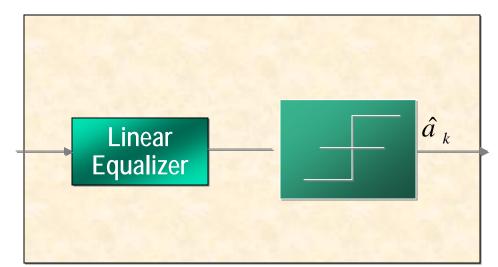

### Decision Feedback Equalization versus Linear Feedforward Equalization

**DFE Receiver**

Receiver with Linear Equalization

# Ideal DFE versus Ideal Linear Equalization

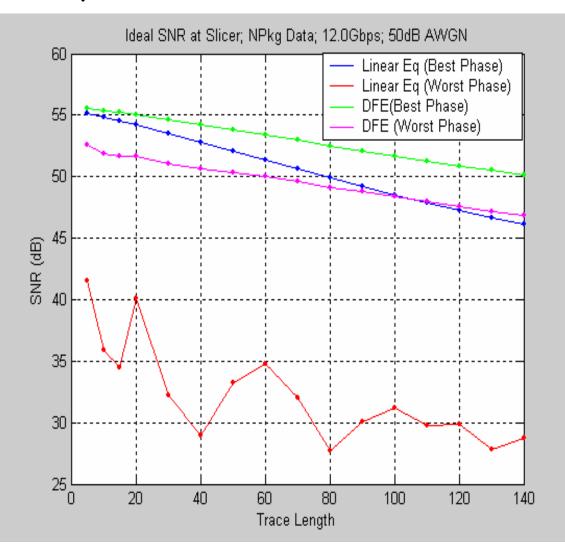

Best and Worst Case Phases Versus Distance; No Jitter or XT

•DFE has an advantage over linear equalizer at the ideal sampling phase because it results in less noise enhancement.

•DFE is less affected by choice of sampling phase and thus more resistant to jitter.

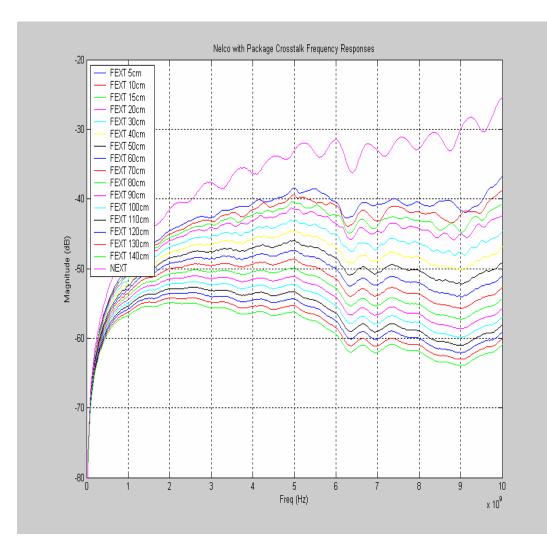

#### Crosstalk Near-End and Far-End Crosstalk Frequency Responses

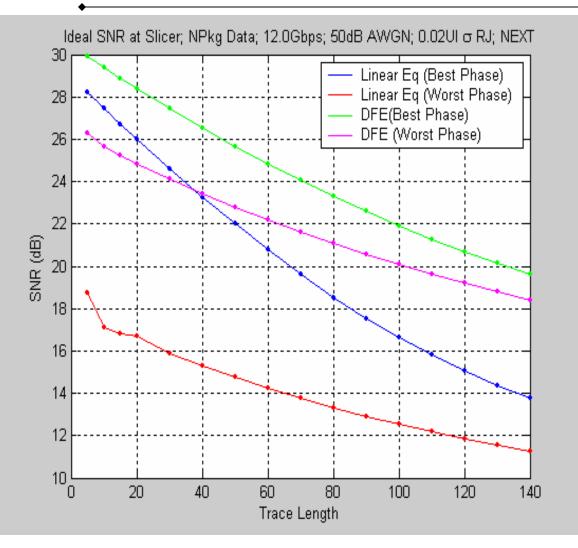

Ideal DFE versus Ideal Linear Equalization Best and Worst Case Phases Versus Distance with Jitter and NEXT

•The benefit of DFE is shown to grow with the amount of high frequency noise and the amount of high frequency boost required to compensate for the channel's attenuation.

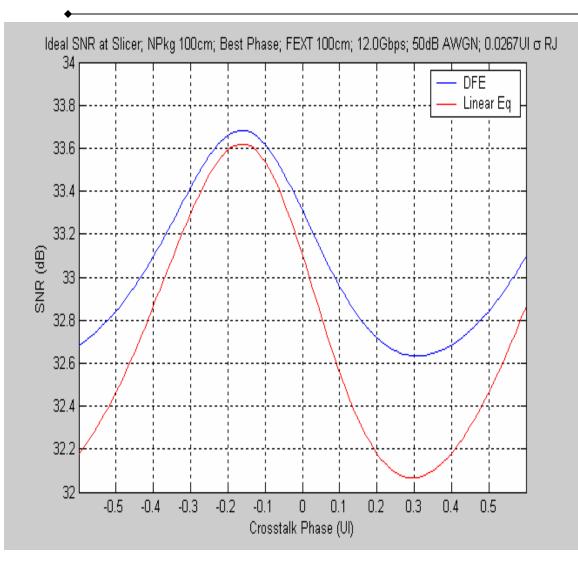

#### Far-End Crosstalk Effect of Crosstalk Phase

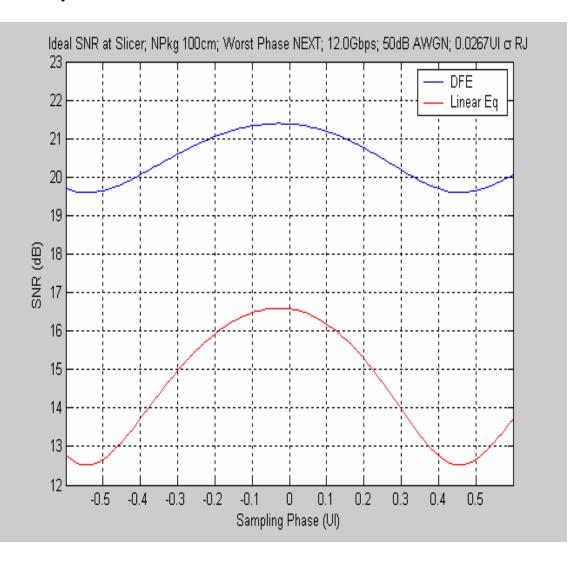

#### Near-End Crosstalk Effect of Worst Phase NEXT

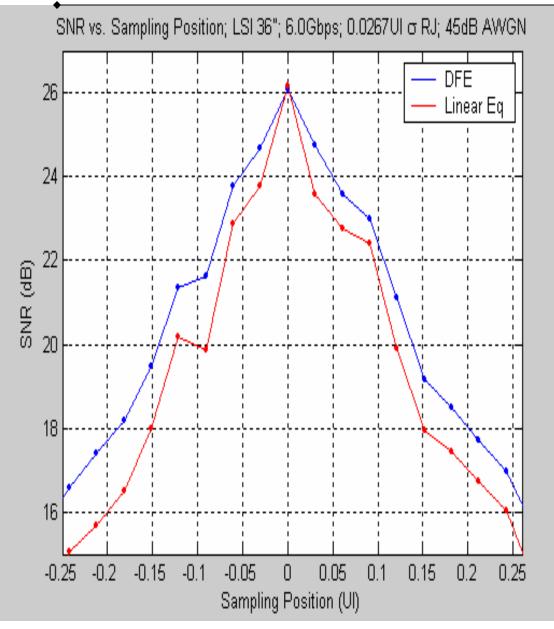

# SNR at Slicer vs. Sampling Position

LSI 36" Trace, 6.0 Gbps; 0.026UI Random Jitter

•Even without crosstalk, the benefit of DFE can be seen as the sampling position moves away from the center of the eye. This results in improved jitter tolerance.

# NRZ vs. PAM-4

# Introduction

- NRZ is standard 2–level signaling used in most backplane transceivers today.

- PAM-4 is four level signaling at half the bit rate with each level corresponding determined by two consecutive bits.

- NRZ can perform better than PAM-4 even when the channel loss between the Nyquist frequency of PAM-4 and that of NRZ is greater than 9.5dB.

- NRZ and PAM-4 with a linear FIR feedforward (FF) filter and a decision feedback (FB) equalizer are compared for such a channel.

- The number of taps in the feedforward and feedback equalizers are varied.

- The effect of near-end crosstalk is observed.

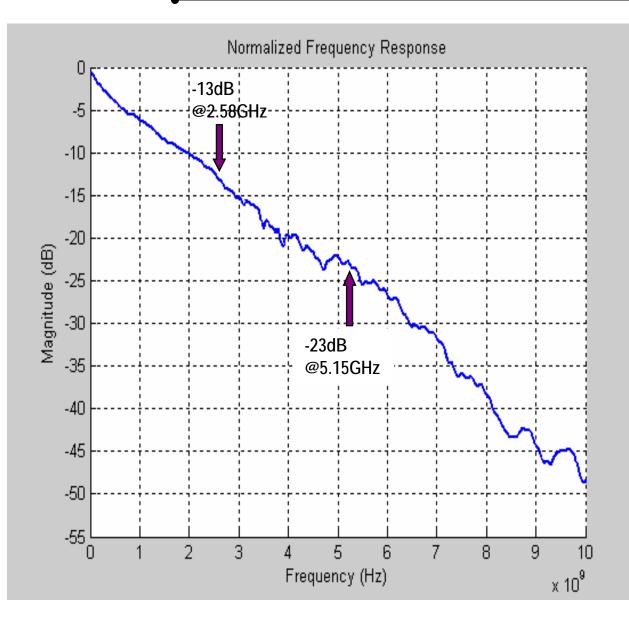

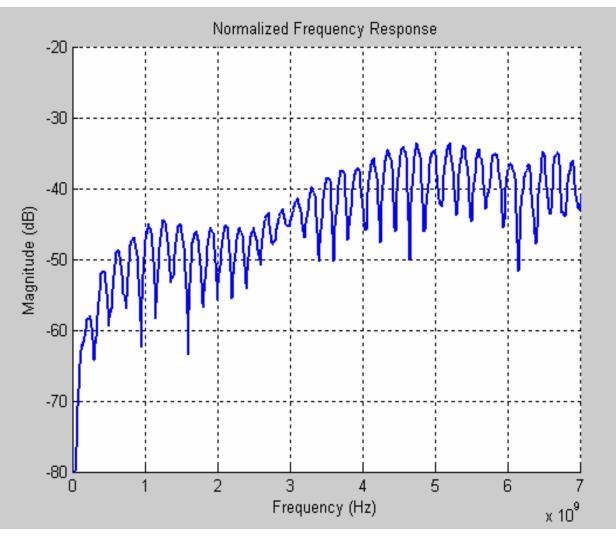

## Frequency Response Actual Channel (from Steve Anderson, Xilinx)

•Difference between response at 5.15GHz (Nyquist frequency of NRZ) and 2.58GHz (Nyquist frequency of PAM-4) is about 10dB.

•PAM-4 is often thought to perform better if the difference is greater >9.5dB.<sup>1</sup> This figure comes from the fact that an ideal PAM-4 signal has three eyes each of which have roughly 1/3 the vertical opening of an ideal NRZ eye.

<sup>1</sup> Howard Johnson, "Multi-Level Signaling," DesignCon 2000.

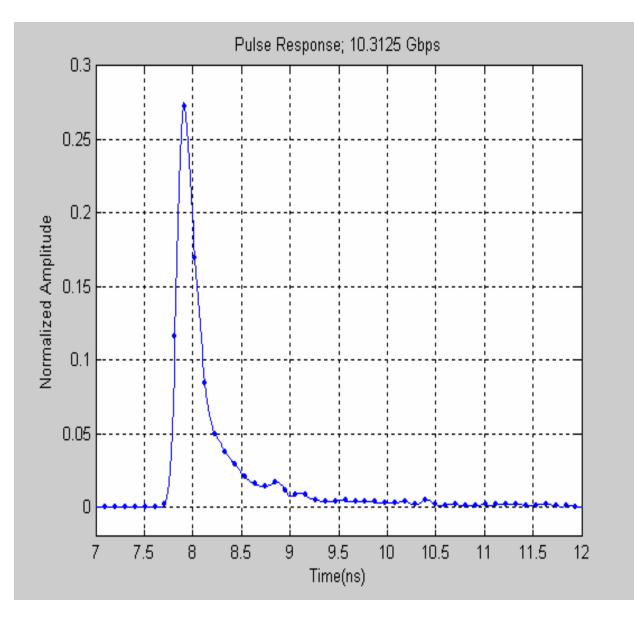

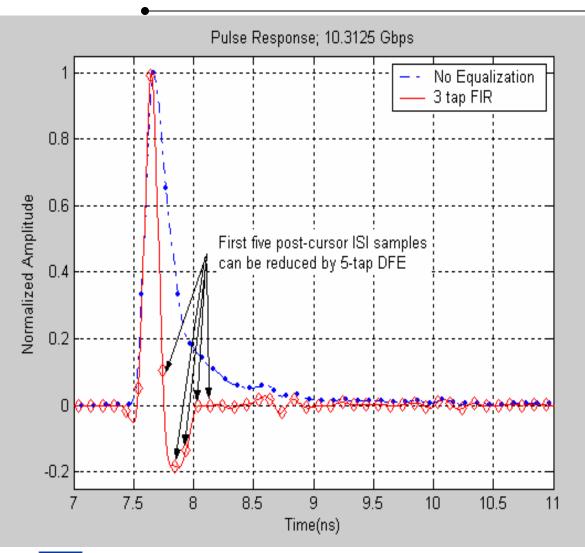

### Pulse Response Based on Channel similar to IEEE 802.3ap Channel Model

•Pulse response generated assuming single pole TX lowpass filter with corner at <sup>3</sup>/<sub>4</sub> \* baud rate.

•Dots are separated by one UI and therefore represent potential ISI.

•Only one significant point of pre-cursor ISI.

•Has long slowly decaying tail with many points of post-cursor ISI. This would require >15 DFE taps to completely address.

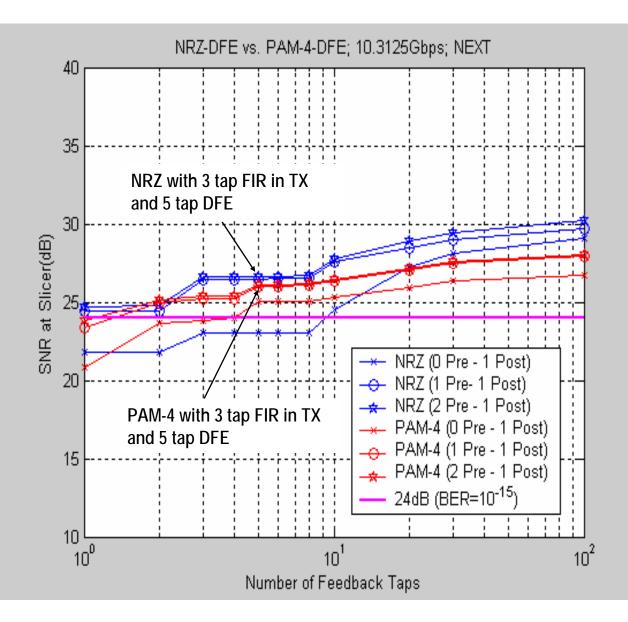

# Description of Results

- SNR at optimal sampling point is shown. No measurement of horizontal eye opening is presented.

- x-axis shows number of feedback taps used

- Each line represents a different number of feedforward (FF) equalizer taps used in the TX

- Each color represents a different signaling scheme.

- Crosstalk is assumed to occur at the same frequency as the signal. The worst case crosstalk phase at the ideal sampling point is selected.

- All tap values are ideal.

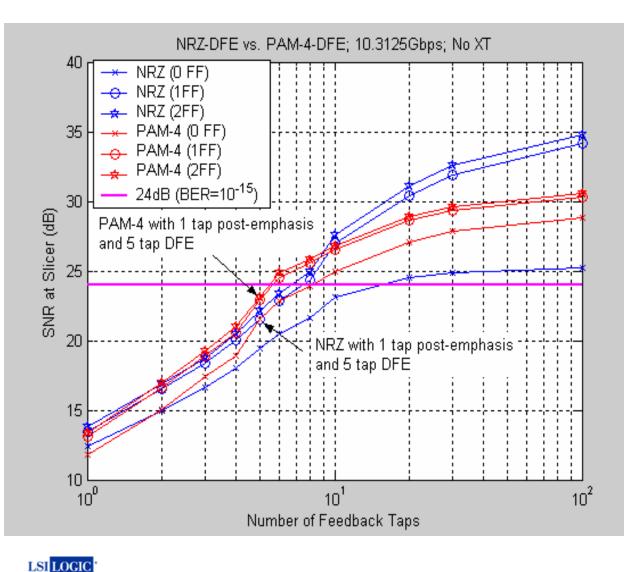

### NRZ vs PAM-4 10.3125Gbps; No Crosstalk

•Transmit equalization is FIR with varying number of taps to address pre-cursor ISI.

$$\frac{D^{k} - \sum_{n=0}^{n=k-1} \alpha_{n} D^{(k-1)-n}}{1 + \sum_{n=0}^{k-1} abs(\alpha_{n})}$$

•With one tap post-emphasis (D-α) and 5 feedback taps, neither PAM-4 nor NRZ provides enough SNR to function. However,PAM4 has about 1.5dB more SNR.

•To get BER <10<sup>-15</sup> with one tap post-emphasis, PAM-4 requires 6 feedback taps while NRZ requires 8.

•As number of DFE taps increases, performance of NRZ relative to PAM4 increases.

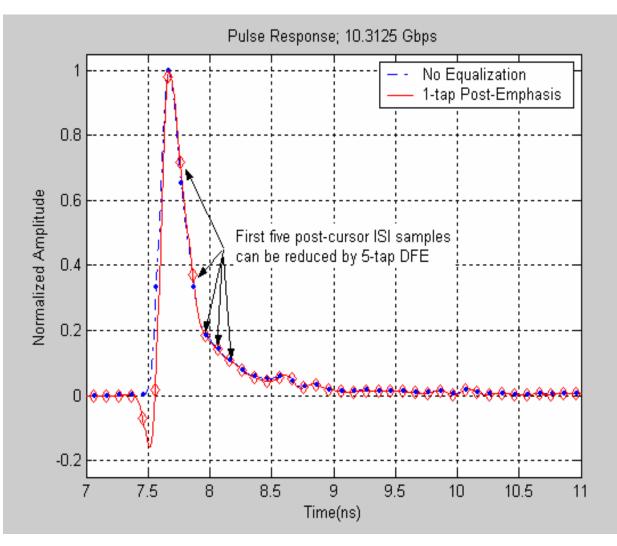

## Pulse Response at 10.3125Gbps One Tap Post-Emphasis

- •Transmit equalization is two tap FIR to address pre-cursor ISI (one tap post-emphasis).

- •Precursor ISI is greatly reduced.

- •First five post-cursor ISI samples can be reduced by a 5tap DFE.

- •A long slowly decaying tail of post-cursor ISI still remains.

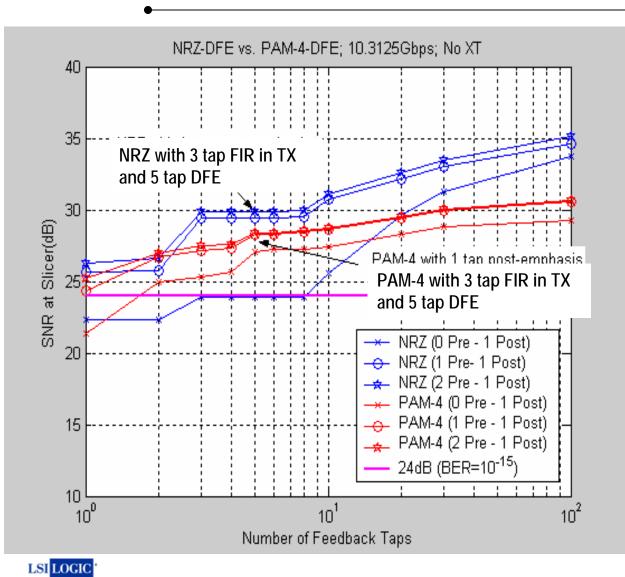

#### NRZ vs PAM-4

10.3125Gbps; No Crosstalk; With One Tap PostCursor FF Equalization

•Transmit equalization is a FIR with one tap to address postcursor ISI and varying number of taps to address pre-cursor ISI.

•With one tap post-emphasis and one tap pre-emphasis

$(-\beta D^2 + D - \alpha)$

and 5 feedback taps, both PAM-4 and NRZ provide enough SNR to function. However, NRZ has about 1dB more SNR than PAM-4.

•As the number of feedback taps increases, advantage of NRZ over PAM4 increases.

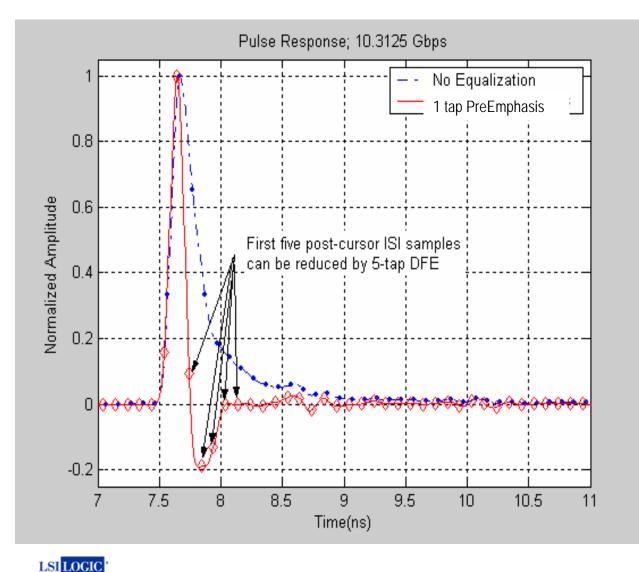

## Pulse Response at 10.3125Gbps One Tap Pre-Emphasis

- •Transmit equalization is two tap FIR to address post-cursor ISI (one tap pre-emphasis).

- •Post-cursor ISI is greatly reduced so that only three significant post-cursor ISI points remain.

- •One tap of pre-emphasis can almost completely remove long tail that would require almost 15 taps of DFE.

- •Pre-cursor ISI is reduced but still significant.

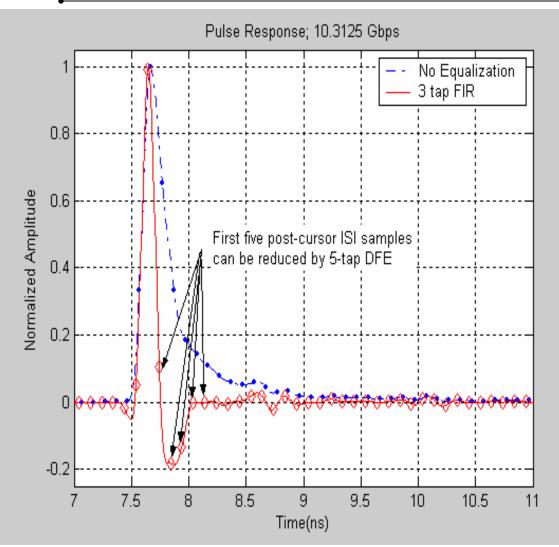

### Pulse Response at 10.3125Gbps Three Tap FIR (One Tap Pre-Emphasis and One Tap Post-Emphasis)

•Transmit equalization is three tap FIR with one tap to address pre-cursor ISI and one tap to address post-cursor ISI. (One tap post-emphasis and one tap pre-emphasis.)

•Pre-cursor ISI is now also significantly reduced.

LSI LOCIC

#### Near-End Crosstalk Frequency Responses From Xilinx

- •One channel of NEXT will be added to the simulations.

- •Crosstalk is assumed to occur at the same frequency as the signal.

- •The worst case crosstalk phase at the ideal sampling point is selected.

#### NRZ vs PAM-4

10.3125Gbps; NEXT; With One Tap PostCursor FF Equalization

•With NEXT and three tap FIR, NRZ meets SNR goal with one DFE tap and PAM-4 requires two.

•With NEXT, performance of three tap FIR and 5 DFE taps decreases about 2.5dB.

•NRZ advantage over PAM-4 has decreased to about 0.5dB with 5 tap DFE.

# Conclusion NRZ vs. PAM-4

- Although channel has greater than 9.5dB loss between Nyquist frequencies of PAM-4 and NRZ, NRZ can perform better depending on the detection scheme.

- Performance of NRZ improves relative to PAM-4 as the number of DFE taps increase.

- A three tap FIR with one tap dedicated to post-emphasis and one tap devoted to pre-emphasis is recommended. This can greatly reduce precursor ISI and mostly remove a long slowly decaying tail on the pulse response. A few points of significant post-cursor ISI remain and can be removed with a few taps of DFE.

- With pre-emphasis tap, number and weight of feedback taps is reduced resulting in improved error propagation.

# NRZ, Duobinary, and PR4 Overview

# Introduction

- Overview of signaling schemes

- NRZ, Duobinary, and PR4

- Presentation of results

# NRZ Signaling Trying to Removing All ISI Through Equalization

- Our primary equalization goal has been to eliminate intersymbol interference (ISI).

- A combination of a TX FIR filter and a DFE in the Rx are used to mitigate the ISI.

- The goal of removing ISI is to make detection possible with a reasonable complexity.

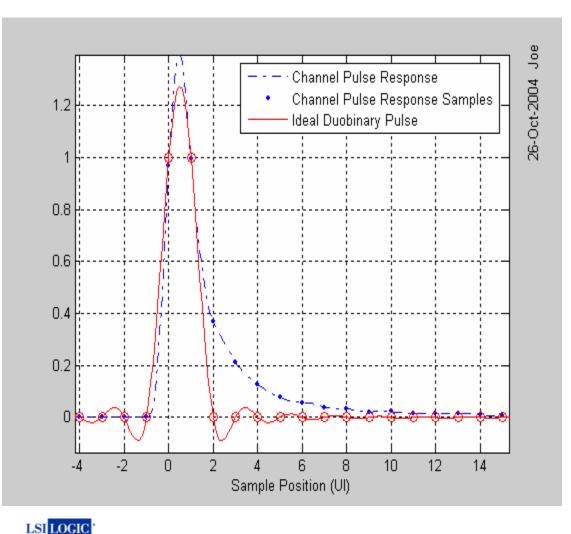

# **Duobinary** Ideal versus Channel Pulse Response

- 1+D Channel

- Samples at

- time 0 and 1 are 1

- 0 everywhere else.

- Appears to be a reasonable fit for channels at this data rate.

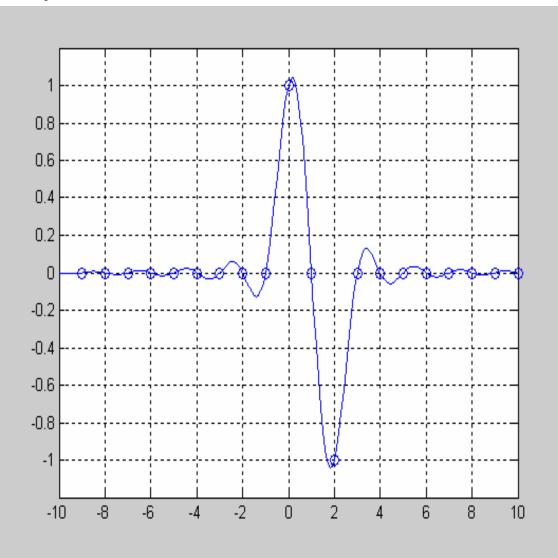

# Partial Response – Class IV Pulse Response

• Does not resemble our channel pulse response.

LSI LOGIC

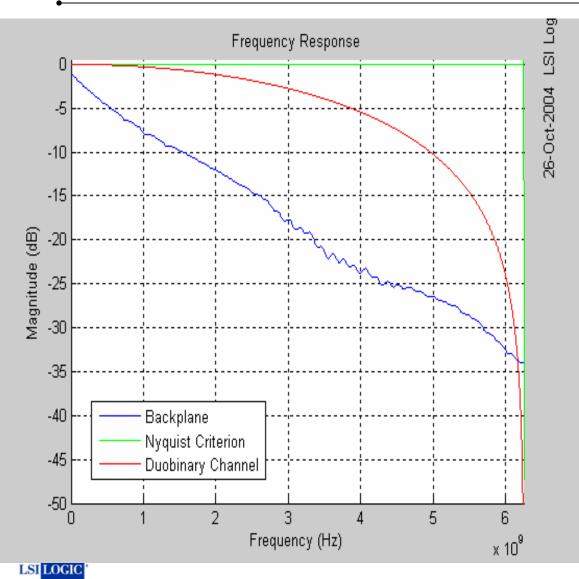

# Frequency Response Comparison NRZ and Duobinary

- Ideal NRZ equalization target is flat spectrum.

- NRZ requires a lot of high frequency boost.

- Duobinary's 1+D equalization target has a null at the Nyquist frequency. It is a better match to the channel at high frequencies and consequently requires less high frequency boost.

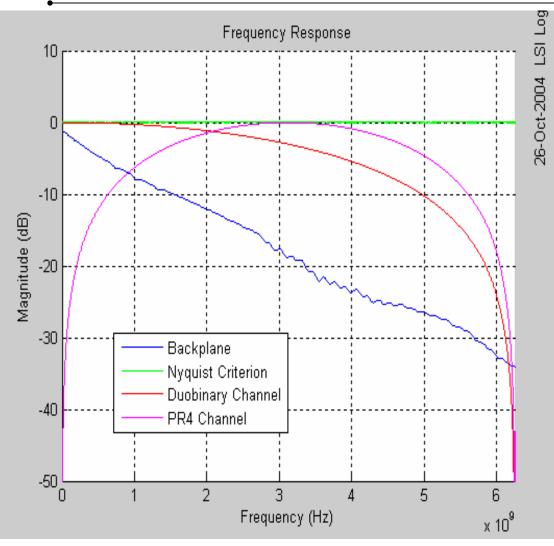

# Frequency Response Comparison NRZ, Duobinary, and PR4

- Has nulls at both DC and Nyquist

- Null at DC may match DCnull in AC coupled systems, but PR-4's DC null is much deeper.

- Equalizing to PR4 results in throwing away the signal in the low frequency range where the SNR is strongest.

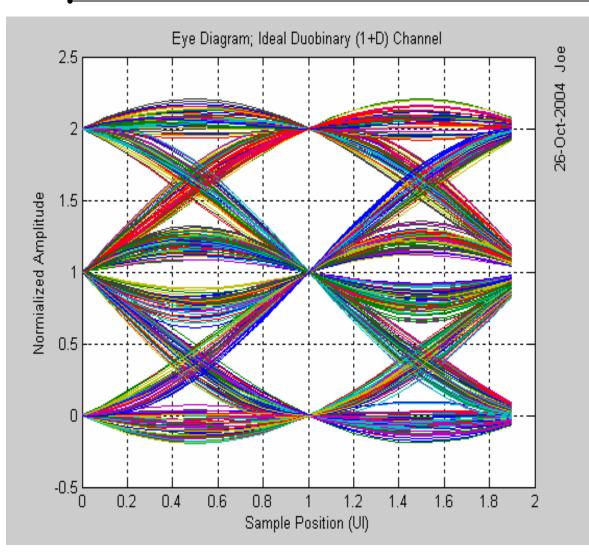

## **Duobinary** Ideal Eye Diagram

- No transitions from highest to lowest signal levels in adjacent bits.

- Notice that slicer value that results in highest jitter tolerance is not the slicer level that results in best noise tolerance.

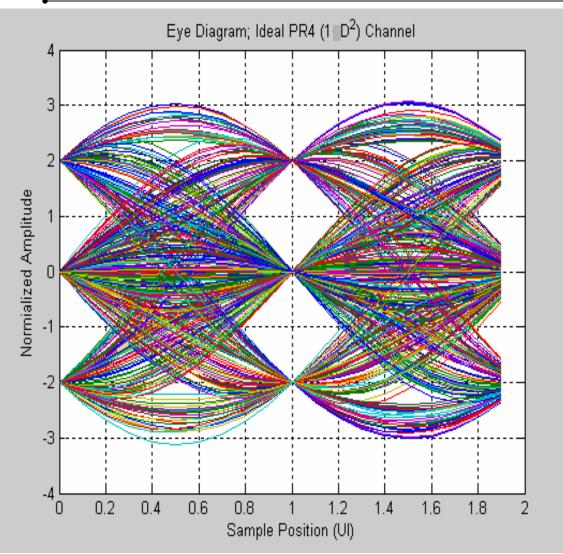

# PR4 Eye Diagram

LSI LOGIC

- Horizontal eye opening in ideal eye diagram is reduced compared to 1+D target.

- Any signal level can transition to any other signal level in adjacent bit.

- Even in ideal case, without MLSD, eye exhibits very little tolerance to jitter.

# Summary of Results

# SNR Comparison

Intel Backplanes

| вр           | NRZ<br>3FF+5DFE | DB<br>3FF+3DFE | DB<br>3FF+5DFE | DB<br>4FF+3DFE | DB<br>4FF+5DFE | PR4<br>3FF+3DFE | PR4<br>3FF+5DFE | PR4<br>5FF+3DFE | PR4<br>5FF+5DFE |

|--------------|-----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|

| Intel<br>B1  | 25.75           | 23.7428        | 24.7189        | 23.8904        | 24.7194        | 10.02           | 10.5355         | 21.9916         | 22.148          |

| Intel<br>B12 | 25.4387         | 20.6647        | 24.2936        | 24.0673        | 25.5312        | 11.8722         | 12.9072         | 22.9701         | 23.5763         |

| Intel<br>B20 | 24.421          | 17.9337        | 21.4678        | 24.1036        | 24.7867        | 12.5534         | 13.6077         | 22.137          | 22.9709         |

| Intel<br>M1  | 24.2043         | 21.3843        | 21.8428        | 21.3882        | 22.1214        | 13.6615         | 14.3548         | 19.2269         | 20.565          |

| Intel<br>M20 | 24.2586         | 18.8378        | 20.1773        | 21.8866        | 22.3897        | 16.7028         | 17.1796         | 21.0436         | 21.0448         |

| Intel<br>T1  | 21.862          | 19.6715        | 20.0462        | 19.685         | 20.1262        | 11.684          | 11.8187         | 17.7951         | 19.4143         |

| Intel<br>T12 | 21.3521         | 17.8295        | 20.2168        | 18.696         | 20.4783        | 13.8084         | 15.0696         | 18.1711         | 18.9188         |

| Intel<br>T20 | 20.4595         | 16.3257        | 19.0451        | 18.4427        | 19.7304        | 14.0649         | 15.2461         | 17.3062         | 18.2698         |

### SNR Comparison

Tyco Backplanes

| BP        | NRZ<br>3FF+5DFE | DB<br>3FF+3DFE | DB<br>3FF+5DFE | DB<br>4FF+3DFE | DB<br>4FF+5DFE | PR4<br>3FF+3DFE | PR4<br>3FF+5DFE | PR4<br>5FF+3DFE | PR4<br>5FF+5DFE |

|-----------|-----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|

| Tyco<br>1 | 26.4184         | 15.5579        | 18.0878        | 25.3081        | 25.3752        | 13.7218         | 15.3615         | 23.1624         | 23.6852         |

| Tyco<br>2 | 26.7208         | 15.4417        | 17.8542        | 15.4474        | 17.8549        | 13.6503         | 15.4245         | 13.6559         | 15.4302         |

| Tyco<br>3 | 24.7924         | 14.7412        | 17.0261        | 24.4904        | 24.6559        | 13.0619         | 14.8896         | 22.4596         | 23.1564         |

| Tyco<br>4 | 27.3838         | 16.7213        | 19.9583        | 25.8848        | 26.1496        | 14.6765         | 16.383          | 23.8066         | 24.8202         |

| Tyco<br>5 | 28.8032         | 20.5003        | 23.6176        | 27.3431        | 27.896         | 15.9264         | 17.4989         | 25.2065         | 26.7141         |

| Tyco<br>6 | 25.4634         | 19.9357        | 22.3319        | 23.3344        | 24.3991        | 15.6349         | 17.0529         | 21.6006         | 23.0806         |

| Tyco<br>7 | 26.6822         | 23.394         | 25.8662        | 23.7112        | 26.0652        | 16.9793         | 17.5009         | 22.5142         | 24.2921         |

### SNR Comparison

#### Molex and Xilinx Backplanes

| BP           | NRZ<br>3FF+5DFE | DB<br>3FF+3DFE | DB<br>3FF+5DFE | DB<br>4FF+3DFE | DB<br>4FF+5DFE | PR4<br>3FF+3DFE | PR4<br>3FF+5DFE | PR4<br>5FF+3DFE | PR4<br>5FF+5DFE |

|--------------|-----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|

| MoL<br>ex i2 | 24.809          | 17.1815        | 18.9193        | 23.3004        | 23.8805        | 14.9248         | 16.8129         | 21.4513         | 22.3848         |

| MoL<br>ex i3 | 24.7216         | 16.4369        | 18.7943        | 23.0948        | 23.7304        | 14.0673         | 15.9244         | 21.3092         | 22.3042         |

| MoL<br>ex i4 | 24.635          | 16.8023        | 18.7352        | 23.0507        | 23.7563        | 14.504          | 16.5218         | 20.9664         | 22.278          |

| MoL<br>ex i5 | 24.9085         | 16.0529        | 18.9518        | 23.5529        | 23.9459        | 13.7286         | 15.6399         | 21.5105         | 22.4099         |

| Mole<br>x o2 | 25.224          | 17.5415        | 19.1214        | 23.9419        | 24.2682        | 15.4785         | 17.0011         | 22.3036         | 22.683          |

| Mole<br>x o3 | 25.0651         | 16.75          | 18.8106        | 23.6832        | 24.0728        | 14.586          | 16.1901         | 22.0329         | 22.4956         |

| Mole<br>x o4 | 25.1958         | 17.2071        | 18.9993        | 23.9024        | 24.2266        | 15.1239         | 16.7727         | 22.1454         | 22.6515         |

| Mole<br>x o5 | 25.2929         | 17.2958        | 19.1175        | 24.1252        | 24.3047        | 15.3704         | 16.9238         | 22.3191         | 22.6489         |

| Ande<br>rson | 23.6875         | 15.3596        | 18.3673        | 22.8244        | 22.9803        | 13.3333         | 15.2358         | 20.2191         | 21.0405         |

#### Required Number of DFE Taps To Achieve 24dB SNR Tyco Backplanes

| BP     | NRZ      | DB       | PR4      |

|--------|----------|----------|----------|

|        | 3 tap FF | 4 tap FF | 5 tap FF |

| Тусо 1 | <=1      | 3        | 6        |

| Тусо 2 | <=1      | 20       | 100      |

| Тусо3  | 3        | 3        | 10       |

| Тусо4  | <=1      | 2        | 4        |

| Тусо 5 | <=1      | <=1      | <=1      |

| Tyco 6 | 4        | 4        | 30       |

#### Required Number of DFE Taps To Achieve 24dB SNR Intel Backplanes

| BP        | NRZ      | DB       | PR4      |  |

|-----------|----------|----------|----------|--|

|           | 3 tap FF | 4 tap FF | 5 tap FF |  |

| Intel B1  | 3        | 4        | 8        |  |

| Intel B12 | 4        | 3        | 6        |  |

| Intel B20 | 4        | 3        | 8        |  |

| Intel M1  | 4        | 6        | 10       |  |

| Intel M20 | 5        | 20       | 20       |  |

| Intel T1  | 10       | 20       | 20       |  |

| Intel T12 | 100      | 100      | >100     |  |

| Intel T20 | >100     | >100     | >100     |  |

#### Required Number of DFE Taps To Achieve 24dB SNR

#### Molex and Xilinx Backplanes

| BP       | NRZ      | DB       | PR4      |  |  |  |  |

|----------|----------|----------|----------|--|--|--|--|

|          | 3 tap FF | 4 tap FF | 5 tap FF |  |  |  |  |

| Molex i2 | 2        | 6        | 100      |  |  |  |  |

| Molex i3 | 2        | 8        | 100      |  |  |  |  |

| Molex i4 | 2        | 10       | 100      |  |  |  |  |

| Molex i5 | 2        | 6        | 100      |  |  |  |  |

| Molex o2 | <=1      | 4        | 100      |  |  |  |  |

| Molex o3 | <=1      | 5        | 100      |  |  |  |  |

| Molex o4 | <=1      | 4        | 100      |  |  |  |  |

| Molex o5 | <=1      | 3        | 100      |  |  |  |  |

| Anderson | 8        | 20       | >100     |  |  |  |  |

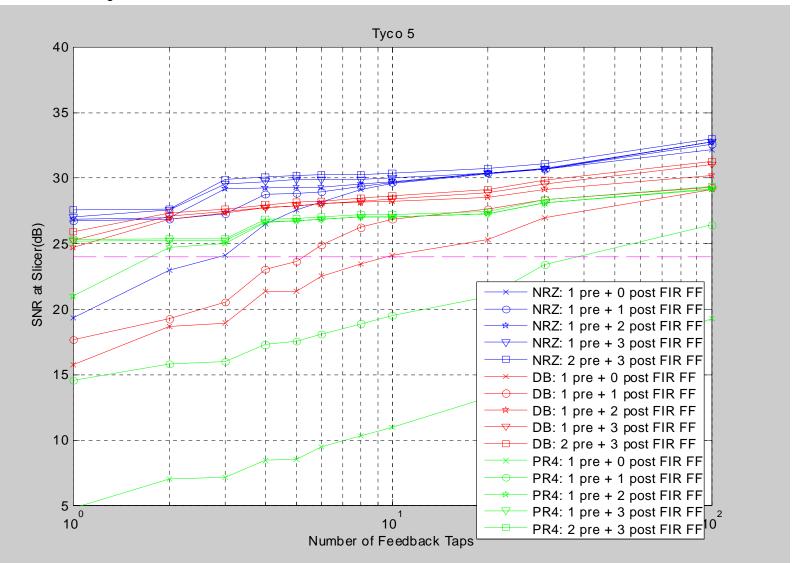

### Results Tyco 5 Backplane

LSI LOGIC

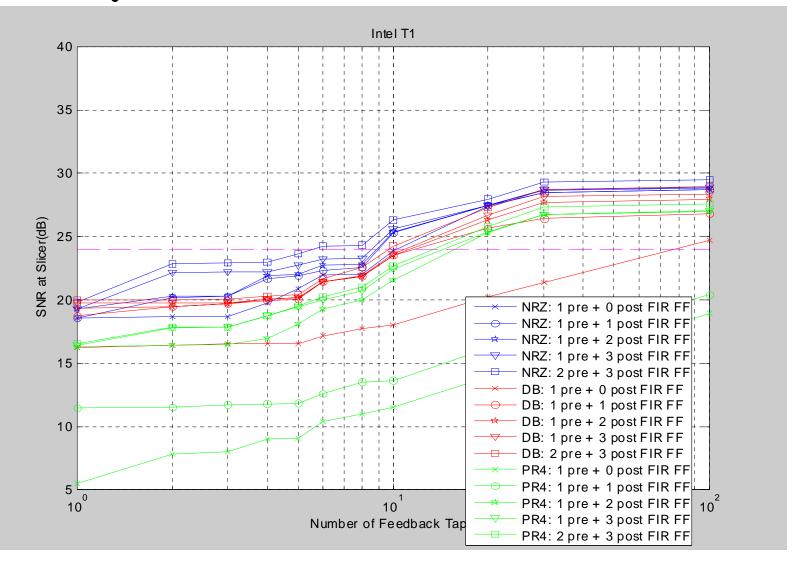

### Results Intel T1 Backplane

Conclusions NRZ, Duobinary, and PR4

- NRZ almost always outperformed Duobinary for similar equalization complexity.

- PR4 does not appear to be appropriate for this application.

- Intel T1 backplanes with large stubs are tremendously challenging to handle at these data rates.