## T10/02-045r0 Method to Reduce Driver/Receiver Asymmetry Induced Timing Errors

## SCSI Signal Path Tr/Tf Asymmetries

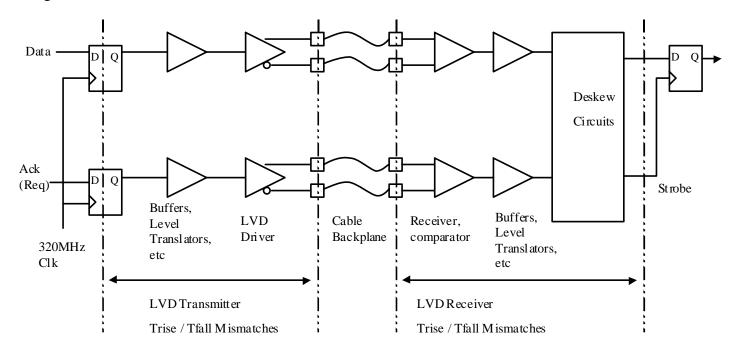

Typical Signal Path Block Diagram:

## LSI LOGIC

## T10/02-045r0 Method to Reduce Driver/Receiver Asymmetry Induced Timing Errors

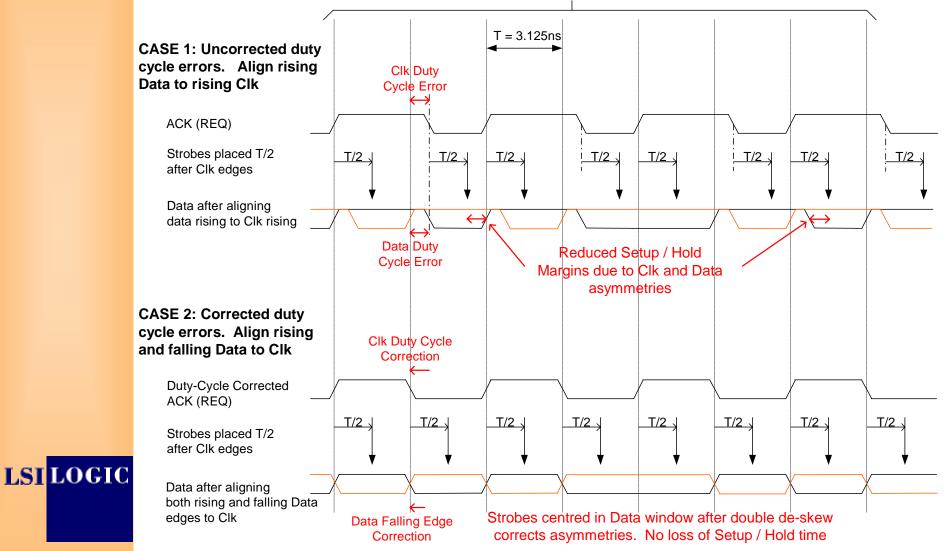

Ideal Cell Boundaries referenced to ACK (REQ) Rising Edge

T10/02-045r0

Method to Reduce Driver/Receiver Asymmetry Induced Timing Errors

Perform the following steps:

•Deskew asserting data edges to asserting clock edge.

•Deskew negating data edges to asserting clock edge.

Combine both deskewed signals to generate corrected data.Correct clock asymmetries.

•Use Corrected clock and set strobes to 1/2 of of bit period.

Possible budget improvement of 1000pS+ From SPI-4 Table 44

- •TX Asymmetry  $\pm 250$ pS

- •Receiver chip skew 750pS (Asymmetry portion only)