### **ULTRA320 TEST BOARD LICENSE**

LSI Logic Corporation ("LSI") is a member of the SCSI Passive Interconnect Performance Working Group of the T10 Technical Committee (the "PIP Working Group") having the goal of identifying a backplane test methodology that will be designated as a Backplane Testing Standard for the PIP Working Group, project 1439-D. LSI developed an Ultra320 Test Board and related documentation (the "Materials") identified in Exhibit A suitable for use in conducting backplane testing, and LSI desires to make the Materials available to other members of the PIP Working Group (the "Group Members") through a round robin exchange. Pursuant to the round robin exchange, each Group Member will have the opportunity to measure test parameters relative to the Ultra320 Test Board as determined by the PIP Working Group before transferring the Materials to the next Group Member participating in the round robin exchange, wherein the results of each Group Members' measuring activity will be provided to the PIP Working Group.

By accepting and using the Materials, the Group Members (each a "Licensee") agree that such use is subject to the terms and conditions of this Agreement. If Licensee does not wish to be subject to the terms and conditions contained herein, the Licensee should immediately forward the Materials to the next designated Group Member in the round robin exchange, or return the Materials to Larry Barnes at LSI Logic Corporation, 4420 ArrowsWest Dr, Colorado Springs, CO 80907.

#### **License Grant and Restrictions**

Subject to the terms and conditions herein, LSI grants to Licensee a nontransferable, nonexclusive, and revocable license under its intellectual property rights to use the Materials solely for the purpose of conducting measurements of test parameters as determined by the PIP Working Group.

Licensee agrees that any documentation, specifications, or other technical information generated from use of the Materials (the "Test Results") shall be used solely for presenting Licensee's measurement results to the PIP Working Group, and Licensee is expressly prohibited from using the Test Results for its own purposes to gain a competitive advantage over LSI or to disparage the goodwill and reputation of LSI or its products and technology.

Licensee agrees that the Material will not be reverse-engineered, merged, decompiled, disassembled, decoded or used in any manner not authorized by this Agreement, and further agrees not to remove or destroy any copyright notices, proprietary markings or confidential legends placed upon or contained within the Materials.

#### **Term and Termination**

The license granted herein shall commence upon the acceptance and first use of the Materials by the Licensee, and shall continue until Licensee transfers the Materials to the next Group Member in the round robin exchange or to LSI. LSI may terminate this Agreement at any time and for any reason. Upon termination or expiration of the license, Licensee shall immediately return to LSI, or destroy, all copies of the Materials made by Licensee to further its authorized measurement activities.

#### Ownership

LSI and its licensors, if any, shall retain sole right, title and ownership of the Materials and all intellectual property rights (including patents, copyrights, trade secrets, and invention disclosures) related to the Materials, including, but not limited to, any and all improvements, modifications, or derivatives thereof.

#### Confidentiality

Licensee shall hold in confidence the Materials as LSI's confidential information, and shall use the Materials only as expressly provided herein, and shall protect the confidentiality of such confidential information with the same degree of care as Licensee uses to protect its own confidential or proprietary information of great commercial value, but in no event shall Licensee use less than reasonable care. Licensee shall not make any such confidential information available in any form to any person other than to Licensee's engineering employees or subcontractors with a need to know for the purpose of conducting backplane testing relative to the Ultra320 Test Board. Licensee represents that it maintains (and agrees that it will maintain throughout the period that it retains any Materials) a reasonable system to protect confidential information, including, without limitation, written agreements with all of its employees and subcontractors containing prohibitions on their disclosure and the use of third party confidential information, which provisions are no less stringent than those

contained in this Agreement, and that the Materials will be protected under such system. Licensee agrees to notify LSI immediately of any suspected misuse or unauthorized disclosure of any Materials.

The obligations of confidentiality imposed on Licensee shall not apply or shall cease to apply to any information that Licensee clearly establishes: (i) was already rightfully in the possession of Licensee at the time of disclosure as evidenced by records of Licensee; (ii) is or becomes publicly available through no act or omission of Licensee; (iii) is rightfully received by Licensee from a third party without an obligation of confidentiality; (iv) is independently developed by Licensee's employees or contractors without use of or access to the information; or (v) is approved for unrestricted disclosure by written authorization of an authorized officer of LSI.

#### **Disclaimer of Warranty**

#### THE MATERIALS ARE FURNISHED TO THE LICENSEE "AS IS". ALL WARRANTIES, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING ANY IMPLIED WARRANTY OF MERCHANTABILITY, ANY IMPLIED WARRANTY OF FITNESS FOR A PARTICULAR PURPOSE, AND ANY IMPLIED WARRANTY AGAINST INFRINGEMENT, ARE HEREBY DISCLAIMED. NO SPECIFICATION OR OTHER DESCRIPTION, NO SAMPLE, NO PROTOTYPE AND NO DEMONSTRATION BOARD OR SYSTEM SHALL OPERATE AS A WARRANTY OF ANY KIND REGARDING ANY OF THE MATERIALS.

#### Damages

#### IN NO EVENT WILL LSI BE LIABLE FOR ANY SPECIAL, INDIRECT, PUNITIVE, INCIDENTAL, OR CONSEQUENTIAL DAMAGES (INCLUDING, WITHOUT LIMITATION, LOSS OF PROFITS) CAUSED BY ANY BREACH BY LSI OF ITS OBLIGATIONS ARISING OUT OF OR RELATING TO THIS AGREEMENT, REGARDLESS OF THE FORM OF ACTION, WHETHER IN CONTRACT OR IN TORT (INCLUDING NEGLIGENCE) EVEN IF LSI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THIS LIMITATION IS A MATERIAL CONDITION TO LSI ENTERING INTO THIS AGREEMENT.

#### General

<u>Limited Rights</u>. Nothing contained in this Agreement shall be construed as conferring by implication, estoppel, or otherwise any license or any other rights except as may otherwise be expressly set forth in this Agreement.

<u>Assignment</u>. Licensee shall not assign, sublicense or otherwise transfer any or all of its rights or privileges hereunder without the prior written consent of a vice president or higher level officer of LSI.

Export Compliance. Each party shall be responsible for complying with the laws and regulations of the U.S. Government relating to the export of goods and technology.

<u>Waiver</u>. No failure or delay on the part of either party in the exercise of any right or privilege hereunder shall operate as a waiver thereof or of the exercise of any other right or privilege hereunder, nor shall any single or partial exercise of any such right or privilege preclude other or further exercise thereof or of any other right or privilege.

<u>Governing Law</u>. This Agreement shall be governed by, and construed under, the laws (excluding its choice of law rules) of the State of California. The parties agree that any legal action to enforce or interpret this Agreement shall be brought in the courts of the State of California, or the Federal Court for the Northern District of California, and Licensee consents to personal jurisdiction of those courts for such purpose.

<u>Severability</u>. In the event that any provision of this Agreement is found by a court of competent jurisdiction to be invalid or void, then the remaining provisions of this Agreement shall remain in full force and effect as though such invalid or void provision were not contained in this Agreement.

<u>Integration</u>. This Agreement embodies the entire understanding of the parties as it relates to the subject matter hereof. This Agreement supersedes any prior agreements or understandings between the parties as to this subject matter. No amendment or modification of this Agreement shall be valid or binding upon the parties unless in writing and signed by an officer of each party.

### EXHIBIT A

### **DESIGNATED MATERIALS**

| Ultra320 Test Board | l:                                                              |

|---------------------|-----------------------------------------------------------------|

|                     | G12 Ultra-4 SCSI Buffer test board. Part number 001003-1        |

| or                  | G12 Ultra-4 SCSI Buffer test board. Part number 001003-2        |

|                     |                                                                 |

|                     |                                                                 |

|                     |                                                                 |

|                     |                                                                 |

|                     |                                                                 |

| Documentation:      |                                                                 |

|                     | SCSI Ultra-4, test PCB. General description (8 pages) Attached. |

|                     | Schematic diagrams. (5 pages)                                   |

|                     |                                                                 |

|                     |                                                                 |

|                     |                                                                 |

|                     |                                                                 |

# SCSI Ultra-4, test PCB. General description.

### **<u>1. Introduction</u>**

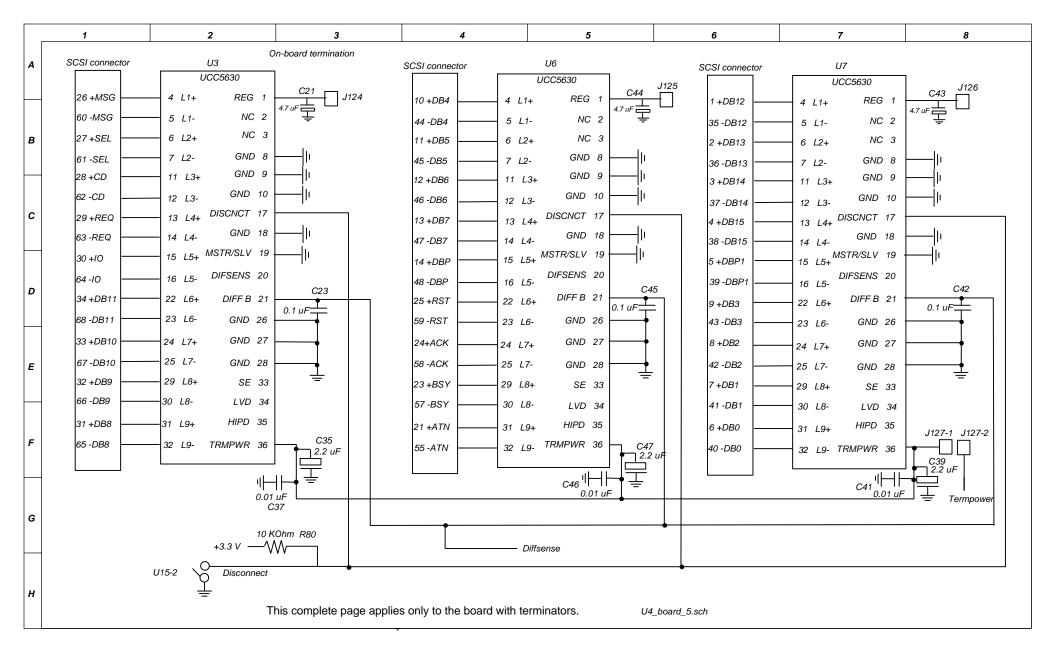

There are two board types. The only difference between the two is that one has "on-board" SCSI multimode terminators, while the other board does not. In this way, the SCSI interface implementation bears more resemblance to a "Hard drive" (with no on-board terminators) and a "Host Adapter" (which typically has on-board terminators).

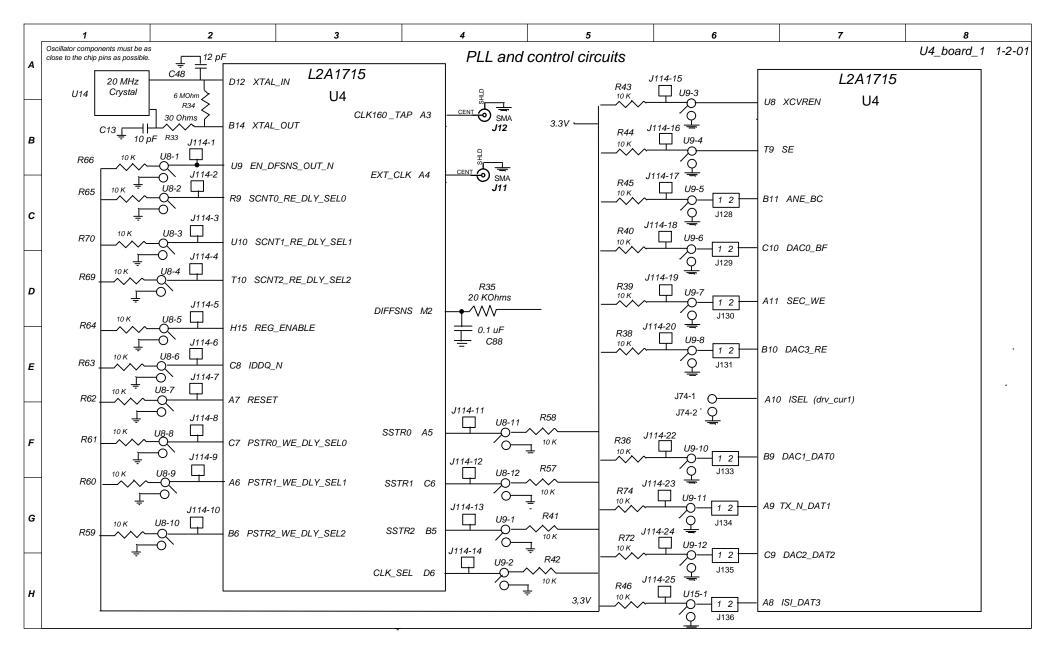

The boards are designed as a test vehicle for the L2B1715 SCSI Ultra-4 transceivers, which are implemented in LSI Logic G12P<sup>TM</sup> technology. The Round Robin test board has "on-board" SCSI miltimode terminators.

### 2. Board features.

Numerous switches and jumpers on the board are used to control the various functions of the chip and PCB. The detailed list of switches an jumpers are appended to the end of this document.

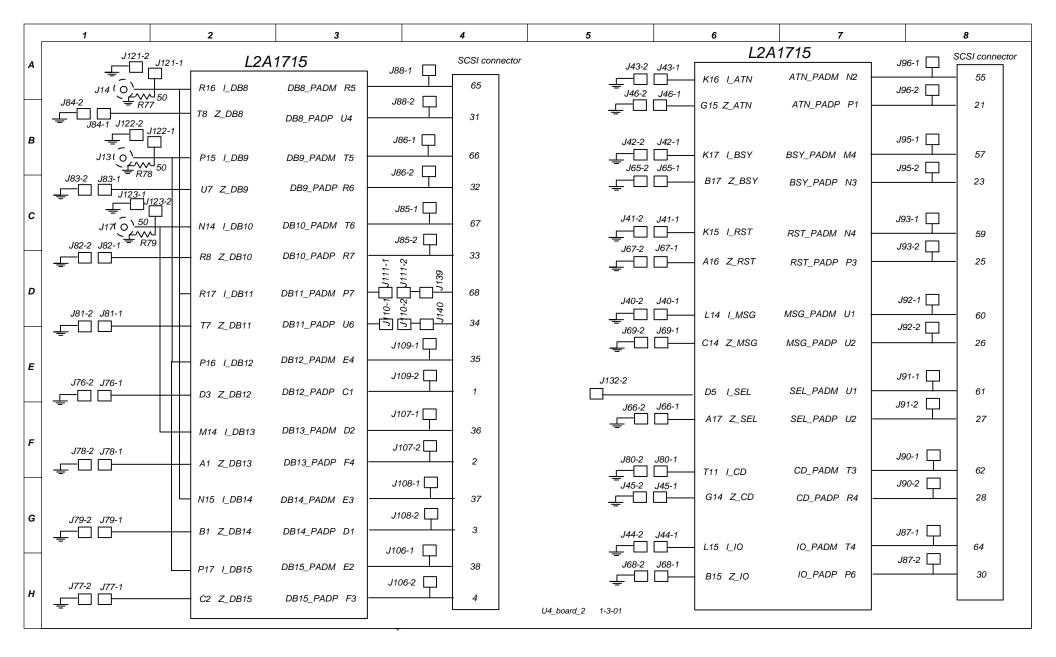

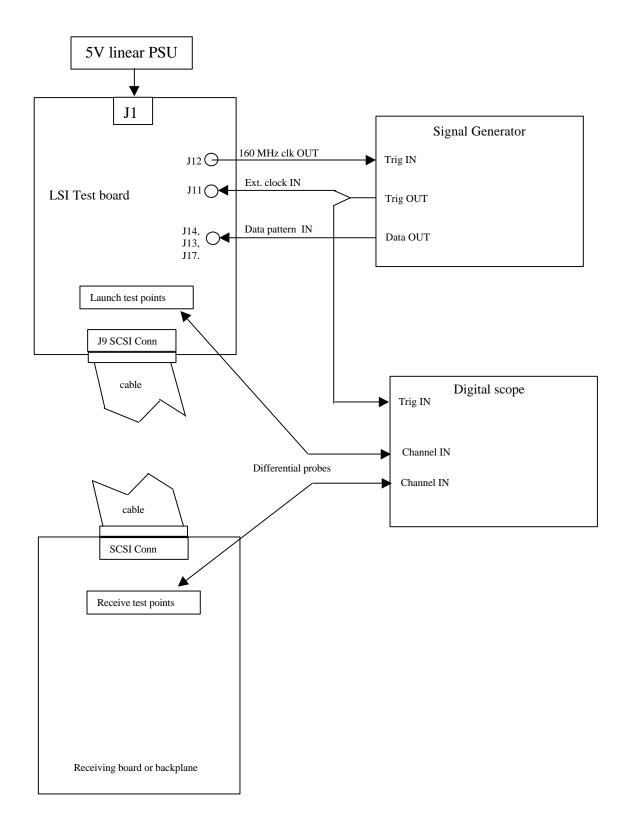

The twenty seven SCSI buffer I/O's on the chip are brought out to a 68 pin high density SCSI connector to enable connection to cable media etc. Test points are provided near the SCSI connector to be able to observe each of the differential signal pairs.

The buffers are divided into three groups. Certain SCSI control signals do not need to employ pre-emphasis and are less sophisticated in the way they are internally connected. These are RST, ATN, BSY, MSG, SEL, C/D, I/O.

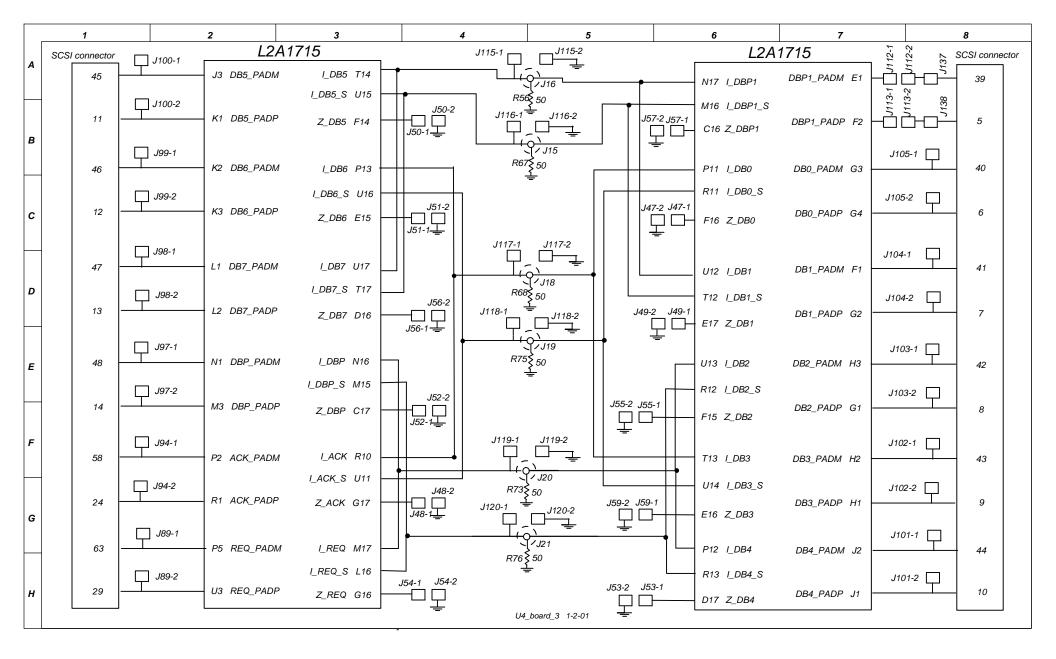

The rest of the SCSI bus signals are the ones which may be driven in pre-emphasis mode, hence there is a Primary and a Secondary input signal to the buffers.

For this group DB0, DB1, DB2, DB3, DB4, DB5, DB6, DB7, DBP, DBP1, REQ and ACK, the Primary data signals are applied to their respective inputs I\_xxx and Secondary data signals are applied to their inputs I\_xxx\_S.

The Primary signal is the data that the "Customer" wishes to transmit. The Secondary signal is the suitably encoded signal which modifies the primary in order to accomplish the pre-emphasis modulation.

An internal encoder is employed for the following buffers. DB8, DB9, D10, DB11, DB12, DB13, DB14 and DB15. For these buffers the "Customer" input data applied to J13, J14 and J17 is encoded automatically. This is much simpler to use because any data pattern can be inserted without having to encode an external input for the Secondary driver.

There are two ways to transmit the data to the SCSI buffers. Synchronous mode or Asynchronous mode. This function is controlled by J74. In Asynchronous mode, the data from the internal core of the chip goes straight out through the buffer without any type of synchronization.

When the SCSI buffers are selected to operate in Synchronous mode The data is latched internally and synchronized by a clock.

There are two ways to do this. Firstly the "internal" method is where the 160 MHz clock from the "onchip" PLL circuit. CLK\_SEL (U9-2) is switched ON. Alternatively, with U9-2 switched OFF, an external clock source is supplied to J11. Remember that the maximum data frequency is 80 MHz. The clock needs to be 160 MHz. (Always twice the data frequency.)

Primary data input signals to the SCSI buffer are labeled as I\_xxx. (e.g. I\_REQ) Secondary data input signals are labeled as I\_xxx\_S. (e.g. (I\_REQ\_S) The differential bi-direct output pins are labeled as xxx\_PADM and xxx\_PADP. The Receiver output signals are labeled as Z\_xxx. Refer to the schematic diagram for the test points and connectors to gain access to these signals.

The LVD and SE drivers have 8 programmable levels of slew rate control. These are set by switches U8-2, U8-3 and U8-4.

The LVD driver has programmable drive strength. The Primary driver circuit has 8 programmable settings controlled by U8-8, U8-9 and U8-10. The Secondary driver circuit also has 8 settings controlled by U8-11, U8-12 and U9-1. These combinations provide a total of 64 different drive strengths each for "Standard" mode and for "Pre-emphasis" mode.

(Pre-emphasis mode is where drive strength is "cutback" after 1 clock period if there has not been a signal transition.)

5 Volt termpower can be provided to the SCSI connector, depending on the jumper configuration of J5.

For the board which has "on-board" SCSI multi-mode terminators, U15-2 is used to electrically enable/disable the terminator circuits.

### 3. Electrical/Power Requirements

One external regulated power supply at 5 VDC. (> 2 Amps) is used to provide primary power to the board. A "LINEAR" power supply is much preferred over a "SWITCHING" type of supply.

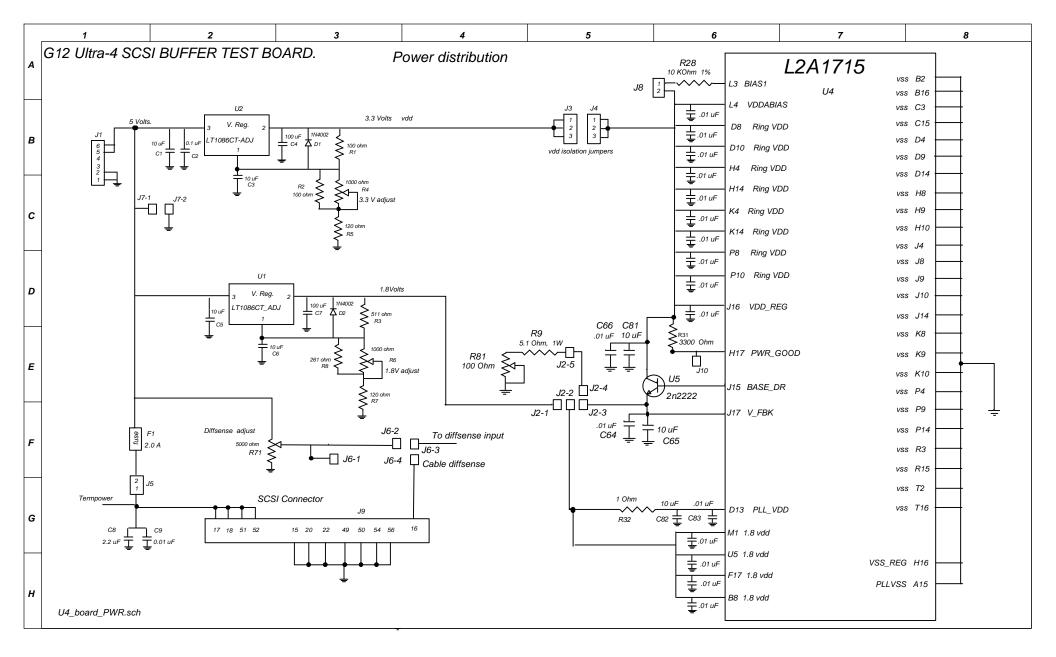

The PC board has regulators to provide 3.3VDC and 1.8 VDC to the chip and test circuits.

## 4. Quick reference Switch and Jumper settings.

|        | Switch settings for Transmit / Receive |          |          |          |                                              |

|--------|----------------------------------------|----------|----------|----------|----------------------------------------------|

| Switch | LVD                                    | SE       | LVD      | SE       |                                              |

|        | transmit                               | transmit | Receive  | Receive  |                                              |

| U8-1   | OFF                                    | OFF      | OFF      | OFF      |                                              |

| U8-2   | OFF                                    | OFF      | OFF (NA) | OFF (NA) |                                              |

| U8-3   | OFF                                    | OFF      | OFF (NA) | OFF (NA) | Slew rate control switches.                  |

| U8-4   | OFF                                    | OFF      | OFF (NA) | OFF (NA) |                                              |

| U8-5   | ON                                     | ON       | ON       | ON       |                                              |

| U8-6   | ON                                     | ON       | ON       | ON       |                                              |

| U8-7   | ON                                     | ON       | ON       | ON       | Reset chip by switching OFF then ON again.   |

| U8-8   | OFF                                    | OFF (NA) | OFF (NA) | OFF (NA) |                                              |

| U8-9   | ON                                     | OFF (NA) | OFF (NA) | OFF (NA) | LVD Primary driver strength settings.        |

| U8-10  | ON                                     | OFF (NA) | OFF (NA) | OFF (NA) |                                              |

| U8-11  | OFF                                    | OFF (NA) | OFF (NA) | OFF (NA) |                                              |

| U8-12  | OFF                                    | OFF (NA) | OFF (NA) | OFF (NA) | LVD Secondary driver strength settings.      |

| U9-1   | OFF                                    | OFF (NA) | OFF (NA) | OFF (NA) | 7                                            |

| U9-2   | ON                                     | ON       | ON (NA)  | ON (NA)  | Internal / External clock select.            |

| U9-3   | OFF                                    | OFF      | OFF      | OFF      |                                              |

| U9-4   | ON                                     | OFF      | ON       | OFF      | LVD / SE mode select                         |

| U9-5   | OFF (NA)                               | OFF      | OFF (NA) | OFF (NA) | Active negation switch (SE only)             |

| U9-6   | OFF (NA)                               | OFF (NA) | OFF (NA) | OFF (NA) |                                              |

| U9-7   | OFF                                    | OFF (NA) | OFF (NA) | OFF (NA) |                                              |

| U9-8   | OFF (NA)                               | OFF (NA) | OFF (NA) | OFF (NA) |                                              |

| J74-1  | to J74-2                               | to J74-2 | (NA)     | (NA)     | Synchronous mode select.                     |

| U9-10  | OFF (NA)                               | OFF (NA) | OFF (NA) | OFF (NA) |                                              |

| U9-11  | ON                                     | ON       | OFF      | OFF      | Transmitter enable switch                    |

| U9-12  | OFF (NA)                               | OFF (NA) | OFF (NA) | OFF (NA) |                                              |

| U15-1  | ON                                     | ON (NA)  | ON (NA)  | ON (NA)  | LVD Precomp. enable switch                   |

| U15-2  | ON                                     | ON       | ON       | ON       | Enable on-board terminators. (If applicable) |

$^{(N\!/\!A)}$  means switch does nothing in this mode.

Default Jumper settings.

| Jumper | Jumper | Function                                                |

|--------|--------|---------------------------------------------------------|

| From   | То     |                                                         |

| J2-1   | J2-2   | 1.8V power                                              |

| J3-1   | J4-1   | 3.3V power                                              |

| J3-2   | J4-2   | 3.3V power                                              |

| J5-1   | J5-2   | 5V "Termpower" to SCSI connector.                       |

| J6-2   | J6-4   | Supply variable voltage source to cable diffsense line. |

| J8-1   | J8-2   | Voltage supply to Bias resistor.                        |

| J110-1 | J110-2 |                                                         |

| J111-1 | J111-2 |                                                         |

| J112-1 | J112-2 | SCSI output breakpoints                                 |

| J113-1 | J113-2 |                                                         |

| J127-1 | J127-2 | Provide 5V power to Terminator resistors.               |

### 5. Configuration for cable / back-plane signal testing.

Typical and simplest configuration.

# Programmable settings.

LVD Driver Slew rate control.

| Slew r | ate contr |      |                         |

|--------|-----------|------|-------------------------|

| U8-4   | U8-3      | U8-2 | Nominal Rise/Fall<br>ns |

| ON     | ON        | ON   | 3.0                     |

| ON     | ON        | OFF  | 2.33                    |

| ON     | OFF       | ON   | 1.91                    |

| ON     | OFF       | OFF  | 1.61                    |

| OFF    | ON        | ON   | 1.40                    |

| OFF    | ON        | OFF  | 1.23                    |

| OFF    | OFF       | ON   | 1.10                    |

| OFF    | OFF       | OFF  | 1.0                     |

Slew rate control. (Single Ended driver).

| Slew rate control bits. |      |      |                                |

|-------------------------|------|------|--------------------------------|

|                         |      |      | Slew rate mV/ns (nom).         |

| U8-4                    | U8-3 | U8-2 | Measured between 0.7V and 2.3V |

| ON                      | ON   | ON   | 220                            |

| ON                      | ON   | OFF  | 240                            |

| ON                      | OFF  | ON   | 260                            |

| ON                      | OFF  | OFF  | 280                            |

| OFF                     | ON   | ON   | 300                            |

| OFF                     | ON   | OFF  | 320                            |

| OFF                     | OFF  | ON   | 340                            |

| OFF                     | OFF  | OFF  | 360                            |

## LVD Driver strengh

The LVD Drive current strength is made up of 3 factors. First the Primary current. Then the Secondary current is added or subtracted to the primary. (Depending on whether Pre-emphasis is Enabled or Disabled). Then a constant 2mA bias current is applied. (Terminator bias cancellation.)

Therefore the calculations for final currents are:

<u>No CUTBACK</u> Assertion current = Primary current + Secondary current + 2 mA Negation current = Primary current + Secondary current - 2 mA

<u>With CUTBACK</u> Assertion current = Primary current - Secondary current + 2 mA Negation current = Primary current - Secondary current - 2 mA

The LVD Primary driver current has eight programmable settings as determined by the switch settings as shown in this table.

| SP0  | SP1  | SP2   | Primary  |

|------|------|-------|----------|

| U8-8 | U8-9 | U8-10 | Drive mA |

| ON   | ON   | ON    | 6.75     |

| ON   | ON   | OFF   | 7.50     |

| ON   | OFF  | ON    | 8.25     |

| ON   | OFF  | OFF   | 9.00     |

| OFF  | ON   | ON    | 9.75     |

| OFF  | ON   | OFF   | 10.50    |

| OFF  | OFF  | ON    | 11.25    |

| OFF  | OFF  | OFF   | 12.00    |

The Secondary driver will add/subtract by the percentages shown in this table.

| SS0   | SS1   | SS2  | Secondary   |

|-------|-------|------|-------------|

| U8-11 | U8-12 | U9-1 | Driver      |

| ON    | ON    | ON   | +/- 4.17 %  |

| ON    | ON    | OFF  | +/- 8.33 %  |

| ON    | OFF   | ON   | +/- 12.5 %  |

| ON    | OFF   | OFF  | +/- 16.67 % |

| OFF   | ON    | ON   | +/- 20.83 % |

| OFF   | ON    | OFF  | +/- 25.00 % |

| OFF   | OFF   | ON   | +/- 29.17 % |

| OFF   | OFF   | OFF  | +/- 33.33 % |

| Switch | Signal                          | Function                                                                        | Effect                                                              |

|--------|---------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------|

| U8-1   | EN_DFSNS_OUT_N                  | Diffsense Receiver control                                                      | ON = Low = Enable<br>OFF = High = Disable                           |

| U8-2   | SCNT0_RE_DLY_SEL0               | Slew rate control LSD                                                           | ON = Low<br>OFF = High                                              |

| U8-3   | SCNT1_RE_DLY_SEL1               | Slew rate control                                                               | ON = Low<br>OFF = High                                              |

| U8-4   | SCNT2_RE_DLY_SEL2               | Slew rate control MSD                                                           | ON = Low<br>OFF = High                                              |

| U8-5   | REG_ENABLE<br>and Miscellaneous | Voltage Regulator control<br>Needs to be ON to permit input<br>signals ANE etc. | ON = Low = Enable<br>OFF = High = Disable                           |

| U8-6   | IDDQ_N                          | Controls High-Z leakage test function for entire chip                           | ON = Low = Disable leakage test<br>OFF = High = Enable leakage test |

| U8-7   | RESET                           | Reset for entire chip                                                           | ON = Low = Disable RESET<br>OFF = High = Enable RESET               |

| U8-8   | PSTR0_WE_DLY_SEL0               | Primary Drive strength. LSD                                                     | ON = Low<br>OFF = High                                              |

| U8-9   | PSTR1_WE_DLY_SEL1               | Primary Drive strength. LSD                                                     | ON = Low<br>OFF = High                                              |

| U8-10  | PSTR2_WE_DLY_SEL2               | Primary Drive strength. MSD                                                     | ON = Low<br>OFF = High                                              |

| U8-11  | SSTR0                           | Secondary drive strength LSD.                                                   | ON = Low<br>OFF = High                                              |

| U8-12  | SSTR1                           | Secondary drive strength                                                        | ON = Low<br>OFF = High                                              |

# Jumper and switch functions. (more details)

| U9-1  | SSTR2   | Secondary drive strength. MSD | ON = Low                        |

|-------|---------|-------------------------------|---------------------------------|

|       |         |                               | OFF = High                      |

| U9-2  | CLK_SEL | Clock select switch.          | ON = Internal 160 MHz clk       |

|       |         |                               | OFF = External clk.             |

| U9-3  | XCVREN  | Transceiver enable            | ON = Low = Disable transceiver  |

|       |         |                               | OFF = High = Enable transceiver |

| U9-4  | SE      | Mode control for SE and LVD   | ON = Low = LVD                  |

|       |         |                               | OFF = High = SE.                |

| U9-5  | ANE_BC  | Active Negation Enable        | ON = Low = Disable Active neg.  |

|       |         |                               | OFF = High = Enable Active neg. |

| U9-6  | DAC0_BF | DAC0 for Voltage Regulator    | ON = Low                        |

|       |         | BF for Register file.         | OFF = High                      |

| U9-7  | SEC_WE  | Secondary driver disable      | ON = Low = Disable secondary Dr |

|       |         |                               | OFF =High = Enable secondary Dr |

| U9-8  | DAC3_RE | DAC3 for Voltage Regulator    | ON = Low                        |

|       |         | RE for Register file          | OFF = High                      |

| J74-1 | ISEL    | Select Synch or Asynch. mode. | J74-1 jumper to $J74-2 = Low =$ |

|       |         |                               | Synchronous mode                |

|       |         |                               | J74-1 open = Asynchronous mode  |

| U9-10 | DAC1_DAT0               | DAC1 for Voltage Regulator    | ON = Low                      |

|-------|-------------------------|-------------------------------|-------------------------------|

|       |                         | DAT0 for Register file        | OFF = High                    |

| U9-11 | TX_N_DAT1               | Transmit enable               | ON = Low = Enable transmit    |

|       |                         |                               | OFF = High = Disable transmit |

| U9-12 | DAC2_DAT2               | DAC2 for Voltage Regulator    | ON = Low                      |

|       |                         | DAT2 for Register file        | OFF = High                    |

| U15-1 | ISI_DAT3                | Pre-compensation enable.      | ON = Low = Disable Pre-comp   |

|       |                         | _                             | OFF = High = Enable Pre-comp. |

| U15-2 | Disconnect              | Control on-board terminators. | ON = Low = Enable Term.       |

|       | (Terminator board only) |                               | OFF = High = Disable Term.    |

| Jumper              | Signal            | Function/Effect                                    |

|---------------------|-------------------|----------------------------------------------------|

| J1                  | 5 Volt            | Main power connector.                              |

| J2-1,2,3,4,5        | 1.8V power        | See Schematic                                      |

| J3, J4              | 3.3V power        | Short to connect power to chip                     |

| J5-1,2              | 5 Volt power      | Short to supply "Termpower" to SCSI connector      |

|                     |                   | and resistor chips                                 |

| J6-1,2,3,4          | Variable V source | See Schematic                                      |

| J7-1, J7-2          | 5V and 0V         | Test point for 5V. DO NOT SHORT                    |

| J8                  | BIAS1             | Short to enable voltage supply to Bias resistor.   |

| J9                  | SCSI              | SCSI bus connector                                 |

| J10                 | PWR_GOOD          | Test point for Voltage regulator                   |

| J110, 111, 112, 113 | SCSI outputs      | See Schematic                                      |

| J114-n              | Test points       | See Schematic                                      |

| J127-1, 2           |                   | Short to provide 5V power to Terminator resistors. |

| All others          | Test points       | See Schematic                                      |

SCSI\_Ultra\_4\_testboard.doc.